Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении высоконадежных резервированных систем передачи-приема информации в последовательных кодах.

Целью изобретения является повы- шение достоверности контроля резервированного устройства.

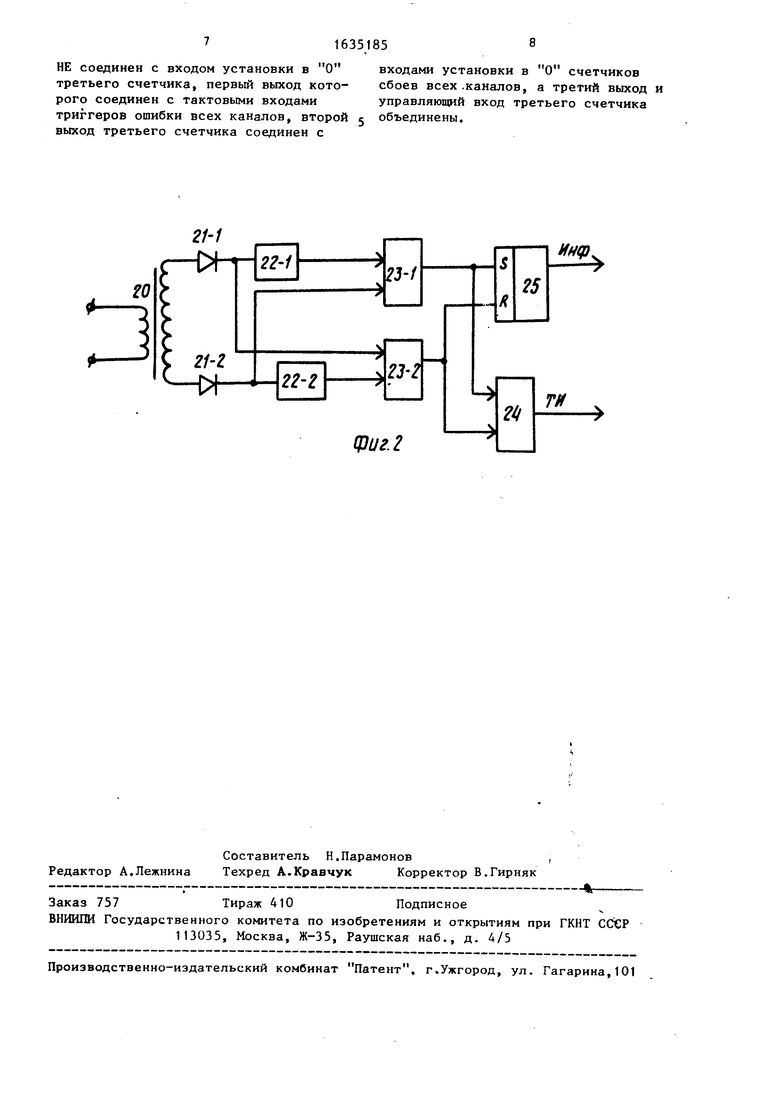

На фиг. 1 приведена схема предлагаемого устройства, на фиг. 2 - схема резервируемого блока.

Устройство содержит блок 1 индикации, триггеры 2 ошибки, элемент НЕ 3, счетчик 4, дешифраторы 5 ошибки, счетчики 6 сбоев, интеграторы 7, схемы 8 сравнения, резервируемые блоки 9, дешифратор 10, сдвигающий регистр 11, мажоритарные элементы 12 и 13, дешифратор 14, счетчик 15, элементы ИЛИ 16, И 17, счетчик 18 и генератор 19 импульсов.

Резервируемый блок 9 включает трансформатор 20, диоды 21, элементы задержки 22, И 23, ИЛИ 24 и триггер 25.

Устройство работает следующим образом.

Резервируемые блоки 9 обеспечивают прием информации в последовательных кодах, при этом биты информации на входах блока 9 представляются двухполярными импульсами, а на выходах блока формируются сигналы О и 1, соответствующие этим битам, и для каждого бита тактовый импульс сопровождения. Информация на входах и выходах блоков 9 представлена в виде кодограмм, причем признаком начала кодограммы является маркер, ко которого накапливается в сдвигающем регистре 11 и декодируется дешифра- тором Ю. Все кодограммы содержат одинаковое число бит, которое подсчитывается в счетчике 15 и декодируется дешифратором 14. В исходном положении все триггеры и счетчики устройства обнулены (цепи начальной установки не показаны). При исправности всех блоков 9 биты информации на их информационных выходах идентичны и совпада

,

5

0

5 0

« , п

5

5

ют со значением информации на выходе мажоритарного элемента 12. С выхода мажоритарного элемента 12 биты информации поступают на выход устройства И на информационный вход сдвигающего регистра 11. Сравнение бит информации каждого блока 9 с информацией мажоритарного элемента 12 производится соответствующей схемой 8 сравнения, на выходе которой при равенстве входных сигналов сигнал не формируется. Из-за задержек мажоритарного элемента 12 сигналы сравнения на входах схемы 8 сравнения могут быть сдвинуты во времени друг относительно друга, возникающие при этом на выходах схем 8 ложные сигналы несравнения устраняются интеграторами 7. Для каждого бита информации блоки 9 формируют на своих тактовых выходах импульсы сопровождения, которые подаются на мажоритарный элемент 13. При исправности всех блоков 9 импульсы с выхода элемента 13 периодически устанавливают в нулевое положение счетчик 18 и через элемент ИЛИ 17 поступают на тактовый вход счетчика 15 и сдвиговый вход регистра 11. В регистре 11 накапливается код маркера - признака начала кодограммы, который декодируется дешифратором Ю. Сигнал маркера с выхода дешифратора 10 устанавливает в нулевое положение счетчик 15, который после этого начинает считать число бит поступающей на блоки 9 кодограммы. После приема последнего бита кодограммы на выходе дешифратора 14 формируется сигнал, который через элемент НЕ 3 снимает сигнал обнуления с нулевого входа счетчика 4. Счетчик 4 заполняется тактовыми импульсами, причем сигнал с его первого выхода подается на тактовые входы триггеров 2, устанавливая их в положения, определяемые сигналами на их информационных входах. Сигнал с его второго выхода обнуляет счетчики 6 сбоев, а сигнал с третьего выхода подается на его управляющий вход и запрещает счет. При поступлении следующего бита следующей кодограммы

снимается сигнал на выходе дешифратора 14 и через элемент НЕ 3 счетчик 4 снова устанавливается в нулевое положение. При неисправности какого- либо из блоков 9, например блока 9-1 биты информации на входах схемы 8-1 сравнения не совпадают и схема 8-1 формирует единичный сигнал, который подается на-счетный вход счетчика 6-1. Счетчики 6 накапливают число сбоев в поступающей кодограмме. При числе сбоев, равном заданному, на выходе соответствующего дешифратора 5-1 формируется сигнал, который подается на информационный вход соответствующего триггера 2-1 и на управляющий вход счетчика 6-1, запрещая дальнейший счет сбоев в данном канале. По окончании приема кодограммы сигнал с выхода дешифратора 14 снова включает счетчик 4 и сигнал ошибки с выхода дешифратора 5-1 устанавливает триггер 2-1 в единичное состояние. Соответствующий сигнал с триггера 2-1 поступает в блок 1 индикации .

В случае отключения всех каналов резервирования блоков 9, например при отключении питания или при отсутствии информации блоков 9, на выхода мажоритарных элементов 12 и 13 сиг- напы также отсутствуют. При этом снимаются сигналы периодического обнуления с нулевого входа счетчика 18, который заполняется тактовыми импульсами генератора 19 до порогового значения. Сигнал с выхода счетчика 18 подается на его управляющий вход, запрещая дальнейший счет, подготавливает к открыванию элемент И 17 и выдается на блок 1 индикации в виде сигнала Информация отсутствует. Тактовые импульсы генератора 19 через элементы И 17, ИЛИ 16 заполняют счетчик 15, который совместно с дешифратором 14 формирует периодически сигналы, запускающие счетчик 4. При этом триггеры 2 и счетчики 6 сбоев также периодически обнуляются до поступления информации с блоков 9.

Формула изобретения

Резервированное устройство, содержащее первый мажоритарный элемент блок индикации, элементы ИЛИ и три канала контроля, каждый из которых содержит триггер ошибки, резервируе5

0

5

0

5

0

5

0

5

мый блок, схему сравнения, причем информационные выходы резервируемых блоков всех каналов соединены с входами первого мажоритарного элемента, выход которого является информационным выходом устройства и подключен к первым входам схем сравнения каждого канала, а в каждом канале информационный выход резервируемого блока соединен г вторым входом схемы сравнения, а выход триггера ошибки подключен к соответствующему входу блока индикации, отличающее- с я., тем, что, с целью повышения достоверности контроля, в него введены генератор импульсов, второй мажоритарный элемент, элемент НЕ, сдвигающий регистр, последовательно соединенный с первым дешифратором, первый счетчик, второй счетчик, последовательно соединенный с вторым дешифратором, третий счетчик, а в каждый канал контроля введены интегратор, последовательно включенные счетчик сбоев и дешифратор ошибки, причем в каждом канале выход схемы сравнения соединен с входом интегратора, выход которого подключен к синхровходу счетчика сбоев, выход дешифратора ошибки соединен с управляющим входом счетчика сбоев и информационным входом триггера ошибки данного канала, тактовые выходы резервируемых блоков трех каналов соединены с соответствующими входами второго мажоритарного элемента, выход которого соединен с тактовым выходом устройства, первым входом элемента ИЛИ и входом установки в О первого счетчика, тактовый вход которого соединен с выходом генератора импульсов, соединенного также с тактовым входом третьего счетчика и первым входом элемента И, второй вход которого соединен с управляющим входом и выходом первого счетчика и соответствующим входом блока индикации, выход элемента И соединен с вторым входом элемента ИЛИ, выход которого подключен к тактовому входу второго счетчика и сдвиговому входу сдвигающего регистра, информационный вход которого соединен с выходом первого мажоритарного элемента, выход первого дешифратора соединен с| входом установки в О второго счетчика, информационный выход которого подключен к входу второго дешифратора, выход которого через элемент

НЕ соединен с входом установки в О третьего счетчика, первый выход которого соединен с тактовыми входами триггеров ошибки всех каналов, второй выход третьего счетчика соединен с

объединены,

входами установки в О счетчиков сбоев всех .каналов, а третий выход и управляющий вход третьего счетчика

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для индикации | 1989 |

|

SU1686474A1 |

| Устройство для приема информации | 1988 |

|

SU1552216A1 |

| Устройство для приема информации | 1986 |

|

SU1336074A1 |

| Устройство для фиксации сбоев | 1987 |

|

SU1462320A1 |

| Устройство для обработки информации | 1990 |

|

SU1758649A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Устройство для оперативной реконфигурации резервированной системы | 1990 |

|

SU1727125A1 |

| Резервированное устройство | 1989 |

|

SU1605236A1 |

| Резервированная система | 1982 |

|

SU1089771A1 |

| Устройство для приема информации | 1988 |

|

SU1562950A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении высоконадежных резервированных систем передачи и приема информации в последовательных кодах. Цель изобретения - повышение достоверности контроля информации. Информация в последовательных кодах с выходов резервируемых блоков 9 сравнивается с результирующей информацией мажоритарного элемента 12 с помощью схем 8 сравнения. Сигналы ошибки с выходов схем 8 сравнения через интеграторы 7 накапливаются в счетчиках 6 сбоев, состояния которых декодируются дешифраторами 5 ошибки, и записываются в триггер 2 ошибки. Тактовые импульсы сопровождения информации через мажоритарный элемент 13 управляют счетчиком

Фиг. 2

| Мажоритарно-резервированное устройство | 1983 |

|

SU1156077A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для мажоритарного выбора сигналов | 1983 |

|

SU1092512A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-03-15—Публикация

1989-04-18—Подача