ыц,

ел ел to

со ел ел

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой согласованный фильтр | 1988 |

|

SU1596267A1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1992 |

|

RU2042269C1 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1990 |

|

SU1795475A1 |

| УСТРОЙСТВО ВЫСОКОСКОРОСТНОГО РАДИОПРИЕМА БЛОКА ЧИСЕЛ | 2010 |

|

RU2419967C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЧАСТОТЫ И РАЗНОСТИ ЧАСТОТ СИГНАЛОВ | 1992 |

|

RU2025738C1 |

| НЕКОГЕРЕНТНЫЙ ОБНАРУЖИТЕЛЬ СИГНАЛОВ В ШУМАХ | 2000 |

|

RU2199762C2 |

| СПОСОБ ПРИЕМА ШИРОКОПОЛОСНОГО СИГНАЛА И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ (ВАРИАНТЫ) | 1999 |

|

RU2153770C1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1984 |

|

SU1840075A1 |

| НЕКОГЕРЕНТНЫЙ ОБНАРУЖИТЕЛЬ РАДИОСИГНАЛОВ В ШУМАХ | 2000 |

|

RU2187198C2 |

Изобретение относится к радиолокационной технике. Цель изобретения - повышение быстродействия при одновременном упрощении фильтра. Фильтр содержит компаратор 1, формирователь 2 кода фаз, блок памяти 3 входных отсчетов, блок управления 4, блок памяти 5 коэффициентов, сумматор 6,формирователь 7 квадратурных сигналов и накапливающий сумматор 8. Входной сигнал сравнивается в компараторе 1 с нулевым уровнем. Из полученного бинарного сигнала формирователь 2 вырабатывает сигнал, представленный набором разрядных кодов фазы. Этот сигнал записывается в блок памяти 3. Полученные двоичные коды фаз входного сигнала поступают на сумматор 6, а результаты сложения - на формирователь 7, вычисляющий поочередно SIN-ную и COS-ную составляющие, которые затем поступают на сумматор 8. Он, осуществляя операцию наакопления квадратурных составляющих, производит вычисление модуля и фазы входного сигнала. Цель достигается путем замены операции умножения двух комплексных чисел простейшей операцией сложения двух разрядных чисел, быстродействие которой определяется только быстродействием сумматора 6. 3 ил.

фие. 1

Изобретение относится к радиолокационной технике и может быть использовано для оптимальной обработки ЧМ- сигналов .

Цель изобретения - повышение быстродействия при одновременном упрощении цифрового согласованного Липьтра ЧМ-с иг на лов .

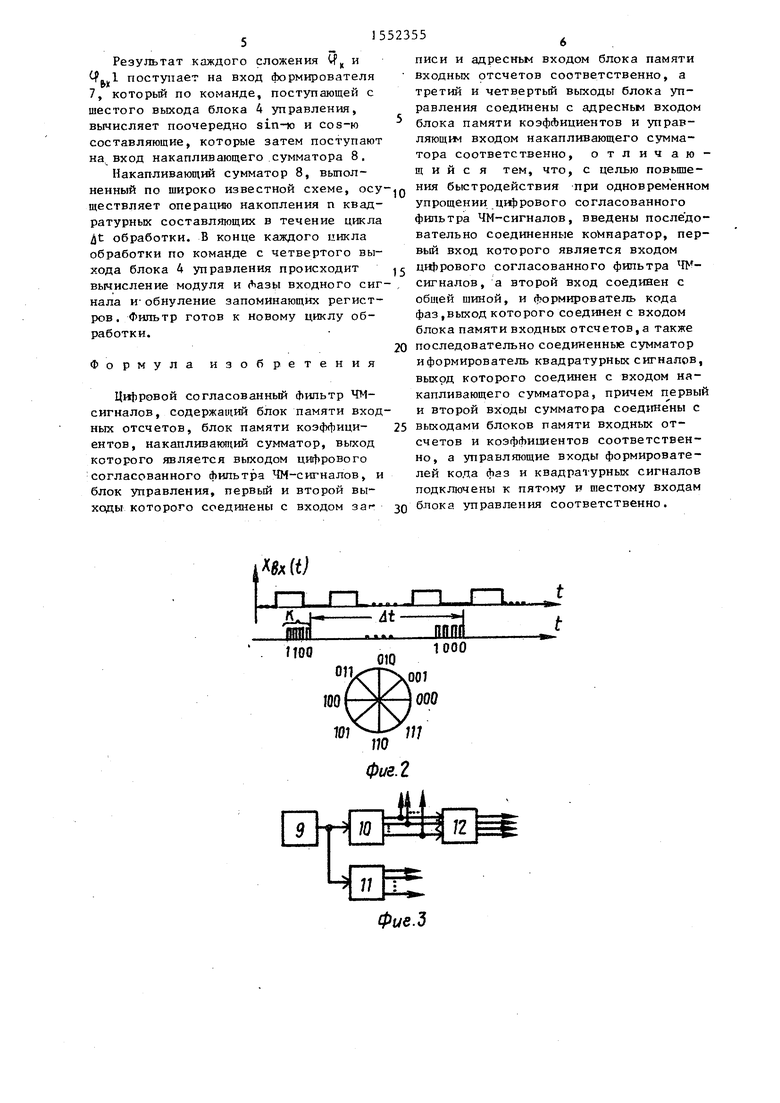

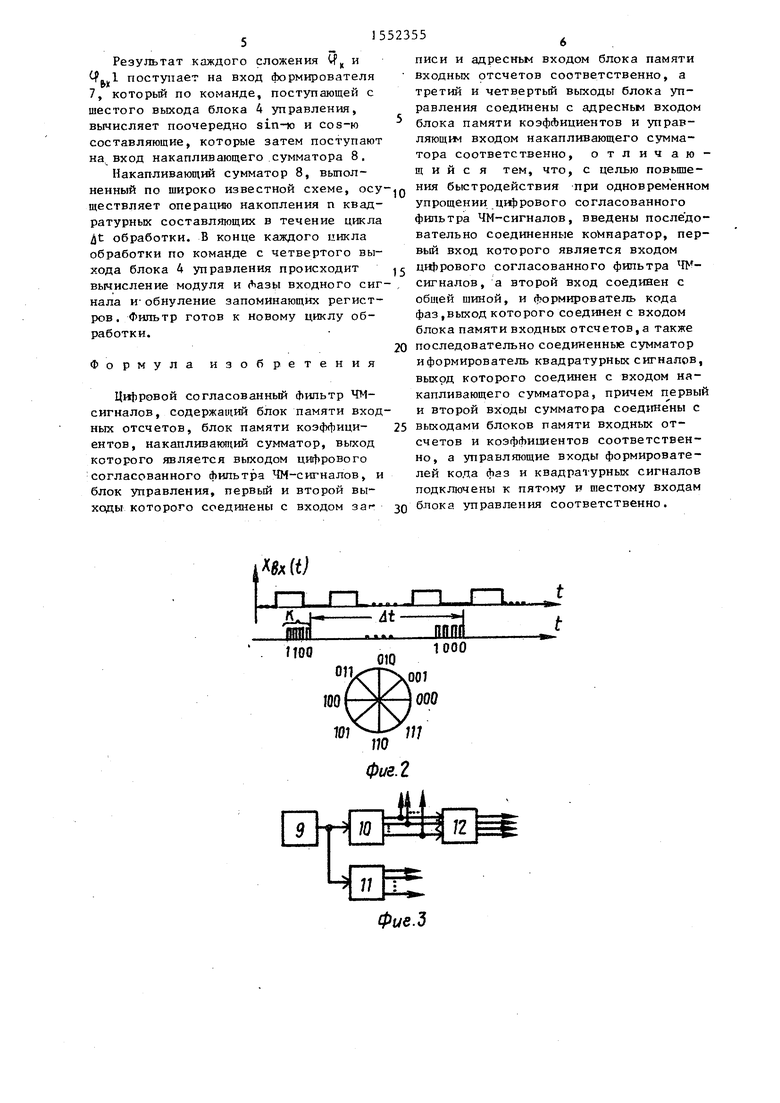

На Лиг.I приведена электрическая схема цифрового согласованного Аильт- ра ЧМ-сигналов; на Лиг.2 - временные диаграммы, поясняющие работу (Ъорми- рователя кода Ьаэ; на Лиг.З - блок управления,

Пифровой согласованный фильтр ЧМ- сигналов содержит компаратор 1 , Лор- мирователь 2 кода фаз, блок 3 памяти входных отсчетов, блок 4 управления, блок 5 памяти коэффициентов, сумматор 6, формирователь 7 квадратурных сигналов и накапливающий сумматор 8. Блок 4 управления содержит генератор 9, первый и второй счетчики 10 и 11 и блок 12 постоянной памяти.

Фильтр ЧМ-сигналов работает следующим образом.

При согласованной фильтрации осуществляется свертка принятого сигнала Х, (t) с импульсной характеристики

кой (Ьильтра. Так как при частотной модуляции информационные параметром является Лаза, то входной сигнал Xfex(t) можно представить в полярных координатах выборками единичного вектора с определенной сЪазой. При этом достаточно сложную операцию квантования входного сигнала на АЦП можно заменить на следующую. Входной сигнал Xftx(t) подается на вход компаратора 1, выполняющий сравнение с нулевым уровнем. С выхода компаратора 1 бинарный сигнал поступает на формирователь 2 кода фаз, работа которого иллюстрируется на фиг.2. На формирователе 2 через интервал At, величина которого определяется полосой частотной модуляции, берутся выборки сигнала. Взятие выборок осуществляется с помощью пачек из k импульсов, поступающих с пятого выхода блока 4 управления. Количество импульсов в пачке k выбирается исходя из требований точности квантования. Для большинства практических случаев характеристики обнаружения и измерения остаются удовлетворительными даже при 4-8- уровневом квантовании Фазы. На фиг.2 приведен случай 8-уровневого кванто-

5

0

5

0

5

0

5

0

5

вания. Затем квантованный сигнал представляется в виде двоичного кода фазы. «Формирователь 2 вырабатывает сигнал, представленный набором р-раэ- рядных (в конкретном случае 3-раэряд- ных) кодов фазы , где 1 - порядковый номер выборки.

Так как импульсная характеристика согласованного Лильтра должна быть функцией, то при способе фильтрации ее можно представить набором из р- раэряцньгх двоичных чисел ч , где Ч, фаза k-й выборки зондирующего сигнала. Значения Ч записаны в ячейки программируемого блока 5 памяти коэффициентов импульсной характеристики фильтра. С выхода формирователя 2 код фаз входного сигнала поступает на вход блока 3 памяти входных отсчетов, представляющий собой ОЗУ. На его вход записи с первого выхода блока 4 управления поступает команда записи, а на адресный вход блока 3 с второго блока 4 управления поступает адрес с номером той ячейки, в которую должна быть записана данная выборка. Адреса Лорнируются таким образом, чтобы в каждом цикле записи (с интервалом At) адрес менялся на одну единицу, общее количество ячеек блока 3 равно числу выборок п. При поступлении (п+1)-й выборки она записывается в ту же ячейку, в которую была записана первая выборка, которая при этом стирается. По окончании команды записи блок 3 переводится в режим чтения, а с его выхода двоичные коды фаз входного сигнала поступают на первый вход сумматора 6, на второй вход-которого поступают коды 0.

Таким образом, операция умножения двух комплексных чисел заменяется простейшей операцией сложения двух р-разрядных чисел, быстродействие которой определяется только быстродействием выбранной микросх 1 1 сумматора 6. Номера вызываемые ячеек блока 5 поступают на его адресный вход с третьего выхода блока 4 управления.

За время между двумя отсчетами дt на сумматоре 6 происходит п сложений Cf и Ч В режиме чтения номера вызываемых на блоке 3 ячеек Лорнируются так, что з каждом следующем цикле обработки они сдвигаются относительно номера вызываемой ячейки блока 5 на единицу.

Результат каждого сложения tf и .ц поступает на вход (Ьормировлтеля 7, который по команде, поступающей с шестого выхода блока 4 управления, вычисляет поочередно sin-ю и cos-ю составляющие, которые затем поступают на вход накапливающего сумматора 8.

Накапливающий сумматор 8, выполненный по широко известной схеме, ocy ществляет операцию накопления п квадратурных составляющих в течение цикла /jt обработки. В конце каждого пикла обработки по команде с четвертого выхода блока 4 управления происходит вычисление модуля и гЬаэы входного сигнала и обнуление запоминающих регистров. Фильтр готов к новому циклу обработки.

Формула изобретения

Цифровой согласованный фильтр ЧМ- сигналов, содержащий блок памяти входных отсчетов, блок памяти коэффициентов, накапливающий сумматор, выход которого является выходом цифрового согласованного фильтра ЧМ-сигналов, и блок управления, первый и второй выходы которого соединены с входом

101

т

y-jg аг6

писи и адресньм входом блока памяти входных отсчетов соответственно, а третий и четвертый выходы блока управления соединены с адресньм входом блока памяти коэффициентов и управляющим входом накапливающего сумматора соответственно, отличающийся тем, что, с целью повыше

ния быстродействия при одновременном упрощении цифрового согласованного фильтра ЧМ-сигналов, введены последовательно соединенные комнаратор, пер- вьй вход которого является входом цифрового согласованного фильтра ЧУ- сигналов, а второй вход соединен с общей шиной, и Формирователь кода фаз,выход которого соединен с входом блока памяти входных отсчетов, а также

последовательно соединенные сумматор и формирователь квадратурных сигналов, выход которого соединен с входом накапливающего сумматора, причем первый и второй входы сумматора соединены с

выходами блоков памяти входных отсчетов и коэффициентов соответственно, а управляющие входы формирователей кода фаз и квадратурных сигналов подключены к пятому и шестому входам

бпока управления соответственно.

юоо

Фиг. 2

| Громкоговорящий телефон | 1925 |

|

SU2621A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-03-23—Публикация

1988-01-04—Подача