ел ел

со

со

vj

J

Изобретение относится к вычисли- (тельной технике и может быть использовано в ЭВМ.

Целью изобретения является расширение функциональных возможностей за счет обеспечения контроля перекрывающихся последовательностей импульсов.

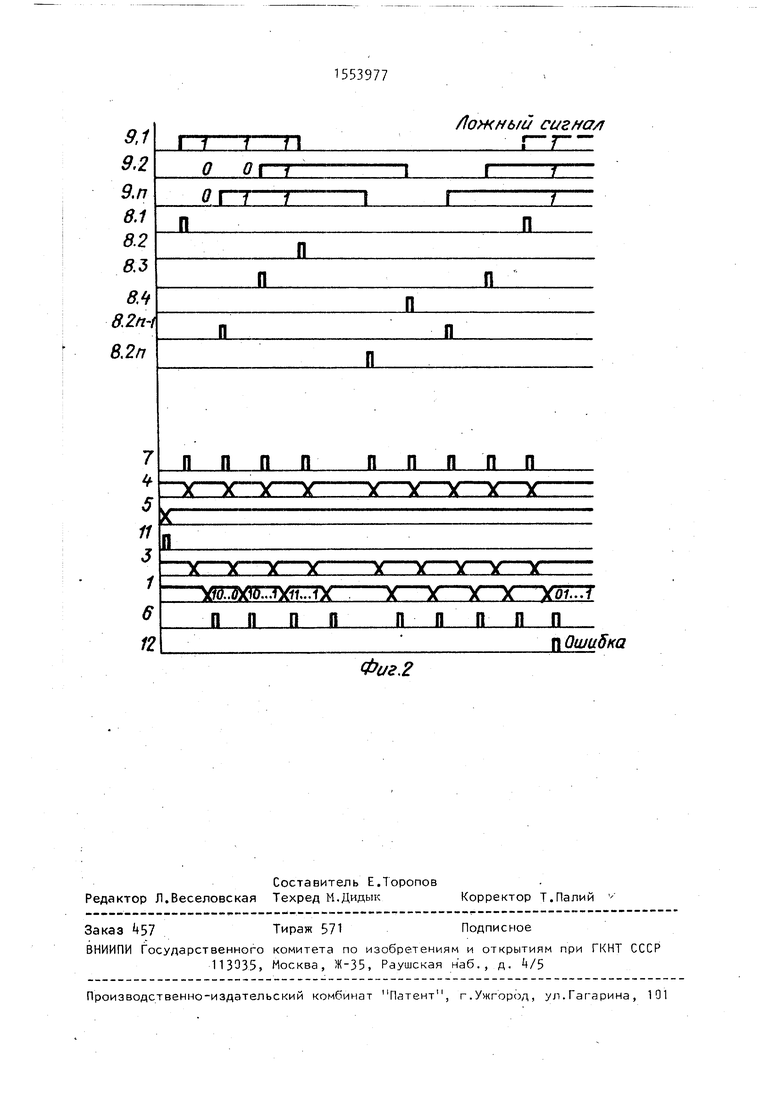

На фиг.1 приведена функциональная схема устройства; на фиг.2 - времен- ные диаграммы функционирования.

Устройство содержит блок 1 постоянной памяти, блок 2 сравнения, сумматор 3, счетчик Ц, регистр 5, эле- мент 6 задержки, элемент ИЛИ 7, труп- jny одновибраторов 801-8.2п, нечетные |из которой 8.1-8.2п-1 реагируют на пе редний фронт импульса, а четные j8.2-8.2n - на задний фронт импульса, входы 9.1-9-п контролируемых последо- вательностей, входы 10 задания начальных условий устройства, синхро- вход 11 разрешения записи, выход 12

|С6ОЯ.

Устройство работает следующим об- разом.

Вначале производится настройка устройства на контроль заданий импульсной последовательности. При этом на входах 10 устройства устанав- ливается начальный адрес блока 1 постоянной памяти, после которого аписана эталонная последователь- i. ность, а по импульсу на входе 11 разрешения записи устройства информация с входов 10 заносится в регистр 5. В исходном состоянии счетчик сброшен в нулевое состояние, поэтому на выходе сумматора 3 также устанавливается начальный адрес блока 1 постоянной памяти, после которого записана эталонная последовательность. При изменении уровней логических сиг1алов на входах 9 устройства срабатывают соответствующие нечетные (при изменении уровня с О на 1) или четные (при изменении уровня 1 на О) одновибраторы из группы одновибраторов 8.1-8.2п. Так, например, при изменении уровня логического сигнала с О на 1 на входе 9.1 группы 9 устройства срабатывает одновибратор 8.1 (см. фиг.2), при том же изменени на входе 9.2 (не показан на фиг.1) срабатывает одновибратор 8.3 (не показан на фиг.1) и т.д„ При измене- нии уровня логического сигнала с 1 на О на входе 9«1 группы 9 устройства срабатывает одновибратор 8.2,

5

0

5

0

при том же изменении на входе 9.2 (не показан на Фиг.1) срабатывает одновибратор 8. 4 (не показан на фиг.1) и т.д. Выходные сигналы пар нечетный - четный одновибратор (8.1-8.2; ... 8.2п-1-8.2п) из группы одновибраторов логически суммируются на элементе ИЛИ 7 о Поэтому изменение логических уровней на любом из входов 9 приводит к тому, что изменяется по переднему фронту сигнала на выходе элемента ИЛИ 7 состояние счетчика k. Это приводит к тому, что на выходе сумматора 3, суммирующего сигналы с выходов счетчика Ц и регистра 5, устанавливается адрес следующей ячейки блока 1 постоянной памяти„ Так, например, при первом возбуждении выхода элемента ИЛИ 7 (см. фиг„2) в соответствии с изменением сигнала на входе 8.1 информационных входов 8 устройства на выходе блока 1 постоянной памяти уста навливается эталонный сигнал 10...0. Этот эталонный сигнал поступает на первую группу входов блока 2 сравнения, на вторую группу входов которого поступают сигналы с входов 9 устройства, но само сравнение происходит после срабатывания элемента 6 задержки, выход которого стробирует блок 2 сравнения. Тем самым исключается ложное срабатывание блока 2 сравнения в переходных процессах. Таким образом, по импульсу на выходе элемента 6 задержки блок 2 сравнения сравнивает эталонное значение 10 .„. О с реальным набором сигналов на информационных входах 9 устройства, так как они равны, то выход 12 устройства (выход неравенства блока 2 сравнения) не будет возбужден. При следующем изменении уровней логических сигналов на информационных входах 9 устройства вновь возникает импульс на выходе элемента ИЛИ 7, изменяется состояние счетчика А и на выходе блока 1 памяти устанавливается очередной эталонный сигнал 10...1, по импульсу на выходе элемента 6 задержки происходит сравнение этого сигнала с реальным набором сигналов на информационных входах 9 устройства, так как они равны, то выход 12 устройства не будет возбужден. При очередном изменении состояния входов 9 устройства из блока 1 постоянной памяти считывается очередной эталонный сигнал 11... 1 и так далее, при

каждом изменении уровней логических сигналов на информационных входах производится сравнение этих наборов с эталонными, т.е0 производится контроль импульсных последовательностей.

При возникновении ложного сигнала, например, на разряде 9.1 информационных входов 9 устройства по соответствующему импульсу на выходе элемента 6 за/Гержки в результате несравнения сигналов 01....1 (эталонный сигнал) и 11.... 1 (реальный набор сигналов) возбуждаются выход блока 2 сравнения и выход 12 устройства, свидетельству- ющий о наличии ложного набора сигналов в импульсной последовательности, поступающей на входы 9 устройства.

При необходимости контроля другой последовательности импульсов в ре- гистр 5 записывается начальный адрес блока 1 постоянной памяти, по которому записана первая команда требуемой эталонной последовательности.

Формула изобретения

Устройство для контроля последовательностей импульсов, содержащее блок постоянной памяти, счетчик и регистр, причем информационные входы регистра являются входами задания начальных условий устройства, вход разрешения записи регистра является синхровходом

устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения контроля перекрывающихся последовательностей импульсов, в него введены сумматор, блок сравнения, элемент задержки, элемент ИЛИ и группа из 2п одновибраторов (где п - число контролируемых последовательностей, причем первая группа информационных входов блока сравнения соединена с группой выходов блока памяти, вторая группа информационных входов блока сравнения является группой входов -контролируемых последовательностей устройства, стробирующий вход блока сравнения соединен с выходом элемента задержки, выход блока сравнения является выходом сбоя устройства, группа выходов регистра соединена с первой группой входов сумматора, вторая группа входов которого соединена с группой разрядных выходов счетчика, выходы сумматора соединены с адресными входами блока постоянной памяти, входы (21-1)-го и 21-го одно- вибраторов Ј ...(2п-1),п группы соединены с 1-м входом контролируемой последовательности устройства, выходы одновибраторов соединены с входами элемента ИЛИ, выход которого соединен со счетным входом счетчика и входом

элемента задержки.

i

Фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство решения систем логических уравнений | 2017 |

|

RU2654137C1 |

| Устройство для контроля кодовых последовательностей | 1988 |

|

SU1575187A1 |

| Устройство для программного контроля | 1987 |

|

SU1464142A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Устройство для контроля программных автоматов | 1988 |

|

SU1571552A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Устройство для отладки мультипрограммных систем | 1989 |

|

SU1735855A1 |

| Устройство для управления восстановлением микропрограмм при сбоях | 1982 |

|

SU1056193A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1277105A1 |

Изобретение относится к вычислительной технике и может быть использовано в ЭВМ. Отличительной особенностью устройства является то, что оно обеспечивает контроль импульсных последовательностей, представляющих собой произвольные последовательности изменения уровней логических сигналов, в том числе и перекрывающихся последовательностей. Целью изобретения является расширение функциональных возможностей за счет обеспечения контроля перекрывающихся последвательностей импульсов. Поставленная цель достигается за счет введения элемента 6 задержки, элемента ИЛИ 7, одновибраторов 8.1...8.2N, блока 2 сравнения. 2 ил.

| Авторское свидетельство СССР № , кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля двух последовательностей импульсов | 1986 |

|

SU1376088A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ( УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОСЛЕДОВАТЕЛЬНОСТЕЙ ИМПУЛЬСОВ | |||

Авторы

Даты

1990-03-30—Публикация

1988-05-10—Подача