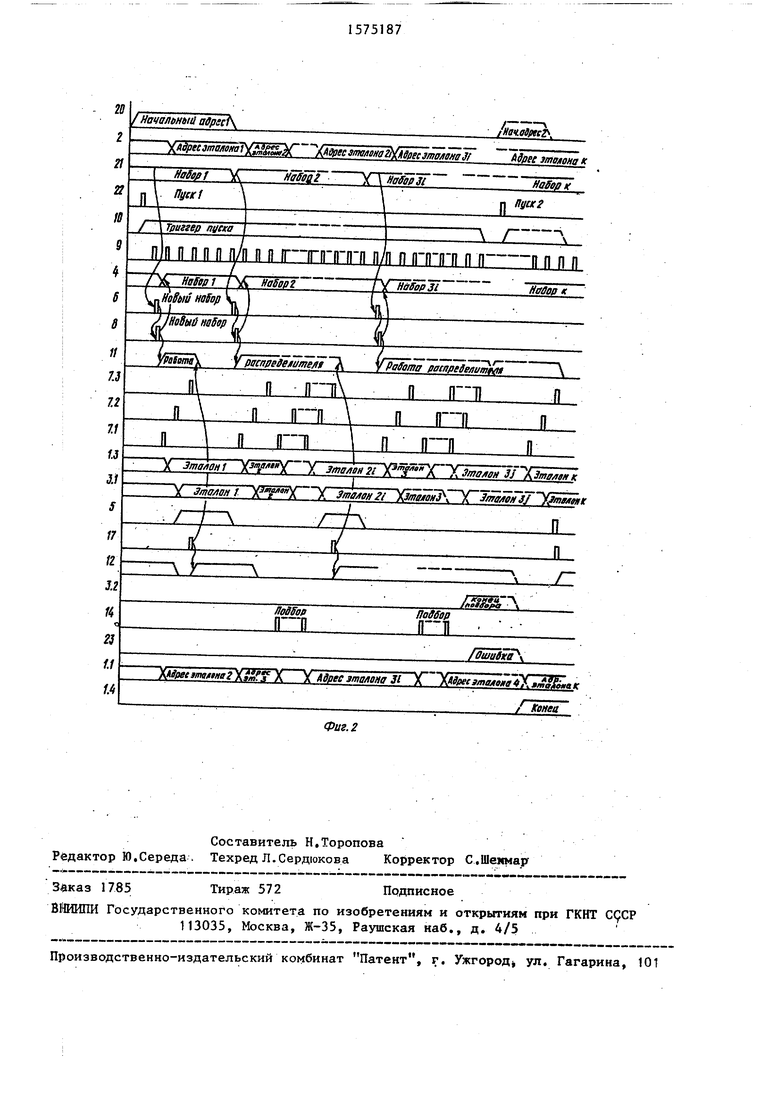

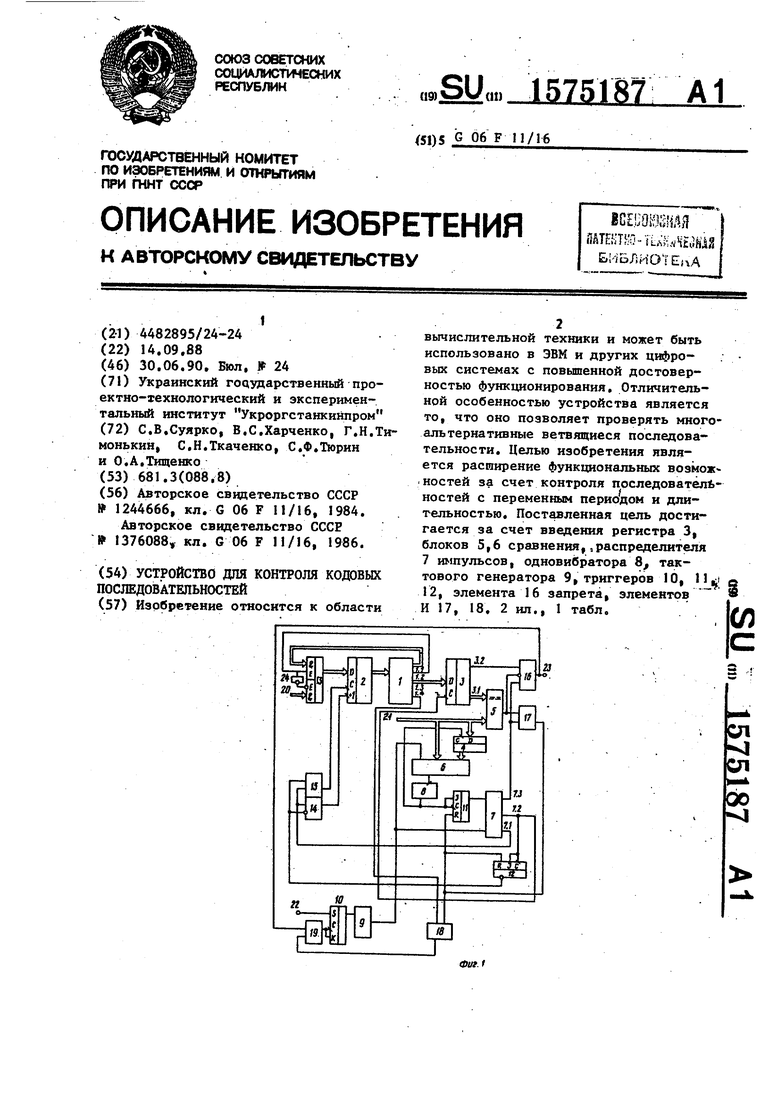

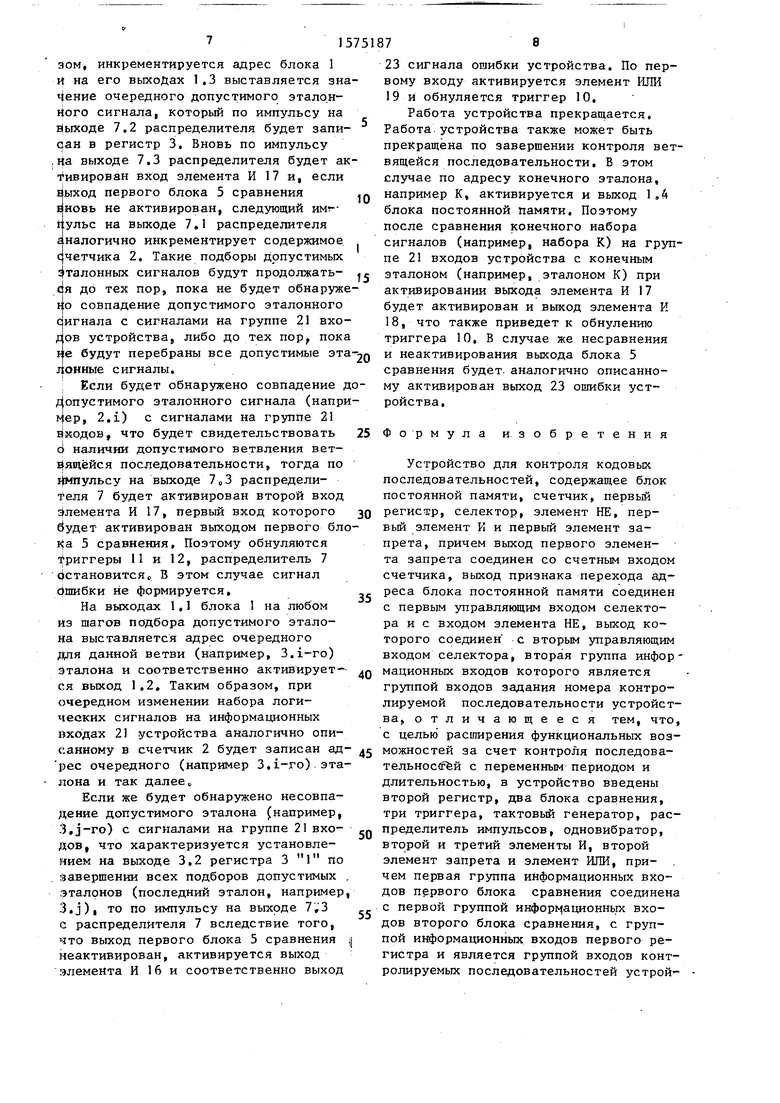

На фиг,1 представлена функциональ- схема предлагаемого устройства; на - временная диаграмма его работы.

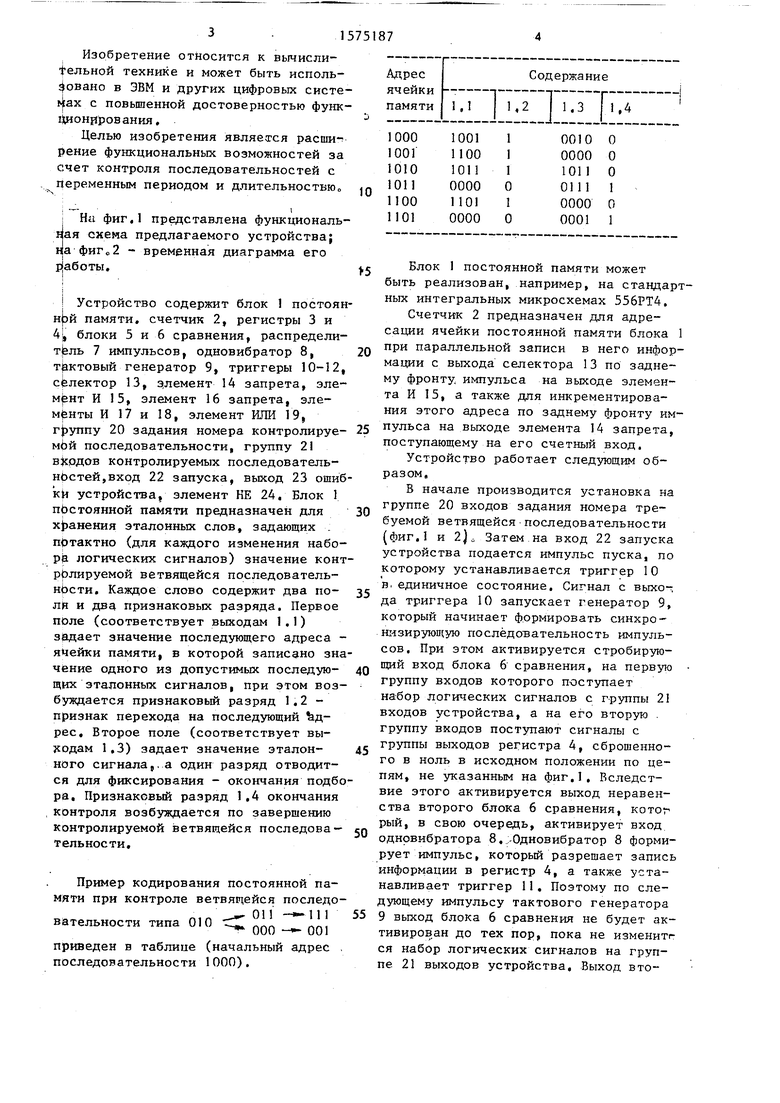

Устройство содержит блок 1 постоянной памяти, счетчик 2, регистры 3 и 4, блоки 5 и 6 сравнения, распределитель 7 импульсов, одновибратор 8, тактовый генератор 9, триггеры 10-12, селектор 13, элемент 14 запрета, элемент И 15, элемент 16 запрета, элементы И 17 и 18, элемент ИЛИ 19, группу 20 задания номера контролируе- мой последовательности, группу 21 входов контролируемых последовательностей,вход 22 запуска, выход 23 ошибки устройства, элемент НЕ 24. Блок 1 постоянной памяти предназначен для хранения эталонных слов, задающих пОтактно (для каждого изменения набора логических сигналов) значение контролируемой ветвящейся последовательности. Каждое слово содержит два по- ля и два признаковых разряда. Первое поле (соответствует выходам 1.1) задает значение последующего адреса - ячейки памяти, в которой записано значение одного из допустимых последую- щих эталонных сигналов, при этом возбуждается признаковый разряд 1.2 - признак перехода на последующий &д- рес. Второе поле (соответствует выходам 1.3) задает значение эталон- ного сигнала, а один разряд отводится для фиксирования - окончания подбора. Признаковый разряд 1.4 окончания контроля возбуждается по завершению

контролируемой ветвящейся последова-

тельности.

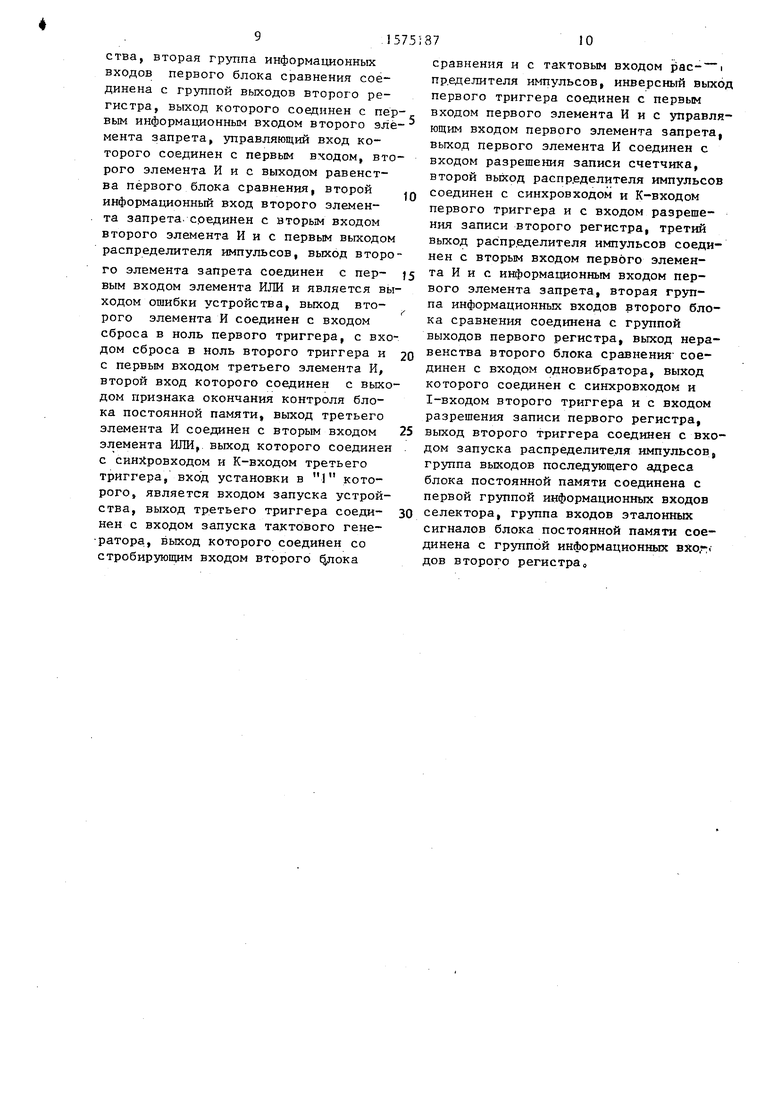

Пример кодирования постоянной памяти при контроле ветвящейся последо... ОН --111

вательности типа 010 -.лп Г1П.

иии - ии 1

приведен в таблице (начальный адрес последояательности 1000).

5

0 5 0 5 0 5

Q

5

Блок 1 постоянной памяти может быть реализован, например, на стандартных интегральных микросхемах 556РТ4.

Счетчик 2 предназначен для адресации ячейки постоянной памяти блока 1 при параллельной записи в него информации с выхода селектора 13 по заднему фронту импульса на выходе элемента И 15, а также для инкрементирова- ния этого адреса по заднему фронту импульса на выходе элемента 14 запрета, поступающему на его счетный вход.

Устройство работает следующим образом,

В начале производится установка на группе 20 входов задания номера требуемой ветвящейся последовательности (фиг.1 и 2)„ Затем на вход 22 запуска устройства подается импульс пуска, по которому устанавливается триггер 10 в единичное состояние. Сигнал с выхода триггера 10 запускает генератор 9, который начинает формировать синхронизирующую последовательность импульсов. При этом активируется стробирую- щий вход блока 6 сравнения, на первую группу входов которого поступает набор логических сигналов с группы 21 входов устройства, а на его вторую группу вкодов поступают сигналы с группы выходов регистра 4, сброшенного в ноль в исходном положении по цепям, не указанным на фиг.1. Вследствие этого активируется выход неравенства второго блока 6 сравнения, котог рый, в свою очередь, активирует вход одновибратора 8, Одновибратор 8 формирует импульс, который разрешает запись информации в регистр 4, а также устанавливает триггер 11. Поэтому по следующему импульсу тактового генератора 9 выход блока 6 сравнения не будет активирован до тех пор, пока не изменитг ся набор логических сигналов на группе 21 выходов устройства. Выход вто515

рого триггера 11 активирует вход разрешения распределителя 7, который распределяет последующие импульсы с тактового генератора 9 на свои выходы 7.1, 7.2и7,3 в порядке номеров выходов .

По импульсу на выходе 7.1 распределителя активируется выход элемента И 15, так как на его первый вход по- дана 1 с инверсного выхода триггера 12, обнуленного в исходном состоянии по цепям, не указанным на Выход 1.2 блока 1 постоянной памяти обнулен в исходном положении, так как обнулен счетчик 2 по цепям, не указанным на фиг.1. Поэтому активирован второй управляющий вход селектора 13 и информация с группы 20 входов по первой группе входов селек- тора поступает на информационные входы счетчика 2, которая и записывается в него по заднему фронту импульса на выходе элемента И 15„ Таким образом, на выходах счетчика 2 устанавливается адрес ячейки памяти, в котором хранится значение первого эталона. Вследствие этого на выходах 1.3 блока 1 постоянной памяти устанавливается значение логических сигналов, соответст- вующих первому эталонному сигналу, а на выходах 1.1 - адрес ячейки памяти, в которой хранится значение следующего эталонного сигнала, устанавливается значение 1 на выходе 1.2 блока 1. Импульс на выходе 7,2 распределителя 7 устанавливает триггер 12 в состояние Yll, а также по входу разрешения записи задним фронтом записывает в первый регистр 3 информацию с выходов 1.3 блока 1, так что на его выходах 3.1 устанавливается значение логических сигналов, соответствующих первому эталонному сигналу. Блок 5 сравнения постоянно сравни- вает значение реального набора логических сигналов на группе 21 входов устройства с сигналами на выходах 3,1 регистра 3, При равенстве эталонных и реальных сигналов блок 5 сравнения формирует на своем выходе равенства сигнал 1, которая активирует первый вход элемента И 17.

Тогда по импульсу на выходе 7.3 распределителя 7 активируется второй вход элемента И 17, вследствие чего обнуляются триггеры 11 и 12. Поэтому снимается сигнал запуска с входа распределителя 7. При очередном измене

.Q 20 25 п 5 , ,с rg

5

876

нии набора логических сигналов на группе 21 входов устройства по очередному импульсу на выходе тактового генератора 9 будет активирован выход блока 6 сравнения и аналогично описанному импульсу с выхода одновибра- тора 8 в регистр 4 будет записан очередной набор логических сигналов с группы 21 входов устройства. Аналогично запускается распределитель 7 импульсов, в счетчик 2 по синхроимпульсу на выходе элемента И 15 записывается адрес следующего (второго) эталона с выходов седектора 13, так как его первый вход управления активирован выходом 1 . 2 блока 1 постоянной памяти, а на его вторую группу входов поступает адрес следующего (второго) эталона с выходов 1.1 блока 1 постоянной памяти. Этот адрес устанавливается на адресных входах блока 1 постоянной памяти по выходам счетчика 2, Таким образом, на выходе 1.3 блока 1 постоянной памяти устанавливается значение очередного эталона, на выходе 1.1 - адрес ячейки памяти со значением следующего эталона, а на выходе 1,2 - значение 1. По импульсу на выходе 7.2 распределителя 7 вновь устанавливается триггер 12 и записывается в регистр 3 значение очередного эталонного сигнала с выходов 1.3 блока 1 постоянной памяти. Это новое значение эталона с выходов 3.1 регистра 3 поступает на вторую группу входов первого блока 5 сравнения, на первой группе входов которого выставлена информация ,с группы 21 входов устройства с новым набором (набором 2) логических сигналовs Далее устройство работает аналогично, реагируя на любое изменение уровней логических сигналов на группе 21 входов.

В случае несравнения при очередном изменении логических сигналов на информационных входах 21 и эталонного сигнала на выходах 3.1 первого регистра 3 выход первой схемы 5 сравнения при очеред- ,. ном импульсе на выходе 7„3 распределителя 7 не будет активирован, поэтому не обнулятся триггеры 11 и 12, вследствие чего активизируется второй вход элемента 14 запрета. Поэтому очередной импульс на выходе 7„1 распределителя, активизирующий первый вход элемента 14 запрета, активирует счетный вход счетчика 2. Таким рбра715

аом, инкрементируется адрес блока 1 И на его выходах 1,3 выставляется значение очередного допустимого эталонного сигнала, который по импульсу на выходе 7.2 распределителя будет записан в регистр 3. Вновь по импульсу на выходе 7.3 распределителя будет активирован вход элемента И 17 и, если в;ыход первого блока 5 сравнения йновь не активирован, следующий им- на выходе 7.1 распределителя аналогично инкрементирует содержимое сметчика 2. Такие подборы допустимых Эталонных сигналов будут продолжать- 3я до тех пор, пока не будет обнаруже совпадение допустимого эталонного сигнала с сигналами на группе 21 вхо- д|ов устройства, либо до тех пор, пока tie будут перебраны все допустимые эта 4онные сигналы.

Если будет обнаружено совпадение д дЪпустимого эталонного сигнала (напри йер, 2.1) с сигналами на группе 21 входов, что будет свидетельствовать о наличии допустимого ветвления вет- йящейся последовательности, тогда по 1 мпульсу на выходе 7„3 распределителя 7 будет активирован второй вход элемента И 17, первый вход которого ёудет активирован выходом первого бло Ка 5 сравнения, Поэтому обнуляются триггеры 11 и 12, распределитель 7 остановится,, В этом случае сигнал бшибки не формируется.

На выходах 1.1 блока 1 на любом из шагов подбора допустимого эталона выставляется адрес очередного для данной ветви (например, 3.1-го) эталона и соответственно активирует- с я выход 1,2. Таким образом, при очередном изменении набора логических сигналов на информационных входах 21 устройства аналогично описанному в счетчик 2 будет записан ад- рее очередного (например 3,i-ro) эталона и так далее„

Если же будет обнаружено несовпадение допустимого эталона (например, 3,j-ro) с сигналами на группе 21 вхо- дов, что характеризуется установлением на выходе 3,2 регистра 3 1 по завершении всех подборов допустимых эталонов (последний эталон, например, J.j), то по импульсу на выходе 7.3 с распределителя 7 вследствие того, что выход первого блока 5 сравнения неактивирован, активируется выход элемента И 16 и соответственно выход

8

5 0

Q

Q ,

5

23 сигнала ошибки устройства. По первому входу активируется элемент ИЛИ 19 и обнуляется триггер 10,

Работа устройства прекращается. Работа устройства также может быть прекращена по завершении контроля ветвящейся последовательности, В этом случае по адресу конечного эталона, например К, активируется и выход 1,4 блока постоянной памяти. Поэтому после сравнения конечного набора сигналов (например, набора К) на группе 21 входов устройства с конечным эталоном (например, эталоном К) при активировании выхода элемента И 17 будет активирован и выход элемента И 18, что также приведет к обнулению триггера 10, В случае же несравнения и неактивирования выхода блока 5 сравнения будет аналогично описанному активирован выход 23 ошибки устройства,

Формула изобретения

Устройство для контроля кодовых последовательностей, содержащее блок постоянной памяти, счетчик, первый регистр, селектор, элемент НЕ, первый элемент К и первый элемент запрета, причем выход первого элемента запрета соединен со счетным входом счетчика, выход признака перехода адреса блока постоянной памяти соединен с первым управляющим входом селектора и с входом элемента НЕ, выход которого соединен с вторым управляющим входом селектора, вторая группа информационных входов которого является группой входов задания номера контролируемой последовательности устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет контроля последовательностей с переменным периодом и длительностью, в устройство введены второй регистр, два блока сравнения, три триггера, тактовый генератор, распределитель импульсов, одновибратор, второй и третий элементы И, второй элемент запрета и элемент ИЛИ, причем первая группа информационных входов первого блока сравнения соединена с первой группой информационных входов второго блока сравнения, с группой информационных входов первого регистра и является группой входов контролируемых последовательностей устройства, вторая группа информационных входов первого блока сравнения соединена с группой выходов второго регистра, выход которого соединен с первым информационным входом второго элемента запрета, управляющий вход которого соединен с первым входом, второго элемента И и с выходом равенства первого блока сравнения, второй 1 информационный вход второго элемента запрета, срединен с вторым входом второго элемента И и с первым выходом распределителя импульсов, выход второго элемента запрета соединен с пер- 1 вым входом элемента ИЛИ и является выходом ошибки устройства, выход второго элемента И соединен с входом сброса в ноль первого триггера, с входом сброса в ноль второго триггера и 2 с первым входом третьего элемента И, второй вход которого соединен с выходом признака окончания контроля блока постоянной памяти, выход третьего элемента И соединен с вторым входом 2 элемента ИЛИ, выход которого соединен с синхровходом и К-входом третьего триггера, вход установки в 1 которого, является входом запуска устройства, выход третьего триггера соеди- 3 нен с входом запуска тактового гене- -ратора, выход которого соединен со стробирующим входом второго б/i ока

сравнения и с тактовым входом рас-i пр.еделителя импульсов, инверсный выхо первого триггера соединен с первым входом первого элемента И и с управляющим входом первого элемента запрета, выход первого элемента И соединен с входом разрешения записи счетчика, второй выход распределителя импульсов соединен с синхровходом и К-входом первого триггера и с входом разрешения записи второго регистра, третий выход распределителя импульсов соединен с вторым входом первого элемента И и с информационным входом первого элемента запрета, вторая группа информационных входов второго блока сравнения соединена с группой выходов первого регистра, выход неравенства второго блока сравнения соединен с входом одновибратора, выход которого соединен с синхровходом и I-входом второго триггера и с входом разрешения записи первого регистра, выход второго триггера соединен с входом запуска распределителя импульсов, группа выходов последующего адреса блока постоянной памяти соединена с первой группой информационных входов селектора, группа входов эталонных сигналов блока постоянной памяти соединена с группой информационных вхог дов второго регистра о

20

f Иачаяоныа adpsct

/Нач.а9#с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного контроля | 1987 |

|

SU1464142A1 |

| Система для программного управления электроавтоматикой | 1988 |

|

SU1532899A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Устройство для ввода информации | 1983 |

|

SU1149236A1 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1429148A2 |

| Система программного управления технологическими процессами | 1989 |

|

SU1688229A1 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1413656A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

Изобретение относится к вычислительной технике и может быть использовано в ЭВМ и других цифровых системах с повышенной достоверностью функционирования. Отличительной особенностью устройства является то, что оно позволяет проверять многоальтернативные ветвящиеся последовательности. Целью изобретения является расширение функциональных возможностей за счет контроля последовательностей с переменным периодом и длительностью. Поставленная цель достигается за счет введения регистра 3, блоков 5,6 сравнения, распределителя 7 импульсов, одновибратора 8, тактового генератора 9, триггеров 10, 11, 12, элемента 16 запрета, элементов И 17, 18. 2 ил., 1 табл.

21 22 IB

{лдресзтаяотГ)

foWM эталона дХМресзпюланаЗ Afyef зталона к

11

Эталон1 . Y JtwffH2{ УРт/к;гХ Ґ Эта/1оя зТ Этаагнк

У Зта/ion) . Зтвлвн2l faiamii3 yrJMatoiTsJ

. /

tv

17

12

14

23

U

/Г

L

ПоОбор

(OuiafxiT

)(Mfleetm/Mff2Xfm У Х СлЬреСзтаяана 31 У Хю еипалоив &ят/Јн,ак

JL

/Г

L

ПоОбор

(OuiafxiT

| Устройство для контроля двух импульсных последовательностей | 1984 |

|

SU1244666A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля двух последовательностей импульсов | 1986 |

|

SU1376088A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-06-30—Публикация

1988-09-14—Подача