:о

а:

о

00 00

Изобретение относится к вычислительной технике и может быть использовано в ЭВМ и цифровых системах с повышенной достоверностью функционирования.

Цель изобретения - расширение функциональных возможностей устройст ва за счет контроля пачек импульсов с произвольным количеством импульсов в пачке.

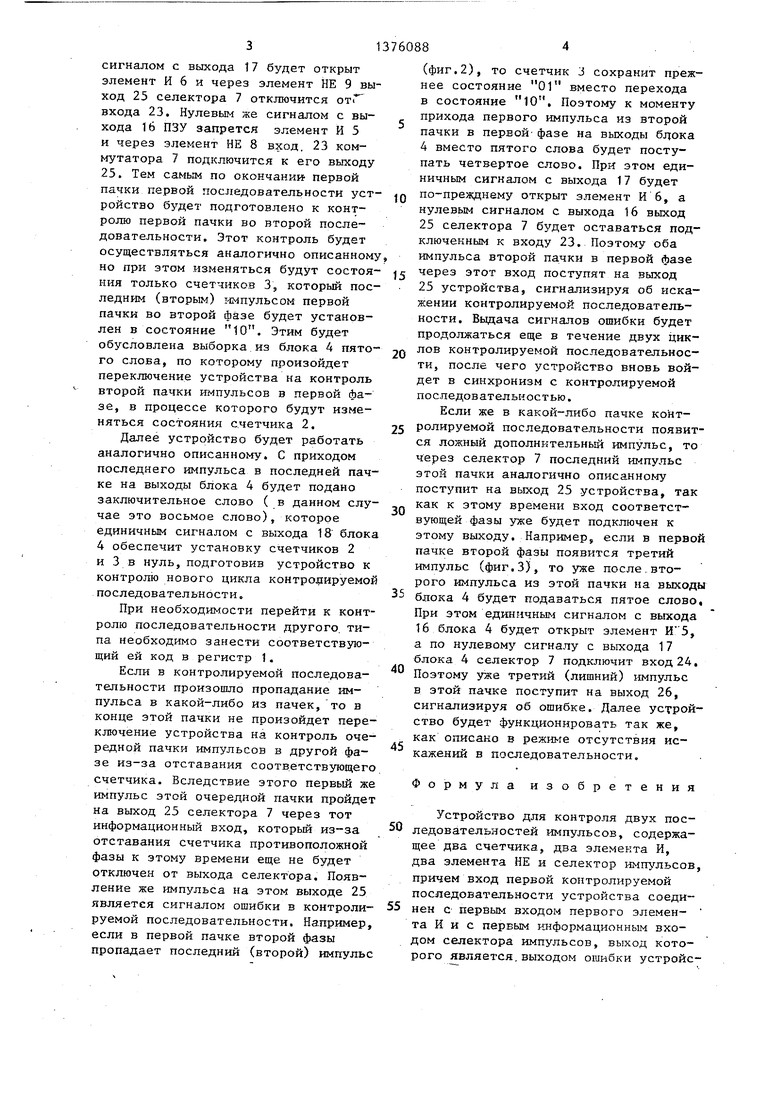

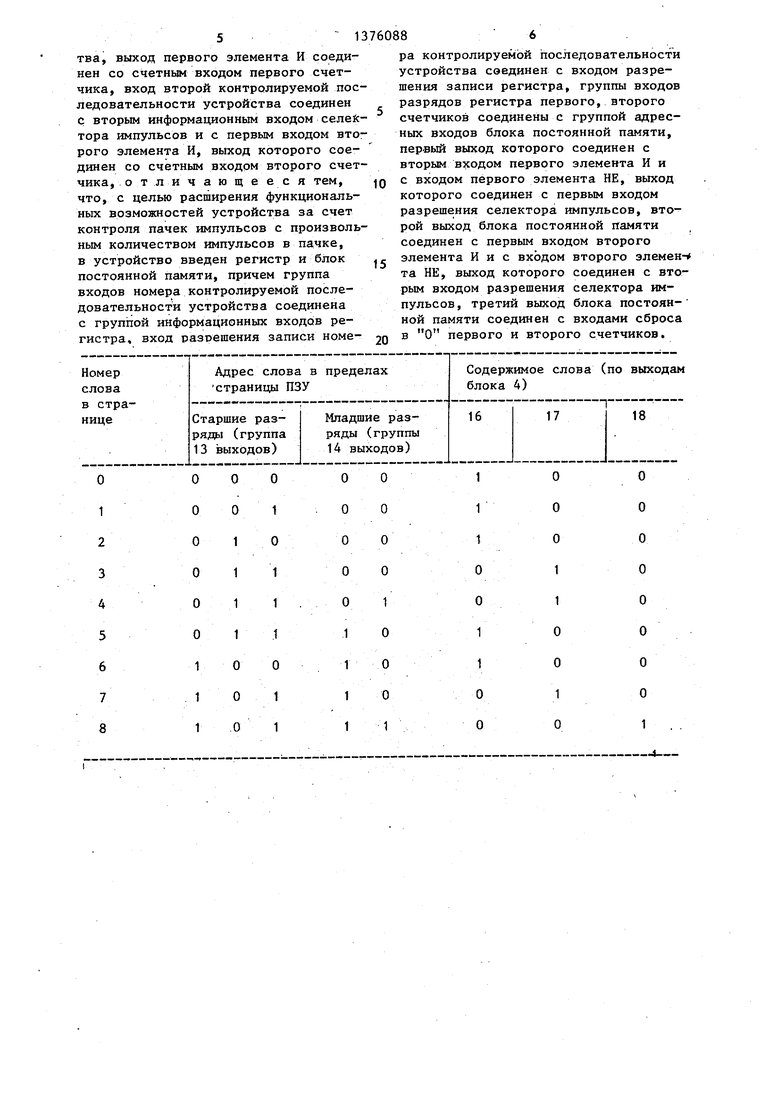

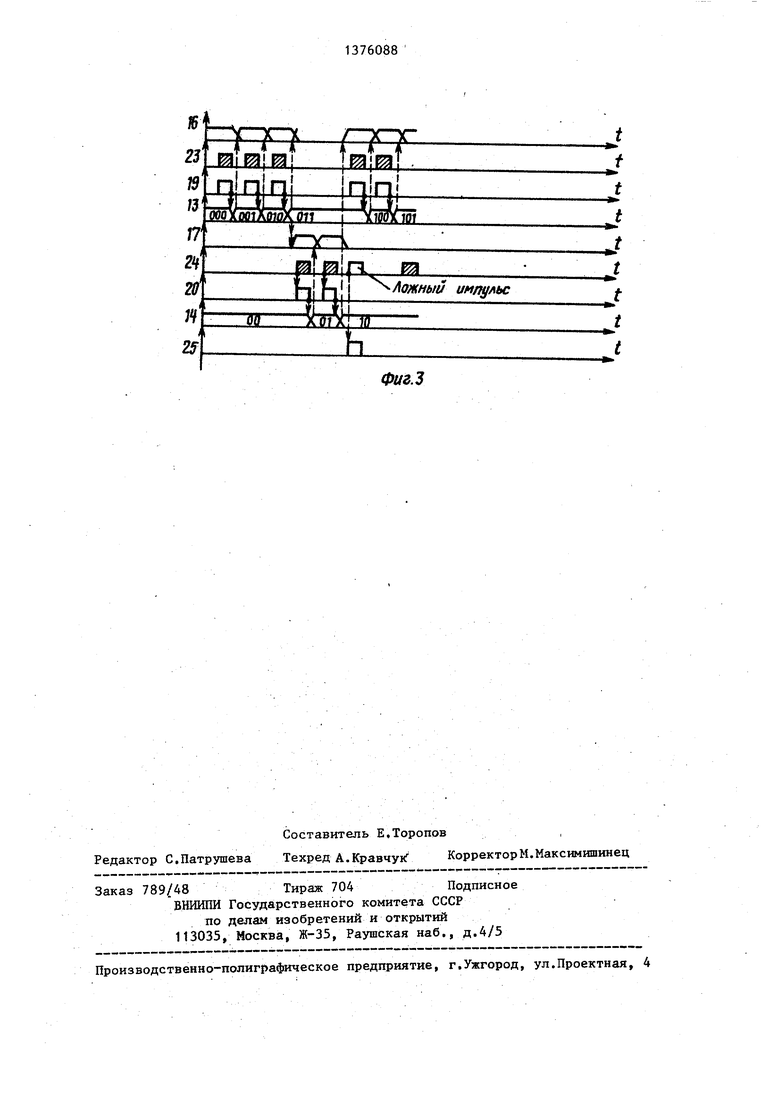

На фиг.1 приведена функциональная схема устройства; на фиг.2 и 3 - временные диаграммы его функционирования.

Устройство содержит регистр 1, первый 2 и второй 3 счетчики, блок 4 постоянной памяти, элементы И 5 и 6, селектор 7 импульсов, элементы НЕ 8 и 9, группу 10 входов номера контролируемой последовательности, вход 11 разрешения записи, группу 12 выходов регистра, группу 13 выходов первого счетчика, группу 14 выходов второго счетчика, группу 15 входов блока 4 памяти, выходы 16 - 18 блока 4 памяти, выходы 19 и 20 элементов И соответственно 5 и 6, выходы 21 и 22 элементов НЕ соответственно 8 и 9, входы 23 и 24 контролируемых последовательностей, выход 25 сигнала ошибки.

Устройство работает следующим образом,

В регистр 1 записывается код номера контролируемой последовательности под управлением сигнала,.поступающего по входу 11 разрешения записи. Этот код задает адрес страницы в .блоке 4 памяти, на которой записано эталонное значение контролируемой последовательности.

Счетчики 2 и 3 предназначены для формирования адреса слова в блоке 4 памяти путем подсчета импульсов первой и второй контролируемых последовательностей соответственно. Изменение состояний счетчиков происходит по спаду сигнала на счетном входе.

Блок 4 памяти представляет собой ПЗУ статического типа и предназначено для хранения слов, задающих по- тактно эталонное значение контролируемых последовательностей импульсов Каждое слово содержит три разряда. Первьй и второй разряды подаются на выходы 16 и 17 соответственно и задают эталонные значения сигналов на входах 23 и 24 в конце текущего так

0

5

0

0

5

5

0

5

0

5

та работы устройства (под тактом работы устройства понимается его функционирование от прихода импульса в данной одной из последовательностей. При кодировании слов в ПЗУ значение разряда принимается равным единице в том случае, если в конце такта на соответствующий вход должен поступить импульс. В противном случае значение сигнала принда1ается равным нулю. Третий разряд слова подается на выход 18 блока 4 и задает конец цикла контролируемой последовательности.

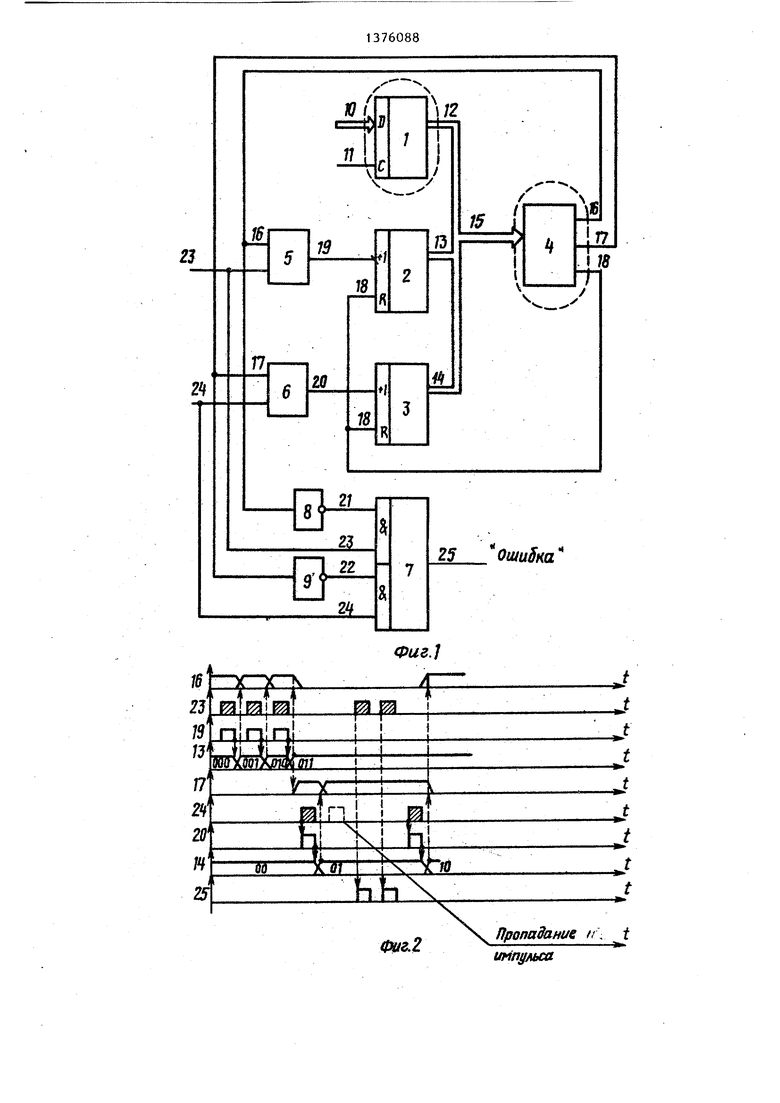

Пример кодирования страницы ПЗУ при контроле последовательности типа 3-2-2-2 (т.е. один цикл которой содержит 3 импульса в первой фазе, затем два импульса во второй фазе, затем два импульса в первой фазе, затем один импульс во второй фазе) приведен в таблице...

Пусть контролируемая последовательность формируется без искажений. Перед началом работы устройства счетчики 2 и 3 устанавливаются в исходное нулевое состояние (цепи их установки на фиг,1 условно не показаны), а в регистр 1 заносится код номера страницы, в которой записаны потакт- но эталонное значение контролируемой последовательности. Поэтому на выходах блока 4 сигналы будут иметь значение, соответствующие нулевому слову страницы (1-я строка таблицы). Единичный сигнал с выхода 16 блока 4 отпирает элемент И 5 и через элемент НЕ 6 запрещает прохождение сигнала с входа 23 первой контролируе- мой последовательности селектора 7 на выход 25. Нулевым же сигналом с выхода 17 блока 4 запирается элемент И 6 и через элемент НЕ 9 разрешается прохождение сигналов с входа 24 устройства на выход 25 селектора. С приходом первого и второго импульсов первой контролируемой последовательности содержимое счетчика 2 становится равным соответственно 001 и 010, вследствие чего на выходы блока 4 будут последовательно поданы слова номер 1 и 2 (табл,1). Поскольку эти слова совпадают с нулевым словом, то в схеме сохраняется изменение значения сигналов. С приходом же последнего (третьего) импульса в первой пачке первой последовательности на выход блока 4 будет подано слово номер три. При этом единичным

сигналом с выхода 17 будет открыт элемент И 6 и через элемент НЕ 9 выход 25 селектора 7 отключится OTi входа 23. Нулевым же сигналом с выхода 16 ПЗУ запрется элемент И 5 и через элемент НЕ 8 вход. 23 коммутатора 7 подключится к его выходу 25. Тем самым по окончании первой пачки первой последовательности устройство будет подготовлено к контролю первой пачки во второй последовательности. Этот контроль будет осуществляться аналогично описанному но при этом изменяться будут состояния только счетчиков 3, который последним (вторым) 1Ф1пульсом первой пачки во второй фазе будет установлен в состояние 10. Этим будет обусловлена выборка из блока 4 пятого слова, по которому произойдет переключение устройства на контроль второй пачки импульсов в первой фазе, в процессе которого будут изменяться состояния счетчика 2.

Далее устройство будет работать аналогично описанному. С приходом последнего импульса в последней пачке на выходы блока 4 будет подано заключительное слово ( в данном случае это восьмое слово), которое единичным сигналом с выхода 18 блока 4 обеспечит установку счетчиков 2 и 3 в нуль, подготовив устройство к контролю нового цикла контролируемой последовательности.

При необходимости перейти к контролю последовательности другого, типа необходимо занести соответствующий ей код в регистр 1.

Если в контролируемой последовательности произошло пропадание импульса в какой-либо из пачек, то в корще этой пачки не произойдет переключение устройства на контроль очередной пачки импульсов в другой фазе из-за отставания соотве тствующего счетчика. Вследствие этого первый же импульс этой очередной пачки пройдет на выход 25 селектора 7 через тот информационный вход, который из-за отставания счетчика противоположной фазы к этому времени еще не будет отключен от выхода селектора. Появление же импульса на этом выходе 25 является сигналом ошибки в контролируемой последовательности. Например, если в первой пачке второй фазы пропадает последний (второй) импульс

,

10

15

760884

(фиг.2), то счетчик J сохранит прежнее состояние 01 вместо перехода в состояние 10, Поэтому к моменту прихода первого импульса из второй пачки в первой фазе на выходы бдока 4 вместо пятого слова будет поступать четвертое слово. При этом единичным сигналом с выхода 17 будет по-прежднему открыт элемент И 6, а нулевым сигналом с выхода 16 выход 25 селектора 7 будет оставаться подключенным к входу 23. Поэтому оба импульса второй пачки в первой фазе через этот вход поступят на выход 25 устройства, сигнализируя об искажении контролируемой последовательности. Выдача сигналов ошибки будет продолжаться еще в течение двух циклов контролируемой последовательности, после чего устройство вновь войдет в синхронизм с контролируемой последовательностью.

Если же в какой-либо пачке контролируемой последовательности появится ложный дополнительный импульс, то через селектор 7 последний импульс этой пачки аналогично описанному поступит на выход 25 устройства, так как к этому времени вход соответствующей фазы уже будет подключен к этому выходу. Например, если в первой пачке второй фазы появится третий импульс (фиг.З), то уже после.второго импульса из этой пачки на выходы блока 4 будет подаваться пятое слово. При этом единичным сигналом с выхода 16 блока 4 будет открыт элемент И 5, а по нулевому сигналу с выхода 17 блока 4 селектор 7 подключит вход 24, Поэтому уже третий (лишний) 11мпульс в этой пачке поступит на выход 26, сигнализируя об ошибке. Далее устройство будет функционировать так же, как описано в режда е отсутствия искажений в последовательности.

20

25

30

35

40

45

Формула изобретения

Устройство для контроля двух последовательностей импульсов, содержащее два счетчика, два элемента И, два элемента НЕ и селектор имщшьсов, причем вход первой контролируемой последовательности устройства соединен с первым входом первого элемен- та И и с первым информационным входом селектора импульсов, выход которого является.выходом ошибки устройства, выход первого элемента И соединен со счетным входом первого счетчика, вход второй контролируемой последовательности устройства соединен с вторым информационным входом селектора импульсов и с первым входом второго элемента И, выход которого соединен со счетным входом второго счетчика, о тличающееся тем, что, с целью расширения функциональных возможностей устройства за счет контроля пачек импульсов с произвольным количеством импульсов в пачке, в устройство введен регистр и блок постоянной памяти, причем группа входов номера контролируемой последовательности устройства соединена с группой информационных входов регистра, вход разрешения записи номе

ра контролируемой последовательности устройства соединен с входом разрешения записи регистра, группы входов разрядов регистра первого, второго счетчиков соединены с группой адресных входов блока постоянной памяти, первый выход которого соединен с вторым входом первого элемента И и с входом первого элемента НЕ, выход которого соединен с первым входом разрешения селектора импульсов, второй выход блока постоянной памяти соединен с первым входом второго элемента И и с входом второго элемен- та НЕ, выход которого соединен с вторым входом разрешения селектора импульсов, третий выход блока постоян- ной памяти соединен с входами сброса в О первого и второго счетчиков.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля двух последовательностей импульсов | 1988 |

|

SU1596336A1 |

| Устройство для контроля последовательностей импульсов | 1988 |

|

SU1580371A1 |

| Устройство для контроля управляющих сигналов микропроцессора | 1989 |

|

SU1656536A1 |

| Устройство для контроля кодовых последовательностей | 1988 |

|

SU1575187A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1545222A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство для контроля управляющей вычислительной машины | 1987 |

|

SU1464163A1 |

| Устройство для управления сверхоперативной буферной памятью мультипроцессорной ЭВМ | 1981 |

|

SU980097A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

1 2 3 4 5 6 7 8

1 1 О О 1 1 О

о

о о 1 1 о о 1 о

о о о о о о о 1

23

16

19

17

2Ц

2JS

тр

23

22

Ж

/2

/3

/5

77

18

18

2 OatuSna

Фаг.

Фиг.2

Пропадание //. t имлульсй

ю

23

Ю /3

2

М я

2у

Фиг.З

| Устройство для контроля последовательности импульсов | 1983 |

|

SU1091346A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для контроля двух импульсных последовательностей | 1984 |

|

SU1244666A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-02-23—Публикация

1986-06-16—Подача