1129

Изобретение относится к вычислительной технике и может быть использовано при построении специализированных устройств, работающих в избыточных системах счисления.

Цель изобретения - расширение функциональных возможностей за счет увеличения набора используемых коэффициентов и расширения диапазона их изменения.

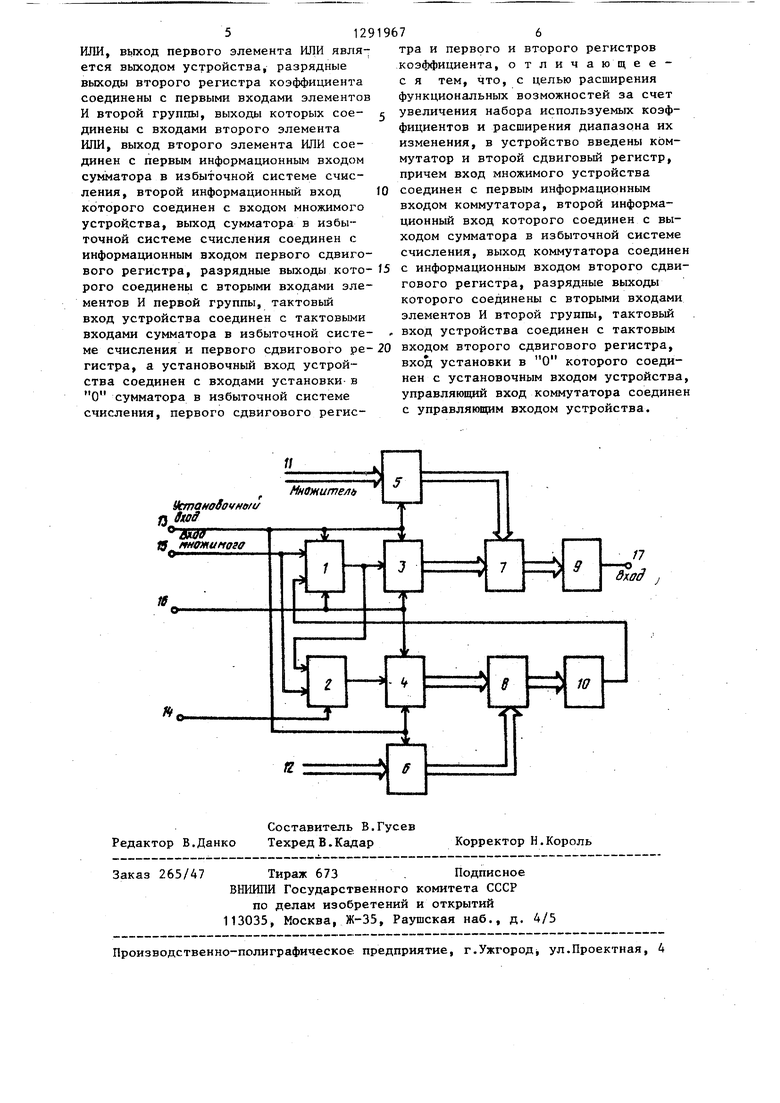

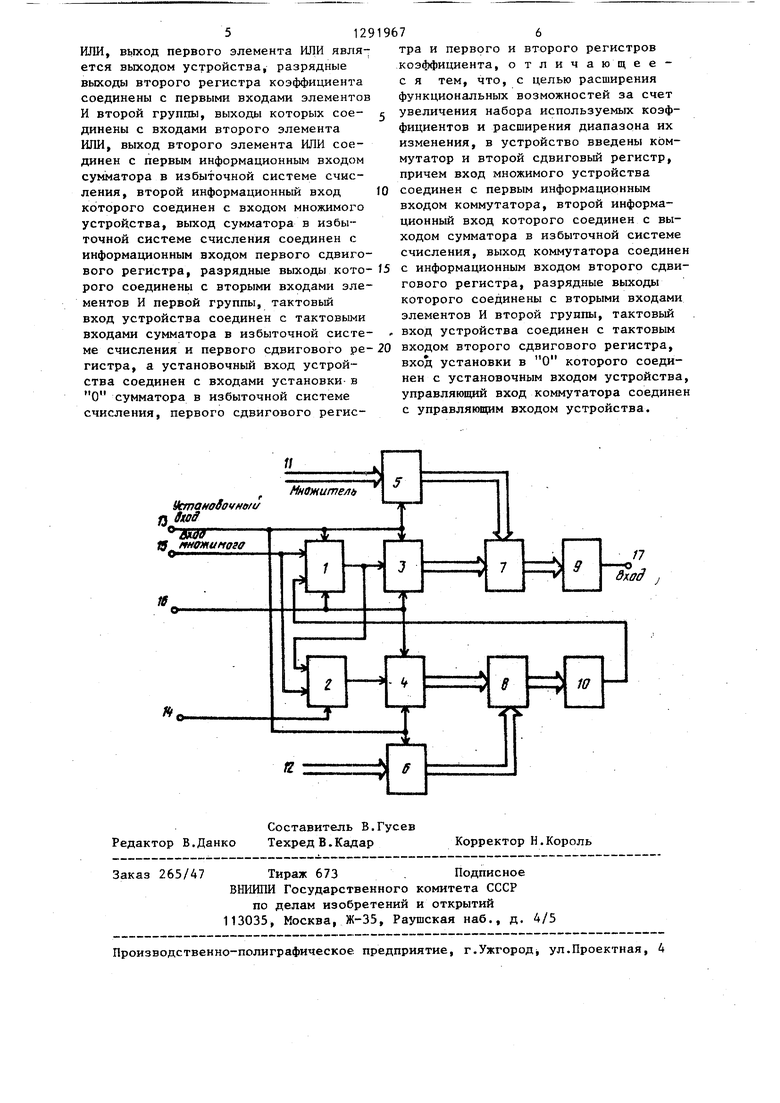

На чертеже приведена функциональная схема устройства.

Устройство для умножения на коэффициенты содержит сумматор 1 в избыточной системе счисления, коммутатор 2, первый и второй сдвиговые регистр

3и 4, первый и второй регистры 5 и 6 коэффициента, первую и вторую группы элементов И 7 и 8, первый и второй элементы ИЛИ 9 и 10, первую и вторую шины 11 и 12 множителя, установочный вход 13, управляющий вход 14j вход 15 множимого, тактовый вход 26 и выход 17,

При этом первая и вторая шины 11

412 множителя устройства соединены соответственно с информационными входами первого и второго регистров

5и 6° коэффициента, разрядные выходы первого регистра 5 коэффициента - с первыми входами элементов И 7 первой группы, выходы которых соединены с входами первого элемента ИЛИ 9, выход которого соединен с выходом 17 устройства.

Разрядные выходы второго регистра 6 коэффициента соединены с первыми входами элементов И 8 второй группы, выходы которых соединены с входами второго элемента ИЛИ 10, выход второго элемента ИЛИ 10 - с первым информационным входом сумматора 1 в избыточной системе счислени, второй информационный вход которого соединен с входом 15 множимого устройства и с первым информационным входом коммутатора 2.

-Выход сумматора 1 в избыточной системе счисления соединен с вторым информационным входом коммутатора 2 и с информационным входом первого сдвигового регистра 3, разрядные выходы которого соединены с вторыми входами элементов И 7 первой группы, выход коммутатора 2-е информационным входом второго сдвигового регистра 4, разрядные выходы которого сое

динены с вторыми входами элементов И 8 второй группы.

Тактовый вход 16 устройства соединен с тактовыми входами сумматора 1 в избыточной системе счисления и первого и второго сдвиговых регистров 3 и 4, установочный вход 13 устройства - с входами установки в О сумматора 1 в избыточной системе счисления, первого и второго сдвиговых ре- гистров 3 и 4 и первого и второго регистров 5 и 6 коэффициента, управляю- щкй вход 14 устройства - с управляющим входом коммутатора 2.

Устройство осуществляет операцию умножения множимого на коэффициент вида

,0.. .0,1. .010. . .01 . . .,

м п+с п+с

где М и С

(1)

целые, больше или равны нулю

П - максимальное число разрядов, на которое распространяется сигнал переноса в сторону старших разрядов.

Умножение на коэффициент (1) осуществляется путем подачи на второй вход сумматора в избыточной системе счисления (первый вход которого подключен к входу множимого) задержанного, на С тактов сигнала с его же выхода. Данные на выходе сумматора в избыточной системе счисления интерпретируются как результат умножения и как сумма частичных произведений. Кроме того, устройство позволяет производить умножение на коэффициенты вида

(2)

где М и С ... 0,100,.., -

С

целые, больше или равны нулю.

Устройство работает следующим образом. ,

В начале каждого цикла умножения сигнал, поступающий с установочного входа 13 устройства на входы установки сумматора 1 в избыточной системе счисления и первого и второго сдвиговых регистров 3 и 4, производит их обнуление. Одновременно этим же сигналом, поступающим на тактовые входы первого и второго регистров 5 и 6 коэффициента, производится запись

преобразованного коэффициента, перва часть которого с первой шины 11 множителя записывается в первый регистр 5 коэффициента, а вторая часть коэффициента с второй шины 12 множите- ля - во второй регистр 6 коэффициента.

Затем с тактового входа 16 устройства на тактовые входы сумматора 1 в избыточной системе счисления и пер вого и второгр сдвиговых регистров 3 и 4 начинают поступать тактирующие импульсы. Причем, количество тактов в каждом цикле вычисления равно К+П (К - разрядность множимого), что обусловлено задержкой распространени одноименных бит числа на выходе сумматора 1 в избыточной системе счисления относительно чисел на его входе на П тактов.

В случае, если сигнал с входа 14 управления устройства, который определяет тип коэффициента (1) или (2), переключает коммутатор 2 таким образом, что на его выход коммутируется сигнал с его второго входа, то на второй вход сумматора 1 в избыточной системе счисления поступают биты множимого с входа 15 множимого старшими разрядами вперед, а на первый вход сумматора 1 в избыточной системе счисления с выхода второго элемента ИЛИ 10 - значение того же множимого, но задержанное на С тактов. Таким образом, на выходе сумматора 1 в из- быт очной системе счисления формируется произведение множимого на коэффициент 1,0...010..., где число нулей между двумя единицами равно С. Этот результат посредством первого сдвигового регистра 3, первой группы элементов И 7 и первого элемента ИЛИ 9 задерживается на М тактов, в результате чего на выходе 17 устройства формируется произведение множимого на коэффициент (2).

В случае, если сигнал с входа 14 управления устройства переключает коммутатор 2 таким образом, что на его выход коммутируется сигнал с его первого входа, то на второй вход сумматора 1 в избыточной системе счисления поступает множимое со входа 15

множимого, а на первый вход с выхода второго элемента ИЛИ 10 - значение суммы частичных произведений, формируемых на выходе сумматора 1 в избыточной системе счисления, задержанное на С тактов. С учетом внутренней

задержки сумматора 1 в из&ыточной системе счисления на П тактов суммарная задержка появления бит суммы частичных произведений на первый вход сумматора 1 в избыточной системе счисления относительно появления одноименных бит множимого на втором входе составляет С +П тактов. Поступающая на первый вход сумматора 1 в избыточной системе счисления сумма частичных произведений совместно с

вход, участвуют в формировании новой суммы частичных произведений, которая в то же время является произведением множимого на коэффициент 1,0... 010...010...010..., где число нулевых битов, заключенных между единичными битами, равно С +п . Этот результат посредством первого сдвигового регистра 3, первой группы элементов И 7 и первого элемента ИЛИ 9 задерживается на М тактов, в результате чего на выходе 17 устройства ормируется произведение множимого на коэффициент (1).

После того, как на второй вход сумматора 1 в избыточной системе

счисления поступят все К бит множимого, сумматор 1 в избыточной системе счисления еще П тактов продолжает довычислять результат произведения. В течение этих П тактов на второй

вход сумматора 1 в избыточной системе счисления необходимо подавать О или сигнал, приводящий к формированию округления результата умножения. Кон- кретньш вид сигнала определяется в зависимости от того, какая именно истема счисления применяется.

ормула изобретения

Устройство для умножения на коэффициенты, содержащее сумматор в избыточной системе счисления, первый сдвиговый регистр, первый и второй регистры коэффициента, первую и втоРУЮ группы элементов И, первый и второй элементы ИЛИ, причем первая и вторая шины множителя устройства соединены соответственно с информационными входами первого и второго регистров коэффициента, разрядные выходы первого регистра коэффициента соединены с первыми входами элементов И первой группы, выходы которых соединены с вводами первого элемента

ИЛИ, В1.1ХОД первого элемента ИЛИ является выходом устройства, разрядные выходы второго регистра коэффициента соединены с первыми входами элементов И второй группы, выходы которых сое- динены с входами второго элемента ИЛИ, выход второго элемента ИЛИ соединен с первым информационным входом сумматора в избыточной системе счисления, второй информационный вход которого соединен с входом множимого устройства, выход сумматора в избыточной системе счисления соединен с информационным входом первого сдвигового регистра, разрядные выходы кото- рого соединены с вторыми входами элементов И первой группы, тактовьш вход устройства соединен с тактовьи 1и входами сумматора в избыточной системе счисления и первого сдвигового ре- гистра, а установочный вход устройства соединен с входами установки в О сумматора в избыточной системе счисления, первого сдвигового регисРедактор В.Данко

Составитель В.Гусев Техред В.Кадар

Заказ 265/47 Тираж 673 . Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г,Ужгородj ул.Проектная, 4

тра и первого и второго регистров коэффициента, отличающее- с я тем, что, с целью расширения функциональных возможностей за счет увеличения набора используемых коэффициентов и расширения диапазона их изменения, в устройство введены коммутатор и второй сдвиговый регистр, причем вход множимого устройства соединен с первым информационным входом коммутатора, второй информационный вход которого соединен с выходом сумматора в избыточной системе счисления, выход коммутатора соедине с информационным входом второго сдвигового регистра, разрядные выходы которого соединены с вторыми входами элементов И второй группы, тактовый вход устройства соединен с тактовым входом второго сдвигового регистра, вход установки в О которого соединен с установочным входом устройства управляющий вход коммутатора соедине с управляющим входом устройства.

Корректор Н.Король

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения на коэффициенты | 1984 |

|

SU1242925A1 |

| Устройство для умножения на коэффициенты | 1985 |

|

SU1295381A1 |

| Устройство для умножения на коэффициенты | 1985 |

|

SU1291966A1 |

| Устройство для умножения на коэффициенты | 1987 |

|

SU1458872A1 |

| Устройство для умножения на коэффициенты | 1988 |

|

SU1562904A1 |

| Устройство для умножения на коэффициенты | 1986 |

|

SU1442987A1 |

| Устройство для умножения в избыточной четверичной системе счисления | 1983 |

|

SU1160399A1 |

| Устройство для умножения на коэффициенты | 1985 |

|

SU1397901A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Арифметическое устройство | 1984 |

|

SU1236473A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении специализированных устройств, работакмцих в избыточных системах счисления. Цель изобретения - расширение функциональных возможностей за счет увеличения набора используемых коэффициентов и расширен ия диапазона их изменения. Предлагаемое устройство содержит сумматор в избыточной системе счисления, коммутатор, четыре регистра, две группы элементов И и два элемента ИЛИ с соответствующими связями. Устройство осуществляет умножение на коэффициент путем подачи на вход сумматора в избыточной системе счисления множимого и задержанного на С тактов сигнала с выхода сумматора, интерпретируя данные на его выходе как результат умножения и как сумму частичных произведений. 1 ил. (Л

| Устройство для умножения | 1981 |

|

SU1005035A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Авторское свидетельство СССР по заявке № 3826642/24, кл | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1987-02-23—Публикация

1985-09-17—Подача