с выхода которого (по переднему фрон-2Q гистр 14, в котором накапливается

Ту) триггер 7 устанавливается в единичное состояние, на его инверсном выходе устанавпивается сигнал нулевого уровня, который через элемент ИПИ 6 поступает на установочный вход счетчика ч, разрешая последнему по окончании импульса малой длительности (длительность импульса выбирается из условия надежного обнуления счетчика) с выхода формирователя 11 счет импульсов, поступающих по тактовому входу. Кроме того, на инверсном выходе триггера 7 действие импульса уста- нова прекращается для вычислителей 2 и блока 3, и, тем самым, разрешается Их работа. Импульс с выхода формирователя 11 поступает на тактовые входы вычислителей 2, блоков 3 и 4. Данные из регистра 12 поступают в блоки 2 и 3.

При поступлении следующих импульсов сигнала процессы преобразования Повторяются.

Если после поступления какого-либо импульса на информационный вход следующий импульс не поступает за время, большее максимальной временной базы кода, то счетчик 9 продолжает счет импульсов до переполнения, с выхода Р импульс переполнения поступает на второй вход установки в нуль триггера 7, который возвращается в исходное (нулевое ) состояние и. возвращает через элемент ИЛИ 6 в это же состояние счетчик 9.

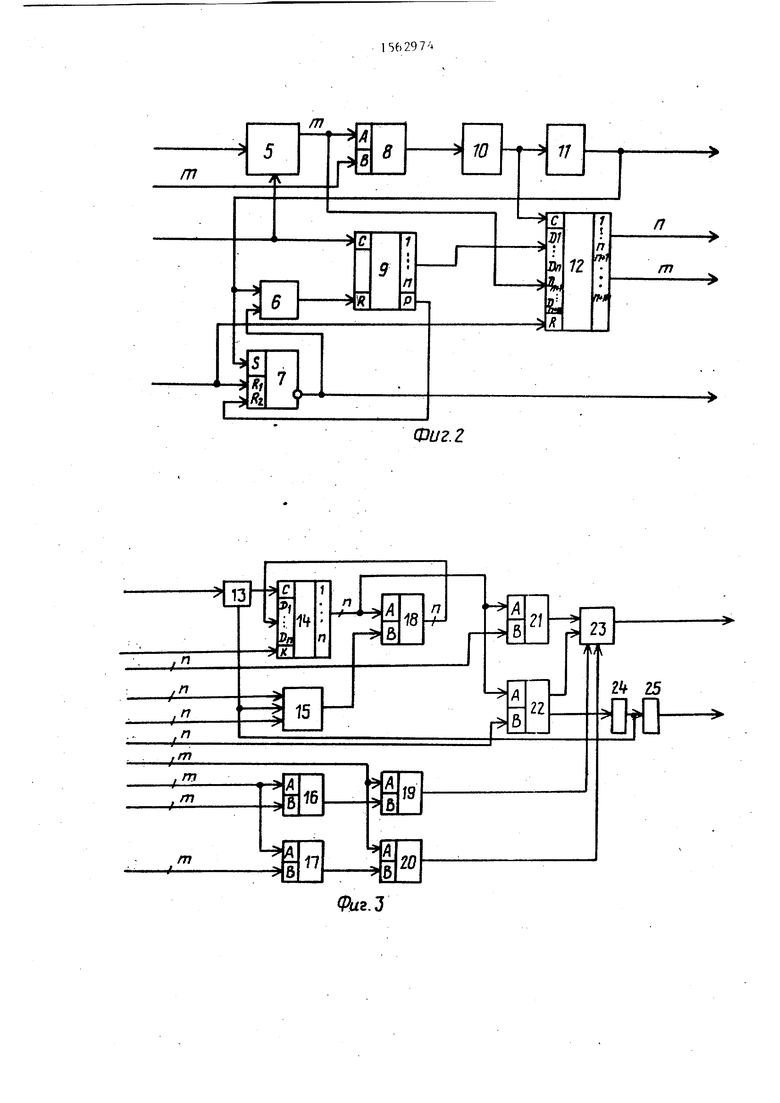

Вычислитель 2 работает следующим образом (фиг.З).

В исходном состоянии регистр 14 обнулЈн импульсом, поступающим на

25

30

)5

40

45

50

55

сумма кодов задержки между импульс ми S; Ј, + Ј 2+t . . . При достижении эт суммой значения Т на выходах соответственно Больше и Меньше1.1 компараторов 21 и 22 появ ляются сигналы уровня логической е ницы. Если и значение кода амплиту ды последнего импульса, поступающе по вторым информационным входам не превышает значений U .-Д ,, где Uj , Up соответственно коды мп туды первого и последнего импульсо причем код U1 - и t Формируется на вы дах сумматора 16, а код V- + и f на выходах сумматора 17, то на выхода компараторов 19 и 20 формируются сигналы логической единицы, а след вательно, и на выходе элемента И 2 тоже формируется сигнал логической единицы, который соответствует дек дированию в принимаемом сигнале 1временного интервала.

Возможен случай, когда при пост лении сигналов, отличных от ожидае мых кодовых, в регистре 14 появитс значение . + Дг. В этом случае н выходе Больше компаратора 22 фор руется сигнал логической единицы, фронту которого формирователь 24 формирует импульс, ,на время действ которого коммутатор 15 установится таким образом, что на его выходе б дет код, поступающий с третьих инф мационных входов (значение задержк второго импульса относительно перв импульса в процессе суммирования)„

Величина кода задержки с треть информационных входов поступает в

5

0

5

0

5

0

5

сумма кодов задержки между импульсами S; Ј, + Ј 2+t . . . При достижении этой суммой значения Т на - выходах соответственно Больше и Меньше1.1 компараторов 21 и 22 появляются сигналы уровня логической единицы. Если и значение кода амплитуды последнего импульса, поступающее по вторым информационным входам не превышает значений U .-Д ,, где Uj , Up соответственно коды мпли- туды первого и последнего импульсов, причем код U1 - и t Формируется на выходах сумматора 16, а код V- + и f на выходах сумматора 17, то на выходах компараторов 19 и 20 формируются сигналы логической единицы, а следовательно, и на выходе элемента И 23 тоже формируется сигнал логической единицы, который соответствует декодированию в принимаемом сигнале 1го временного интервала.

Возможен случай, когда при поступлении сигналов, отличных от ожидаемых кодовых, в регистре 14 появится значение . + Дг. В этом случае на выходе Больше компаратора 22 формируется сигнал логической единицы, по фронту которого формирователь 24 формирует импульс, ,на время действия которого коммутатор 15 установится таким образом, что на его выходе будет код, поступающий с третьих информационных входов (значение задержки второго импульса относительно первого импульса в процессе суммирования)„

Величина кода задержки с третьих информационных входов поступает в об9

18

ратном коде, и на выходе сумматора сформируется код разности (S--).

По заднему фронту импульса с выхода формирователя 24 величина (S.- ) запишется в регистр 14, а коммутатор 15 по окончании этого же импульса переключится в исходное состояние. По заднему фронту импульса с выхода формирователя 24 запустится формирователь 25 и с его выхода импульс сброса поступит на блок 3. При поступлении следующих импульсов и кодов процессы повторяются.

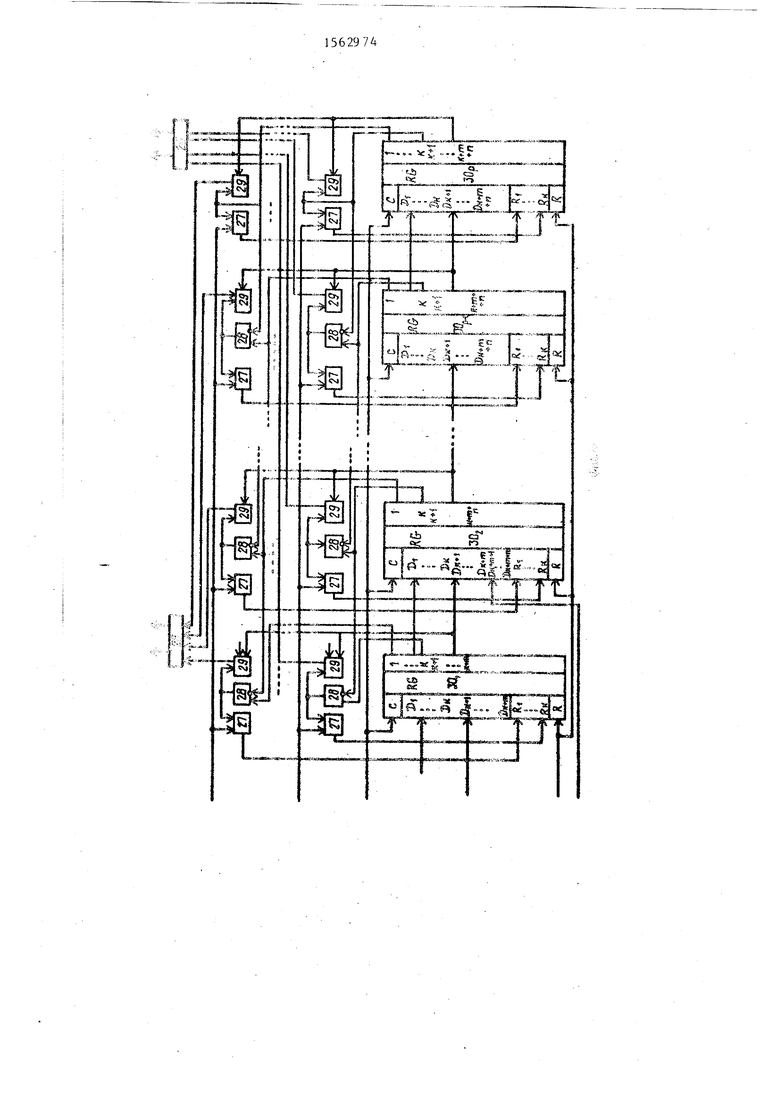

Блок 3 работает следующим образом (фиг.4).

В исходном состоянии (с момента времени t0 и до поступления первого импульса селектируемого сигнала) и;м- пульсом начального установа все регистры 30 обнулены.

При поступлении первого импульса в момент времени t на блок 1 снимается импульс установа и по заднему фронту тактового импульса в-разряды (k+1),..,(k+m) регистра 301 записывается значение кода амплитуды первого импульса, а в разряды 1,.,k - единицы, т.к. на входы П1,...,П , подана постоянная I. Состояние регистра 30-2 не изменяется, т.к. код задержки для первого импульса равен нулю. По поступлении второго импульса селектируемого сигнала по тактовому импульсу в разряды (k+l)м..(k+m) регистра 301 записывается значение его кода амплитуды, в разряды l}0,.k записывается 1, а в регистр 30 i записывается: в разряды 1,.. ,k - 1, в разряды (k+1),...,(k+m) значение кода амплитуды первого импульса, в разряды (k+m+1),,.,,(k+m+n) - значение кода задержки, второго импульса относительно первого. По поступлении последующих импульсов синхронизации происходит запись и сдвиг в регистрах 30 t,. в (30 j кодов параметров импульсов. На выходы блока 3, например, для первой позиции кода поступает (n+m)- разрядный код параметров первого импульса, что обеспечивается сравнением состояний первых разрядов предыдущего и последующего регистров 30, причем, только при комбинации 1 в первом разряде предшествующего регистра 30; и О в первом разряде последующего регистра 30 + 1 на выходе соответствующего элемента 28 1

явится уровень логической 1

запрета покото1562974

10

8

о а

10

15

20

25

30

35

40

45

50

55

рый разрешит прохождение (т+п)-р.т рядиого кода через коммутатор 29, и эпемент ИЛИ 26. При поступлении им- пульсоя сброса на установочные входы, например, на первый установочный вход от вычислителя 21 при S1 T1+Z3,

IT

импульс сброса чероз элемент 27 поступит на вход Rf регистра 30 j

и

разряд в нулеустановнт его первый вое состояние.

На выходе элемента И 27f установится сигнал О, а на выхо де элемента 281 /;(j запрета установится 1, которая разрешит прохождение кода параметров второго импульса с выхода регистра 30 t череэ коммутатор 29 ,, (j-fi и элемент ИЛИ 2ht на выходы блока 3. Таким образом, при поступлении кодов параметров импульсов и импульсов синхронизации блок 3 обеспечивает выдачу на каждый из своих k выходов кода первого поступившего импульса. По поступлении импульсов сброса код на выходах блока 3 выдается для второго и последующих импульсов в зависимости от количества импульсов сброса для каждого из первых, вторых выходов. При сдвиге (записи) кодов параметров первого анализируемого импульса в регистр 30 р значение кодов параметров импульсов из этого регистра 30 выдается через коммутаторы 29 t ,.„, о..,24 которые управляются значением (наличием) 1 в разрядах 1,...,k регистра 30р.

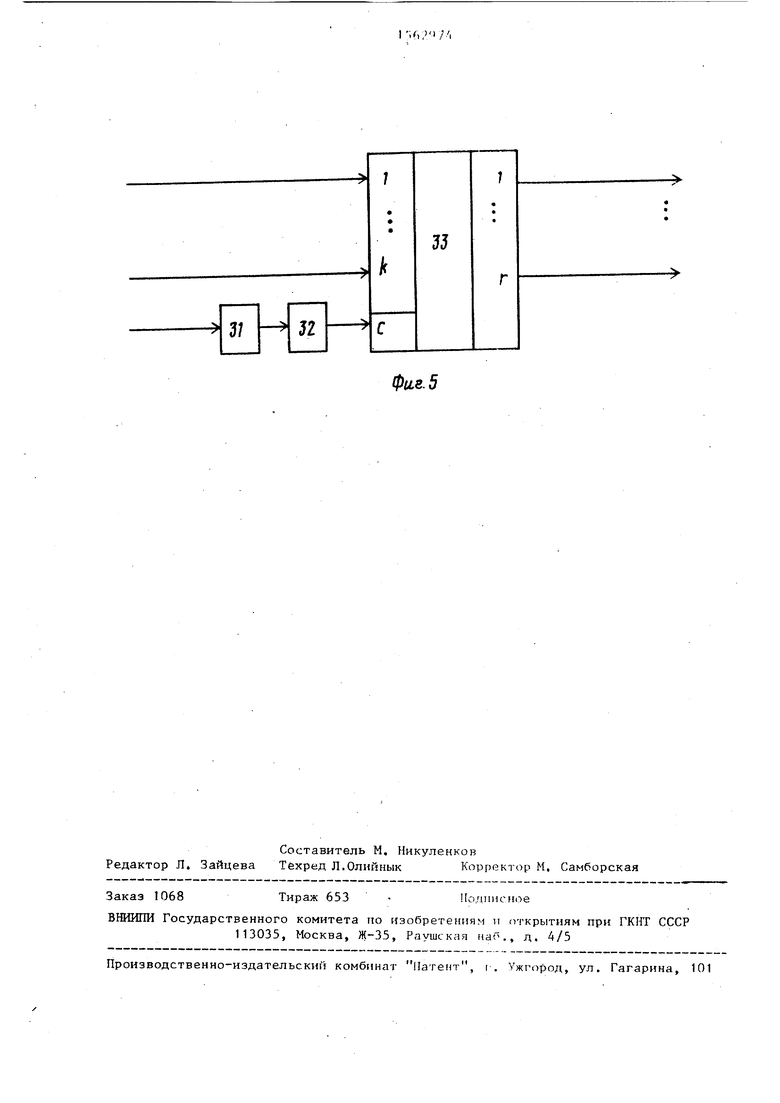

Блок 4 временной селекции работает следующим образом (фиг.5),

При поступлении на тактовый вход импульса синхронизации формирователь 31 формирует импульс, длительность которого выбирается несколько болыче времени выполнения операций и задержки в вычислителях 2. По заднему фронту импульса с выхода формирователя 31 запускается формирователь 32, определяющий длительность выходного сигналя, импульс с выхода которого оступпет на стробирующий вход дешифратора 33. При наличии на информационных входах дешифратора 33 сигналов с выходов вычислителей 2 на выходе деши(Ьрчтора 33, соответствующем дешиАрирч рмой кодовой комбинации, формируется пчпч-лъс.

Селектор M IISльсно-временного кода имеет рап и-р ииые функциональные возможности пи сравнению с известным

личных групп импульсно-временных кодов обеспечивается сменой значений установочных сигналов

и о р м у л а изобретения

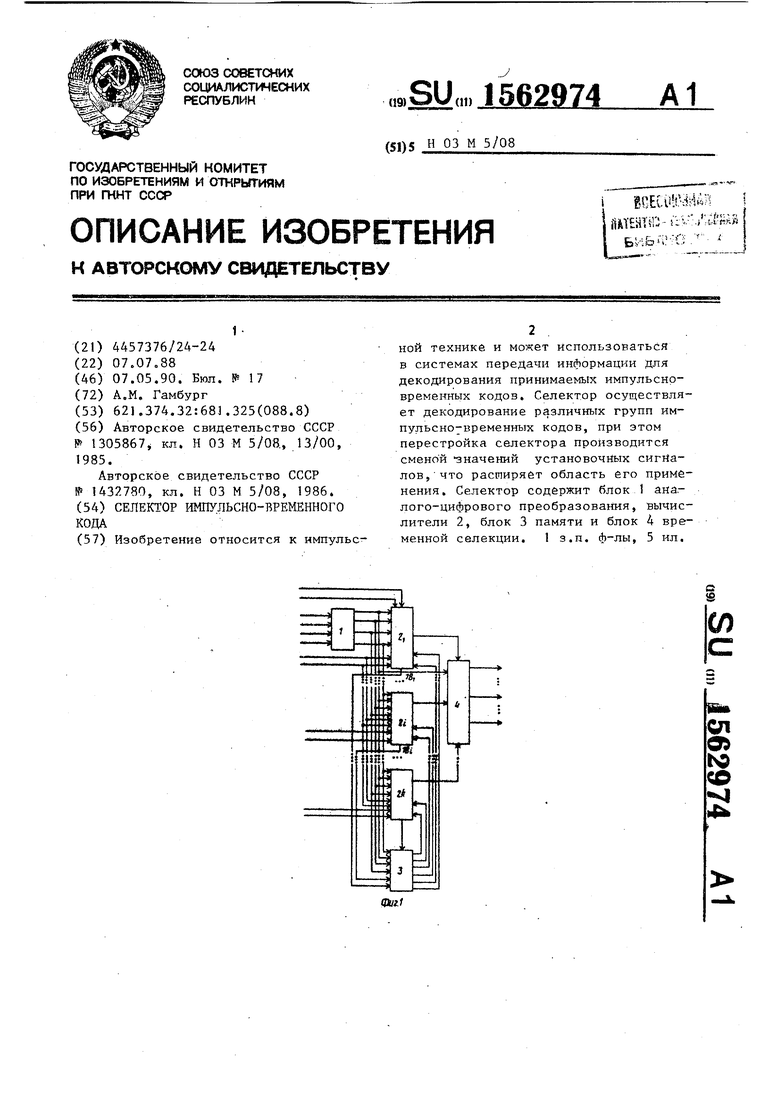

1. Селектор импульсно-временного к|ода, содержащий блок аналого-цифрового преобразования, информационный вход которого является информационным феодом селектора, и блок временной с елекции, выходы которого являются выходами селектора, отличаю- mj и и с я тем, что, с целью расши- р|ения области применения селектора за счет возможности перестройки его временной базы и позиций импульсов кода, в него введены блок памяти и вычислители, первые и вторые входы уставок вычислителей являются соответственно первыми и вторыми входами уставок селектора, одноименные тре- т)ьи и четвертые входы уставок вычислителей объединены соответственно и являются третьими и четвертыми входами уставок селектора, тактовый вход, входы уставки и вход начальной установки блока аналого-цифрового преобразования являются соответственно тактовым входом, пятыми входами уставок и входом начальной установки селектора, первый выход блока аналого- цифрового преобразования соединен с тактовыми входами вычислителей, блока временной селекции и блока памяти, вторые и третьи выходы блока аналого-цифрового преобразования соединены с одноименными соответственно первыми и вторыми информационными входами вычислителей и блока памяти, четвертый выход блока аналого- цифрового преобразования соединен с установочными входами вычислителей и первым установоч гым входом блока памяти, первые выходы вычислителей со-единены с одноименными вторыми ус- танбвочными входами блока памяти, первые и вторые выходы которого соединены соответственно с одноименными третьими информационными входами и одноименными пятыми входами уставок

телей соединены с одноименными информационными входами блока временной селекции

2. Селектор по п. 1, отличающийся тем, что вычислитель содержит элемент ИПИ, регистр, коммутатор, сумматоры, компараторы, элемент И и формирователи импульсов, выход первого формирователя импульсов соединен с входом второго формирователя импульсов, управляющим входом 5 коммутатора и первым РХОДОМ элемента ИЛИ, выход которого соединен с тактовым входом регистра, выходы регистра соединены с одноименными первыми входами первого, второго компара- 0 торов и первого сумматора, выходы коммутатора соединены с одноименными вторыми входами первого сумматора, выходы которого соединены с одноименными информационными входами регист- 5 ра, выходы второго и третьего сумматоров соединены с одноименными первыми входами соответственно третьего и четвертого компараторов, выходы первого, третьего, четвертого компа- 0 раторов и первый выход второго компаратора соединены соответственно с первым, вторым, третьим и четвертым входами элемента И, второй выход второго компаратора соединен с входом с первого Формирователя импульсов, второй вход элемента ИЛИ, вход установки в О регистра, первые информационные входы коммутатора, вторые входы третьего и четвертого компараторов, 0 вторые информационные входы коммутатора, вторые входы второго, первого компараторов, первые входы второго, третьего сумматоров и вторые входы второго и третьего сумматоров квляют- 5 ся соответственно тактовым входом, установочным входом, первыми, вторыми, третьими информационными входа- ми, первыми, вторыми, третьими и четвертыми входами уставок вычисли- 0 теля, выходы второго формирователя импульсов и элемента И являются соответственно первым и вторым выходами вычислителя.

гпф

| название | год | авторы | номер документа |

|---|---|---|---|

| Вероятностный мажоритарный декодер | 1986 |

|

SU1396282A1 |

| Устройство для формирования изображения на экране телевизионного приемника | 1987 |

|

SU1474727A1 |

| Преобразователь угла поворота вала в код | 1988 |

|

SU1522408A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| Кольцевая система громкоговорящей связи с временным разделением каналов | 1990 |

|

SU1699359A3 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| УСТРОЙСТВО МОНИТОРИНГА ИНФОРМАЦИОННОГО ТРАФИКА | 2021 |

|

RU2768543C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2004 |

|

RU2281549C1 |

| Многокоординатное устройство для управления | 1989 |

|

SU1777121A2 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

Изобретение относится к импульсной технике и может использоваться в системах передачи информации для декодирования принимаемых импульсно-временных кодов. Селектор осуществляет декодирование различных групп импульсно-временных кодов, при этом перестройка селектора производится сменой значений установочных сигналов, что расширяет область его применения. Селектор содержит блок 1 аналого-цифрового преобразования, вычислители 2, блок 3 памяти и блок 4 временной селекции. 1 з.п. ф-лы, 5 ил.

V/.62%1

Фиг. 5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Декодер Гамбурга | 1986 |

|

SU1432780A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-05-07—Публикация

1988-07-07—Подача