Изобретение относится к вычислительной технике, а именно к устройствам контроля правильности кода программ.

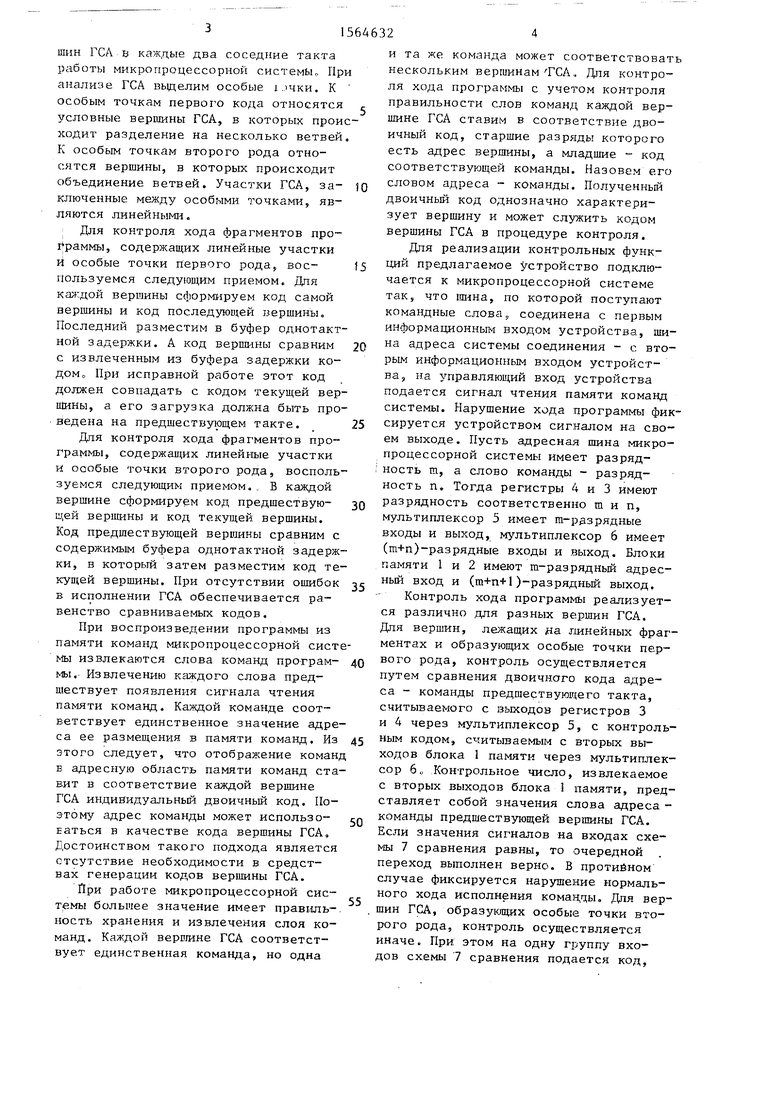

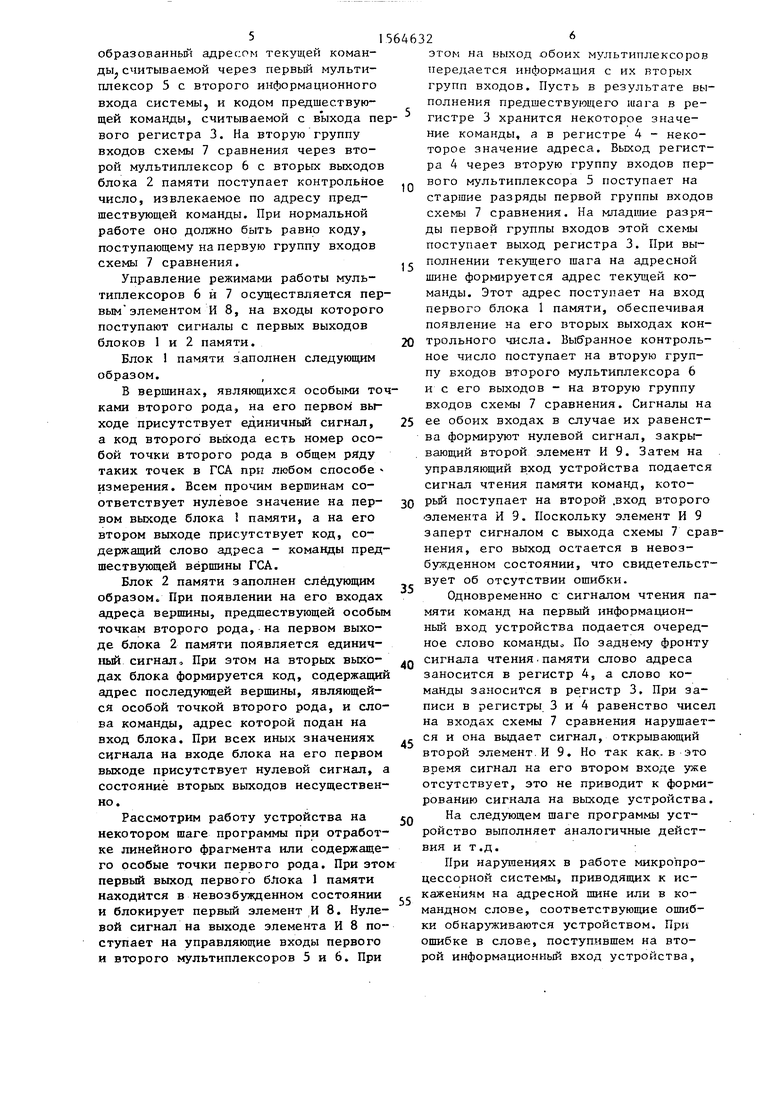

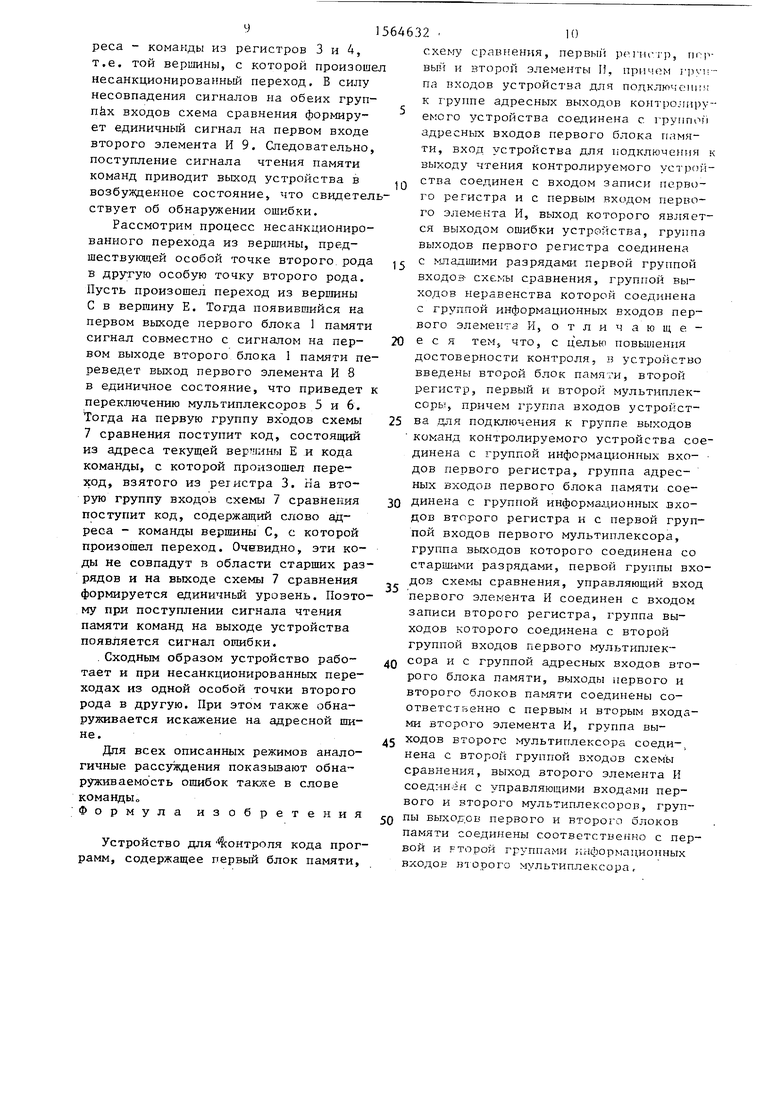

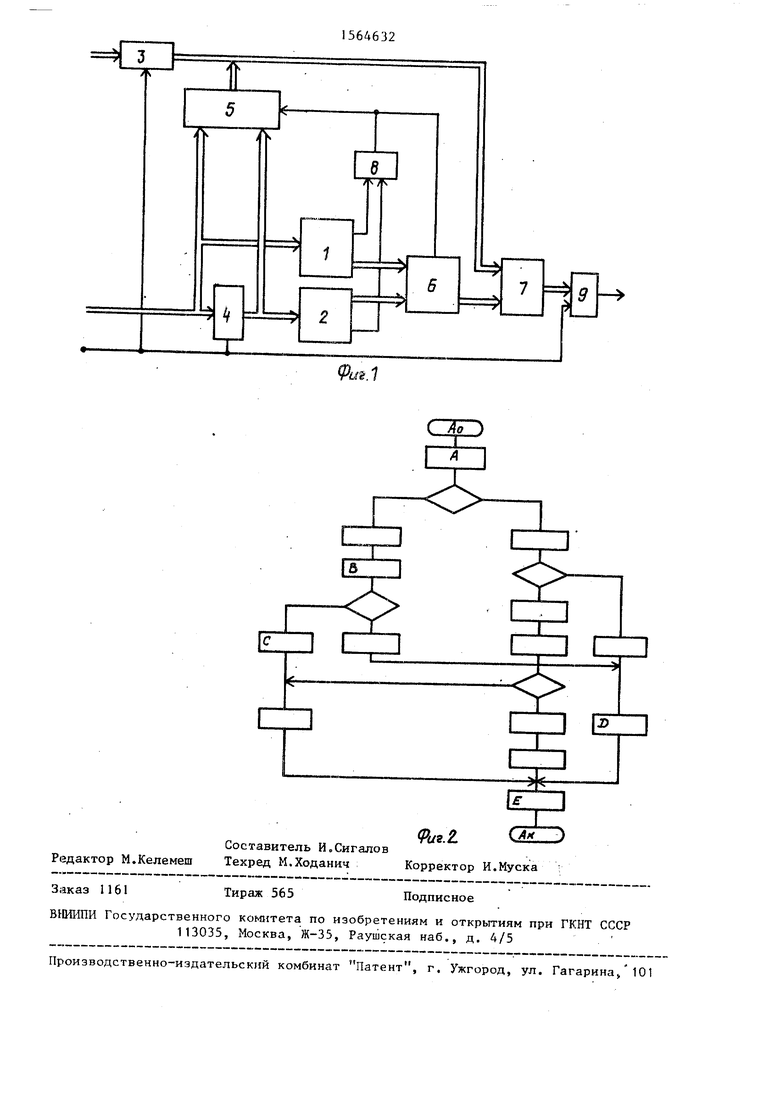

Цель изобретения - повышение достоверности.На фиг.1 изображена структурная схема устройства для контроля кода программ; на фиг.2 - пример графсхемы алгоритма программы.

Устройство содержит первый 1 и второй 2 блоки памяти, первый 3 и второй 4 регистры, первый 5 и второй 6 мультиплексоры, схему 7 сравнения, первый 8 и второй 9 элементы И.

Устройство работает следующим образом.

известно, что любая программа может быть представлена в вир, графсхемы ее алгоритма (ГСА). Пример ГСА приведен на фиг.2, где А0 - начальная вершина, А., - конечная вершина. Процесс исполнения программы выражается в движении по ГСА из А0 и Ak по одной из возможных ветвей.

Поставим каждой вершине ГСА в соответствие некоторое двоичное число. Причем так, что полученное множество двоичных чисел не имеет одинаковых элементов и каждой вершине соответствует отличное от других значение двоичного кода. В этом случае исполнение программы сопровождается сменой описанных кодов, а в силу неповторяемости кодов такая смена происходит на каждом шаге программы. Поэтому для контроля хода программы достаточно проконтролировать смену кодов верЬп

Ьэ 4ь о& со to

шин ГСЛ в каждые два соседние такта работы микропроцессорной системы,, При анализе ГСА выделим особые i чки. К особым точкам первого кода относятся условные вершины ГСА, в которых происходит разделение на несколько ветвей, К особым точкам второго рода относятся вершины, в которых происходит объединение ветвей. Участки ГСА, за ключенныс между особыми точками, являются линейными.

Для контроля хода фрагментов программы, содержащих линейные участки И особые точки первого рода, вое- Пользуемся следующим приемом. Для каждой вершины сформируем код самой вершины и код последующей вершины. Последний разместим в буфер однотакт- ной задержки. А код вершины сравним с извлеченным из буфера задержки кодом При исправной работе этот код должен совпадать с кодом текущей вершины, а его загрузка должна быть проведена на предшествующем такте.

Для контроля хода фрагментов программы, содержащих линейные участки И особые точки второго рода, воспользуемся следующим приемом. В каждой вершине сформируем код предшествую- щей вершины и код текущей вершины. Код предшествующей вершины сравним с содержимым буфера однотактной задержки, в который затем разместим код текущей вершины. При отсутствии ошибок в исполнении ГСА обеспечивается равенство сравниваемых кодов.

При воспроизведении программы из памяти команд микропроцессорной системы извлекаются слова команд програм- мы. Извлечению каждого слова предшествует появления сигнала чтения памяти команд. Каждой команде соответствует единственное значение адреса ее размещения з памяти команд. Из этого следует, что отображение команд в адресную область памяти команд ставит в соответствие каждой вершине ГСА инцинидуалышй двоичный код. Поэтому адрес команды может использо- ЕЭТЬСЯ в качестве кода вершины ГСА, Достоинством такого подхода является стсутствие необходимости в средствах генерации кодов вершины ГСА.

При работе микропроцессорной системы большее значение имеет правильность хранения и извлечения слоя команд. Каждой вершине ГСА соответствует единственная команда, но одна

5 0

5

и та же команда может соответствовать нескольким вершинам ТСА, Для контроля хода программы с учетом контроля правильности слов команд каждой вершине ГСА ставим в соответствие двоичный код, старшие разряды которого есть адрес вершины, а младшие - код соответствующей команды. Назовем его словом адреса - команды. Полученный двоичньй код однозначно характеризует вершину и может служить кодом вершины ГСА в процедуре контроля.

Для реализации контрольных функций предлагаемое устройство подключается к микропроцессорной системе так, что шина, по которой поступают командные слова4 соединена с первым информационным входом устройства, шина адреса системы соединения - с вторым информационным входом устройства, на управляющий вход устройства подается сигнал чтения памяти команд системы. Нарушение хода программы фиксируется устройством сигналом на своем выходе. Пусть адресная шина микропроцессорной системы имеет разрядность т, а слово команды - разрядность п. Тогда регистры 4 и 3 имеют разрядность соответственно тип, мультиплексор 5 имеет га-разрядные входы и выход, мультиплексор 6 имеет (т+п)-разрядные входы и выход. Блоки памяти 1 и 2 имеют m-разрядный адресный вход и (т+п+1)-разрядный выход.

Контроль хода программы реализуется различно для разных вершин ГСА, Для вершин, лежащих да линейных фрагментах и образующих особые точки первого рода, контроль осуществляется путем сравнения двоичного кода адреса - команды предшествующего такта, считываемого с выходов регистров 3 и 4 через мультиплексор 5, с контрольным кодом, считываемым с вторых выходов блока 1 памяти через мультиплексор 6„ Контрольное число, извлекаемое с вторых выходов блока i памяти, представляет собой значения слова адреса - команды предшествующей вершины ГСА. Если значения сигналов на входах схемы 7 сравнения равны, то эчередной переход выполнен верно. В протибном случае фиксируется нарушение нормального хода исполнения команды. Для вершин ГСА, образующих особые точки второго рода, контроль осуществляется иначе. При этом на одну группу входов схемы 7 сравнения подается код,

образованный адресом текущей коман- ды считываемой через первый мультиплексор 5 с второго информационного входа системы, и кодом предшествующей команды, считываемой с выхода первого регистра 3. На вторую группу входов схемы 7 сравнения через второй мультиплексор 6 с вторых выходов блока 2 памяти поступает контрольное число, извлекаемое по адресу предшествующей команды. При нормальной работе оно должно быть равно коду, поступающему на первую группу входов схемы 7 сравнения.

Управление режимами работы мультиплексоров 6 и 7 осуществляется первым элементом И 8, на входы которого поступают сигналы с первых выходов блоков 1 и 2 памяти.

Блок 1 памяти заполнен следующим образом.

В вершинах, являющихся особыми точками второго рода, на его первом выходе присутствует единичный сигнал, а код второго выхода есть номер особой точки второго рода в общем ряду таких точек в ГСА при любом способе « измерения. Всем прочим вершинам соответствует нулевое значение на первом выходе блока 1 памяти, а на его втором выходе присутствует код, содержащий слово адреса - команды предшествующей вершины ГСА.

Блок 2 памяти заполнен следующим образом. При появлении на его входах адреса вершины, предшествующей особым точкам второго рода, на первом выходе блока 2 памяти появляется единичный сигнал, При этом на вторых выходах блока формируется код, содержащий адрес последующей вершины, являющейся особой точкой второго рода, и слова команды, адрес которой подан на вход блока. При всех иных значениях сигнала на входе блока на его первом выходе присутствует нулевой сигнал, а состояние вторых выходов несущественно.

Рассмотрим работу устройства на некотором шаге программы при отработке линейного фрагмента или содержащего особые точки первого рода. При этом первый выход первого блока 1 памяти находится в невозбужденном состоянии и блокирует первый элемент И 8. Нулевой сигнал на выходе элемента И 8 поступает на управляющие входы первого и второго мультиплексоров 5 и 6. При

0

5

0

5

0

5

0

5

0

5

этом на выход обоих мультиплексоров передается информация с их вторых групп входов. Пусть в результате выполнения предшествующего шага в регистре 3 хранится некоторое значение команды, а в регистре 4 - некоторое значение адреса. Выход регистра 4 через вторую группу входов первого мультиплексора 5 поступает на старшие разряды первой группы входов схемы 7 сравнения. На младшие разряды первой группы входов этой схемы поступает выход регистра 3. При выполнении текущего шага на адресной шине формируется адрес текущей команды. Этот адрес поступает на вход первого блока 1 памяти, обеспечивая появление на его вторых выходах контрольного числа. Выбранное контрольное число поступает на вторую группу входов второго мультиплексора 6 и с его выходов - на вторую группу входов схемы 7 сравнения. Сигналы на ее обоих входах в случае их равенства формируют нулевой сигнал, закрывающий второй элемент И 9. Затем на управляющий вход устройства подается сигнал чтения памяти команд, который поступает на второй .вход второго элемента И 9. Поскольку элемент И 9 заперт сигналом с выхода схемы 7 сравнения, его выход остается в невозбужденном состоянии, что свидетельствует об отсутствии ошибки.

Одновременно с сигналом чтения памяти команд на первый информационный вход устройства подается очередное слово команды По заднему фронту сигнала чтения памяти слово адреса заносится в регистр 4, а слово команды заносится в регистр 3. При записи в регистры 3 и 4 равенство чисел на входах схемы 7 сравнения нарушается и она выдает сигнал, открывающий второй элемент И 9. Но так как. в это время сигнал на его втором входе уже отсутствует, это не приводит к формированию сигнала на выходе устройства.

На следующем шаге программы устройство выполняет аналогичные действия и т.д.

При нарушениях в работе микропроцессорной системы, приводящих к искажениям на адресной шине или в командном слове, соответствующие ошибки обнаруживаются устройством. При ошибке в слове, поступившем на второй информационный вход устройства,

на вход блока 1 памяти поступит неверный адрес текущей вершины ГСА. При этом с его вторых выходов на вторую группу входов схемы сравнения поступит код, не совпадающий с содержимым регистров 3 и 4 „ Например, при ошибочном переходе из А в С вместо А в В (фиг.2) на вторых выходах первого блока 1 памяти появится слово адреса - команды, соответствующей вершине С. Вместе с тем в регистрах 3 и 4 хранится слово адреса - команды, соответствующее .вершине А. Поэтому на выходе схемы 7 сравнения формируется единичный сигнал,, поступающий на элемент И 9. При поступлении сигнала чтения памяти команд он приходит на второй вход элемента И 9 и открывает его, тем самым возбуждается выход устройства, что свидетельствует о наличии ошибки.

При возникновении ошибки на первом информационном входе устройства поступивший код команды фиксируется в регистре 3 задним фронтом сигнала чтения памяти команды. На следующем такте на второй информационный вход устройства поступает новое значение

в регистре 3 задним фронтом того же сигнала чтения памяти команд.

Вслед за этим на второй информационный вход устройства поступает а рес вершины, являющейся особой точкой второго рода. Он поступает на вход первого блока 1 памяти, первый выход которого при этом возбуждает

JQ ся в единичное состояние. Это приво дит к появлению единичного сигнала выходе первого элемента И 8. Данный сигнал поступает на управляющие вхо ды первого 5 и второго 6 мультипл

J5 соров, в результате чего на их выхо подается информация с первых входов При этом на первую группу входов сх мы 7 сравнения поступает сигнал, ст шие разряды которого образованы адр

2Q сом текущей веошины, а младшие - ко мандным словом предшествующей верши На вторую группу входов схемы 7 сра нения поступает сигнал с второго вы хода блока 2 памяти. При отсутствии

25 ошибок сигналы на обоих группах вхо дов схемы 7 сравнения совпадают, а выходе схемы сравнения появляется н левой сигнал, который передается на первый вход второго элемента И 9 и

текущего адреса. При этом извлекаемое 30 блокирует его. Поэтому поступление

46328

в регистре 3 задним фронтом того же сигнала чтения памяти команд.

Вслед за этим на второй информационный вход устройства поступает адрес вершины, являющейся особой точкой второго рода. Он поступает на вход первого блока 1 памяти, первый выход которого при этом возбуждаетJQ ся в единичное состояние. Это приводит к появлению единичного сигнала на выходе первого элемента И 8. Данный сигнал поступает на управляющие входы первого 5 и второго 6 мультиплекJ5 соров, в результате чего на их выходы подается информация с первых входов, При этом на первую группу входов схемы 7 сравнения поступает сигнал, старшие разряды которого образованы адре-

2Q сом текущей веошины, а младшие - командным словом предшествующей вершины. На вторую группу входов схемы 7 сравнения поступает сигнал с второго выхода блока 2 памяти. При отсутствии

25 ошибок сигналы на обоих группах входов схемы 7 сравнения совпадают, а на выходе схемы сравнения появляется нулевой сигнал, который передается на первый вход второго элемента И 9 и

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Устройство для контроля хода программ | 1987 |

|

SU1508215A1 |

| Устройство для программного управления технологическим оборудованием | 1987 |

|

SU1423982A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Устройство для программного управления технологическим оборудованием | 1988 |

|

SU1638707A1 |

| УСТРОЙСТВО СОРТИРОВКИ ИНФОРМАЦИИ | 1993 |

|

RU2034327C1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

| СИСТЕМА ДЛЯ ОБРАБОТКИ КОМПОНЕНТ ПРОГРАММ И СХЕМА УПРАВЛЕНИЯ ПАМЯТЬЮ ДЛЯ ТРАНСПОРТНОГО ПРОЦЕССОРА | 1995 |

|

RU2145728C1 |

| Устройство для исследования графов | 1984 |

|

SU1238099A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

Изобретение относится к вычислительной технике, а именно к средствам контроля устройств управления. Целью изобретения является повышение достоверности контроля. Устройство содержит блоки 1 и 2 памяти, регистры 3 и 4, мультиплексоры 5 и 6, схему 7 сравнения и элементы И 8 и 9. При этом в устройстве каждой вершине графсхемы алгоритма ставится в соответствие свой индивидуальный признак, что позволяет свести контроль хода программы к сопоставлению признаков каждых двух соседних вершин и обеспечить тем самым гарантированное выявление всех одиночных ошибок на шине адреса и в слове команды на линейных участках программ и при переходе к точкам схождения ветвей графсхемы алгоритма программы. 2 ил.

по вторым выходам первого блока 1 памяти контрольное слово в области младших разрядов не совпадает с содержимым регистра 3„ Такое расхождение приведет к появлению на выходе устройства сигнала ошибки по описанной схеме. Следовательно, указанные ошибки обнаруживаются,,

Выше описана работа устройства на линейных участках программы или участках, содержащих особые точки первого рода.

Пусть программа достигла вершины, предшествующей особой точке второго рода. При этом адрес вершины фиксируется в регистре 4 задним фронтом сигнала чтения памяти команд. Сигнал с выхода регистра 4 поступает на вход блока 2 памяти, обеспечивая появление на его первом выходе единичного сигнала. Данный сигнал поступает на второй вход первого элемента И 8. На втором выходе бпока 2 памяти появляется код, состоящий из адреса следующей иершины ГСА и слова команды текущеД нершины. Этот код поступает на первую группу входов второго мультиплексора (). Код командного слова фиксируется

5

0

сигнала чтения памяти команд не приводит к возбуждению выхода устройства. II этому сигналу адрес текущей команды и ее код заносятся соответственно в регистры 4 и 3. На первом выходе второго блока 2 памяти появляется нулевой сигнал и, поступая на второй вход первого элемента И 8, блокирует его. Это приводит к переключению первого 5 и второго 6 мультиплексоров, на выходы которых теперь подаются их вторые входы. Дальнейшая работа устройства аналогична описанной.

Рассмотрим процесс обнаружения 5 ошибки на шине адреса, приводящей к несанкционированному переходу из любой вершины линейного участка в особую точку второго рода (А - Е фиг.2). Появляющийся при этом единичный сигнал на первом выходе блока 1 памяти не приводит к возбуждению выхода первого элемента И 8, так как на втором его входе присутствует блокирующий сигнал. Поэтому на вторую группу входов схемы 7 сравнения поступает слово адреса - команды текущей особой то«- ки второго рода с вторых выходов блока 1 памяти. На первую группу входов схемы 7 сравнения поступает слово ад0

5

реса - команды из регистров 3 и 4, т.е. той вершины, с которой произоше несанкционированный переход, В силу несовпадения сигналов на обеих группах входов схема сравнения формирует единичный сигнал на первом входе второго элемента И 9. Следовательно, поступление сигнала чтения памяти команд приводит выход устройства в возбужденное состояние5 что свидетелствует об обнаружении ошибки.

Рассмотрим процесс несанкционированного перехода из вершины, предшествующей особой точке второго рода в другую особую точку второго рода. Пусть произошел переход из вершины С в вершину Е. Тогда появившийся на первом выходе первого блока 1 памяти сигнал совместно с сигналом на первом выходе второго блока 1 памяти переведет выход первого элемента И 8 в единичное состояние, что приведет переключению мультиплексоров 5 и 6. Тогда на первую группу входов схемы 7 сравнения поступит код, состоящий из адреса текущей вер чины Е и кода команды, с которой произошел переход, взятого из регистра 3. На вторую группу входов схемы 7 сравнения поступит код, содержащий слово адреса - команды вершины С, с которой произошел переход. Очевидно, эти коды не совпадут в области старших разрядов и на выходе схемы 7 сравнения формируется единичный уровень. Поэтому при поступлении сигнала чтения памяти команд на выходе устройства появляется сигнал ошибки.

Сходным образом устройство работает и при несанкционированных переходах из одной особой точки второго рода в другую. При этом также обнаруживается искажение на адресной шине.

Для всех описанных режимов аналогичные рассуждения показывают обна- руживаемость ошибок также в слове

команды

Формула изобретения

Устройство для контроля кода программ, содержащее первый блок памяти,

10

15

20

25

схему сравнения, первый prnu ip, гп р выи и второй элементы И, призом i u i па входов устройства для подключен к группе адресных выходов контролируемого устройства соединена с ipvunon адресных входов первого блока памяти, вход устройства для подключения к выходу чтения контролируемого уст рон- ства соединен с входом записи первого регистра и с первым входом первого элемента И, выход которого является выходом ошибки устройства, группа выходов первого регистра соединена с младшими разрядами первой группой входов- схег;ы сравнения, группой выходов неравенства которой соединена с группой информационных входов первого элемента И, отличающееся тем, что, с целью повышения достоверности контроля, в устройство введены второй блок памя и, второй регистр, первый и второй мультиплексоры, причем группа входов устройства плч подключения к группе выходов команд контролируемого устройства соединена с группой информационных входов первого регистра, группа адресных входов первого блока памяти соединена с группой информационных входов второго регистра и с первой группой входов первого мультиплексора, группа выходов которого соединена со старшими разрядами, первой группы входов схемы сравнения, управляющий вход первого элемента И соединен с входом записи второго регистра, группа выходов которого соединена с второй группой входов первого мультиплексора и с группой адресных входов второго блока памяти, выходы первого и второго блоков памяти соединены соответственно с первым и вторым входами второго элемента И, группа выходов второго мультиплексора соеди-, нена с второй группой входов схемы сравнения, выход второго элемента И соедчн н с управляющими входами первого и второго мультиплексоров, группы выходов первого и BTOpoin блоков памяти соединены соответственно с первой и рторои группами ьпформационных входов второго мультиплексора.

30

35

40

45

50

JT I

Редактор М.Келемеш

к

г.Ј СЖИ-)

Составитель И.Сигалов

Техред М.Ходанич Корректор И.Муска

Заказ 1161

Тираж 565

ВШИЛИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

СЖР

ПП

Ј

S с

Г

ПП E

Подписное

| Микропрограммное устройство управления | 1984 |

|

SU1180888A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР It 1300479, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-05-15—Публикация

1988-06-14—Подача