ел

2

ОЭ 00

со

Изобретение относится к вычислительной технике и предназначено для реализации простого взаимодействия с оперативной памятью микропроцессорны систем.

Известно устройство для адресации оперативной памяти (авторское свидетельство СССР № 401997, кл. G 06 F 9/00 9 1971), которое позволяет адресовать данные и команды, хранящиеся в оперативной памяти, однако требует больших аппаратурных затрат для реализации.

Цель изобретения - уменьшение аппаратурных затрат„

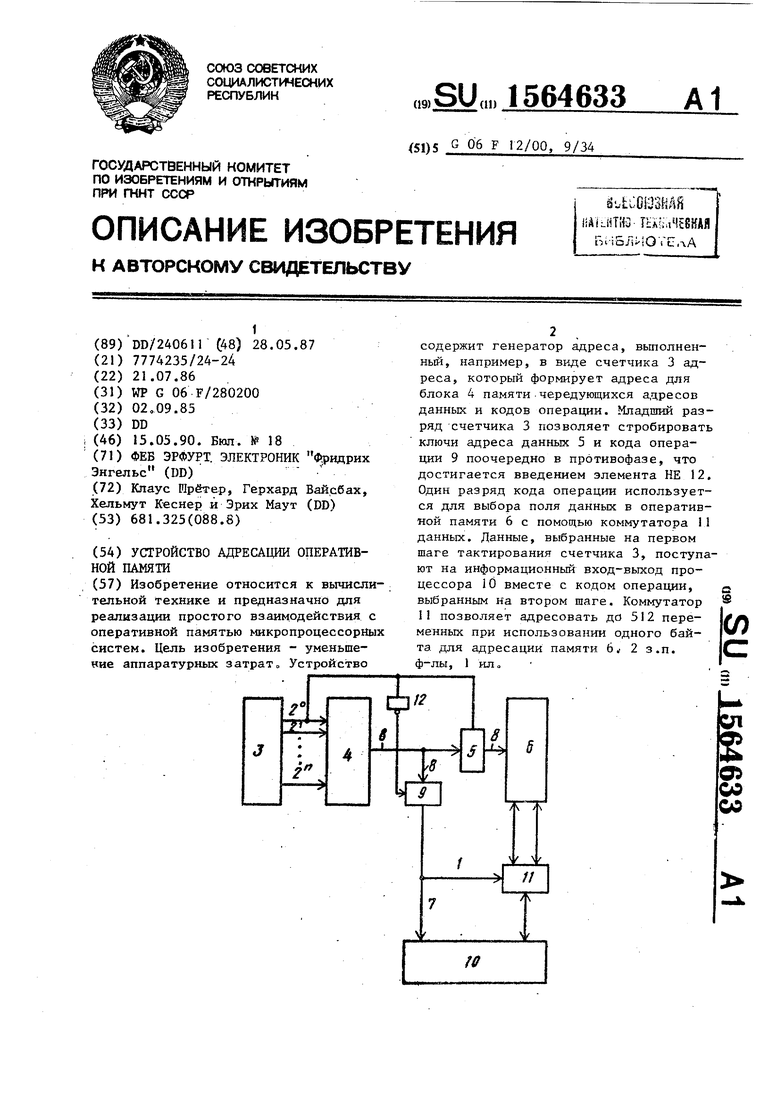

На чертеже схематически представлено включение устройства в состав системы, содержащей, по крайней мере, процессор 10 и оперативную память 6. Устройство содержит генератор адреса, который может быть выполнен в виде счетчика 3 адреса, блок 4 памяти чередующихся адресов данных И кодов операции, ключ 5 адреса данных, ключ 9 кода операции, коммутатор 11 данных и элемент НЕ 12. Цифрами у пиний связи на чертеже обозначена разрядность шин. Цепи тактирования и записи чтения, а также схемы буфери- рования сигналов на чертеже не показаны и определяются конкретной реализацией изобретения.

В блоке 4 записываются чередующиеся адреса данных и кодов операций, Причем один разряд кода операции используется для кодирования поля данных, считываемого или записываемого в памяти 6, Этот разряд используется для управления коммутатором 31 данных. В предлагаемом варианте реали зации ключи 5 и 9 работают поочередно в противофазе, что достигается подключением управляющих входов ключей непосредственно (для ключа 5) и через элемент НЕ 12 (для ключа 9) к выходу младшего разряда счетчика 3 ад ;эеса„

Устройство работает следующим образом.W

На первом шаге из блока 4 считывается первый байт - адрес данных, который через открытый ключ 5 передается на вход адреса оперативной памяти 6. В это время ключ 9 заблокиро- 5 нан инверсным управляющим сигналом с выхода счетчика 3 и первый байт не может попасть в процессор 10.

5

10

5

0

На втором шаге из блока 4 считывается второй байт - код операции, который в связи с изменением значения младшего разряда счетчика 3 передается через открытый ключ 9 в процессор 10 и одним разрядом управляет коммутатором 11. На информационный вход- выход процессора 10 поступают данные, содержащиеся в памяти 6 по указанному на первом шаге адресу Выбор поля данных осуществляется коммутатором 1 S .

Таким образом, за два обращения к памяти 6 в процессоре 10 появляются код операции и данные, подлежащие обработке.

На третьем шаге результат обработки может быть записан из процессора 10 в память 6. При этом для хранения входных и выходных переменных может использоваться первое поле данных в памяти 6, а для хранения промежуточных значений - второе поле данных.

В результате за два обращения к памяти оказывается возможным адресовать до 512 переменных в памяти 6 и сформировать код операции при использовании восьмиразрядного блока 4.

рмула изобретения

1. Устройство адресации оперативной памяти, содержащее генератор адреса, ключ адреса данных и ключ кода операции, отличающееся тем, что, с целью уменьшения аппаратурных затрат, оно содержит блок памяти чередующихся адресов данных и кодов операции, адресный вход и выход которого соединены с выходом генератора адреса и с поразрядно объединенными информационными входами ключей адреса данных и кода операции соответственно, двунаправленный коммутатор данных, первый, второй и третий информационные входы-выходы которого являются входами-выходами устройства для подключения к информационному входу-выходу процессора и к первому и второму информационным входам-выходам оперативной памяти соответственно, выходы ключей адреса данных и кода операции являются выходами адреса данных и кода операции- устройства соответственно, управляющий вход двунаправленного коммутатора данных

515646336

подключен к соответствующему разрядудинен с управляющим входом ключа ковыхода ключа кода операции.да операции.

2. Устройство по п.1, о т л и чающееся тем, что оно содер- 3. Устройство по пп. 1 и 2, о т жит элемент НЕ, вход которого являет-личающееся тем, что генерася управляющим входом устройства итор адреса выполнен в виде счетчика,

соединен с управляющим входом ключавыход младшего разряда которого соедиадреса данных, выход элемента НЕ сое-нен с управляющим входом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для управления каналами | 1979 |

|

SU877519A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Процессор с микропрограммным управлением | 1975 |

|

SU525956A1 |

| Устройство для связи процессора с оперативной памятью | 1978 |

|

SU750489A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1987 |

|

SU1587521A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1985 |

|

SU1260970A2 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Устройство для выполнения быстрого преобразования Фурье | 1980 |

|

SU955085A1 |

Изобретение относится к вычислительной технике и предназначено для реализации простого взаимодействия с оперативной памятью микропроцессорных систем. Цель изобретения - уменьшение аппаратурных затрат. Устройство содержит генератор адреса, выполненный, например, в виде счетчика 3 адреса, который формирует адреса для блока 4 памяти чередующихся адресов данных и кодов операции. Младший разряд счетчика 3 позволяет стробировать ключи адреса данных 5 и кода операции 9 поочередно в противофазе, что достигается введением элемента НЕ 12. Один разряд кода операции используется для выбора поля данных в оперативной памяти 6 с помощью коммутатора 11 данных. Данные, выбранные на первом шаге тактирования счетчика 3, поступают на информационный вход-выход процессора 10 вместе с кодом операции, выбранным на втором шаге. Коммутатор 11 позволяет адресовать до 512 переменных при использовании одного байта для адресации памяти 6. 2 з.п.ф-лы, 1 ил.

Авторы

Даты

1990-05-15—Публикация

1986-07-21—Подача