ном случае oit 062. ... р- 0, а Dip ,. p+i ... оСц 1, формирователь 32 порога выполняется в виде эле- мента И, соединенного входами с входами блока от р-го до U-ro. При а -2ци формирователь 32 порога выполняется в виде линии связи с его U-ro входа на выход.

Устройство работает следующим образом,

В исходном состоянии многоканальный преобразователь 2 параллельного кода в последовательности импульсов: триггер 3, реверсивные накопители 5 и 8, счетный блок 13, сброшены. При этом на выходе триггера 3 присутствует нулевой сигнал, блокирующий прохождение тактовых импульсов через элементы И 6 и 9, в счетный блок 13 записан код числа q, а в реверсивные накопители 5«i и 8.J -1 коды чисел qj и q,j соответственно.

0

5

0

5

Если за время работы многоканального преобразователя 2 в некоторый момент времени на входы полусумматора 15 с момента начала цикла поступает К+1 или К+2 импульсов, на втором выходе счетного блока 13 появляется единичный сигнал, поступающий через элемент ИЛИ 12 на выход 18 конца контроля устройства, свидетельствуя об окончании цикла работы, при этом на информационный выход 17 устройства с первого выхода счетного блока 13 поступает нулевой сигнал.

Если за время работы многоканального преобразователя 2 в счетном блоке 13 не произойдет накопление требуемого числа импульсов (не меньше К+1), работа продолжается в описанном выше порядке до опроса всех входов 16, для чего потребуется п/2- (р+г+1 )Ј тактов, где п - разрядность входного кода. При этом по окончании работы

715

многоканального преобразователя 2 он самоблокируется и далее импульсов на выходах своих каналов не формирует.

При этом на его выходе останова форми -

руется импульс, переключающий триг-

гер 3 в паузе между тактовыми импульсами. При этом на выходе триггера 3 появляется единичный сигнал, разрешающий прохождение тактовых импульсов через элементы И 5 и 8.

Далее одновременно в каждой из групп реверсивных накопителей 5 и 8 осуществляатся последовательный пересчет их содержимого в счетный блок 13 Пусть 5.1 (8.J) наименьший номер реверсивного накопителя первой (второй) группы, в которой записан код, отличный от начального q(q; ) , т.е. за время работы многоканального преобразо вателя 2 на его суммирующие входы поступили импульсы, при этом на его первом выходе, соединенном с входом элемента К 6.i (9.J) - единичный сигнал, а на втором, соединенном с входа ми элементов И 6.(i+l)-6tp (9.(j + I)- 9.г) - нулевой, запрещающий прохождение тактовых импульсов на их выходы. Таким образом, на всех входах элемента И 6.1 (9.J), соединенных с вторы- ми выходами реверсивных накопителей 5.1 - 5. (1-1) (8.1-8. (j-O), имеются единичные сигналы. В результате тактовых импульсы проходят через элемент И 6.1 (9.J) на вход элемента И 10 (11) и далее на вход полусуммато- ра 15. Работа продолжается таким образом до возвращения реверсивного накопителя 5.1 (8.j) в исходное состояние, поскольку импульсы с выхода элемента И 6,1 (9.J) поступают на его вычитающий вход и от содержимого накопителя каждый раз вычитается единица. При возвращении реверсивного накопителя 5.1 (8.J) в исходное состояние на его первом выходе появляется нулевой сигнал, запрещающий дальнейшее прохождение тактовых импульсов на выход элемента И 6.1 (9.J), а на втором выходе - единичный сигнал, разрешающий прохождение тактовых им- пульсов на выходе элементов И 6. (1+1) б.р (9.(j+l) - 9.г). Далее аналогичным образом осуществляется пересчет содержимого реверсивных накопителей 5.(1+1) - 5.р (8.(j + l) - 8.г) в счетный блок 13.

Импульсы с выходов элементов ИЛИ 1 и 11 поступают на входы полусуммато

0

5

0

94

S

J

5, 35 50 55

40

1 18

ра 15. До обнуления (возвращения в исходное состояние) реверсивных накопителей одной из групп импульсы поступают на оба входа полусумматора 15, что вызывает импульсы на его выходе переноса, поступающие на второй суммирующий вход счетного блока 13, к содержимому которого при этом каждый раз прибавляется число 2. При возвращении в исходное состояние всех реверсивных накопителей одной из групп, импульсы начинают поступать только на один из входов полусумматора 15, что вызывает импульсы на его выходе суммы, поступающие на первый суммирующий вход счетного блока 13, к содержимому которого при этом каждый раз прибавляется единица. п

При 5- хс К работа продолжается

5-

в описанном порядке до накопления в счетном блоке 13 кода числа большего или равного q+K+1, при этом на его втором выходе появляется единичный сигнал, поступающий через элемент ИЛИ 12 на выход 18 конца контроля устройства, свидетельствуя об окончании цикла работы. С первого выхода счетного блока 13 на информационный выход 17 устройства поступает нулевой сигнал, являющийся результатом контроля.

п

I При 21 X,. К работа продолжается

Igel

в описанном порядке до возвращения в исходное состояние всех реверсивных накопителей 5 и 8 обоих групп, при этом на их вторых выходах появляются единичные сигналы, что вызывает единичный сигнал на выходе элемента И 14, поступающий через элемент ИЛИ 12 на выход 18 конца контроля устройства, свидетельствуя об окончании цикла работы устройства. Результат работы снимается с первого выхода счетного блока 13 на информационный

п

выход 17 устройства. Если

к,

на выходе 17 присутствует единичный

п сигнал, а если 21 х„ К, то - нуле5 1 э

ври.

Таким образом, на информационном

выходе 17 устройства формируется еди

п ничный сигнал, если LXS К, а в

s

противном случае формируется нулевой сигнал.

915

Формула изобретения

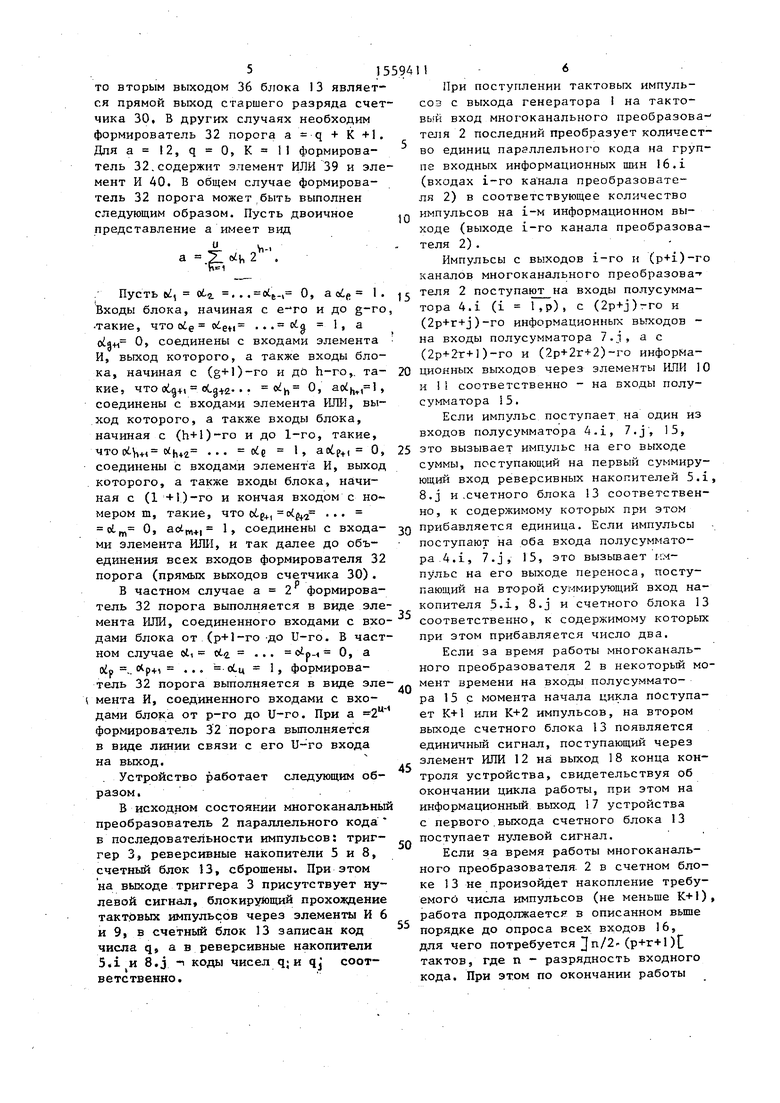

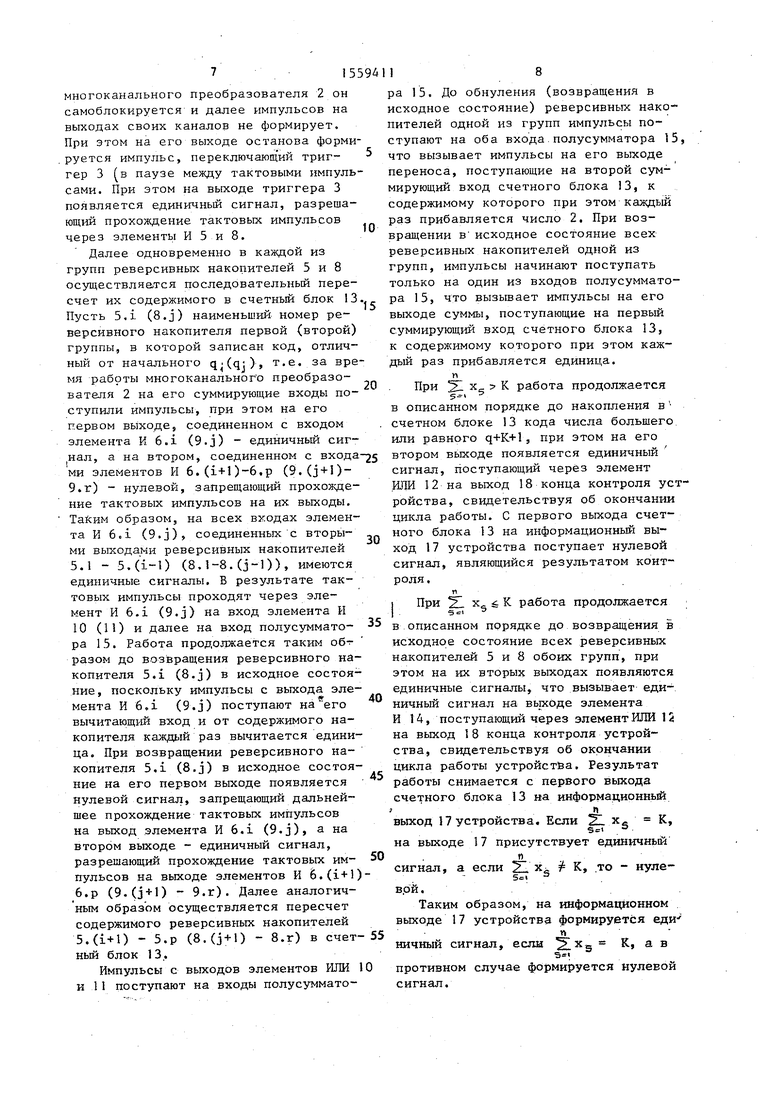

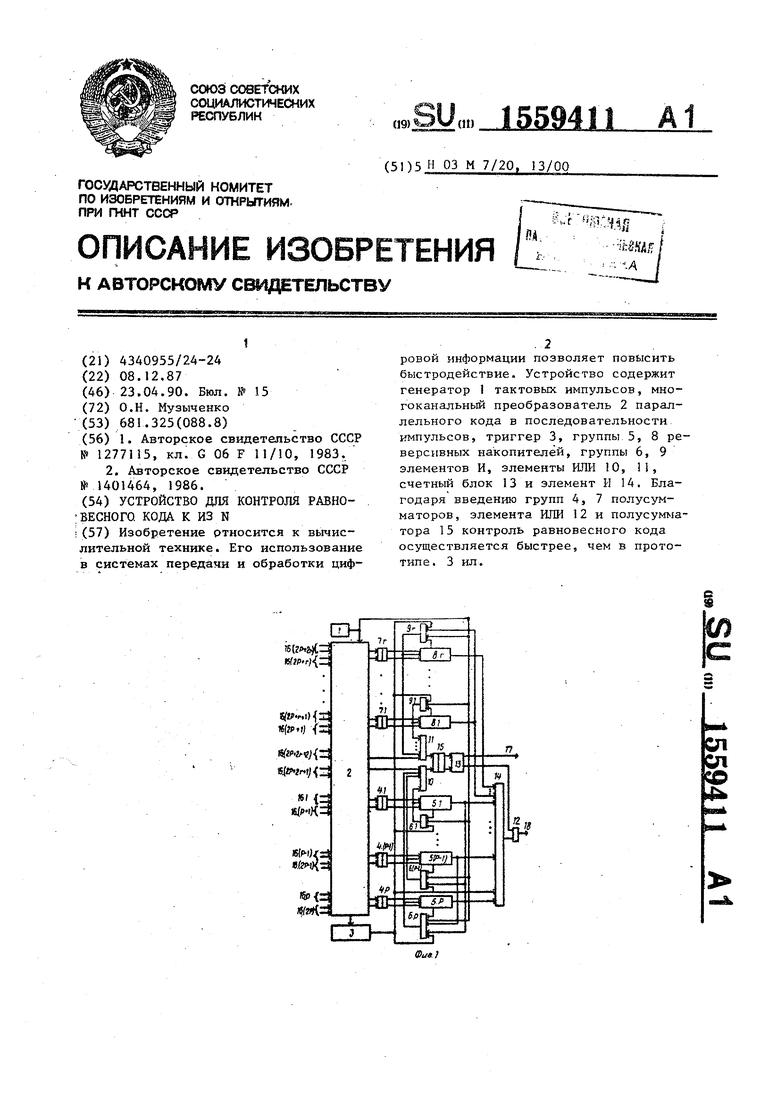

Устройство для контроля равновесного кодаК из N, содержащее счетный блок, многоканальный преобразователь параллельного кода в последовательности импульсов, группы информационных входов первого - (2р+2г+2)-го каналов которого (р,г 2,3,...) являются соответствующими входами устройства, генератор тактовых импульсов, выход которого подключен к первым входам первого - р-го элементов И первой группы и первого - r-го элементов И второй группы и тактовому входу многоканального преобразователя параллельного кода в последовательности импульсов, выход окончания преобразования которого соединен с входом триг гера, выход которого подключен к первому входу элемента И и вторым входам всех элементов И обеих групп, выход 1-го элемента И (i 1,р) первой группы и j-ro элемента И (j I ,r) второй группы соединены соответственно с i-м входом первого и j-м входом второго элементов ИЛИ и с вычитающим входом соответственно 1-го реверсивного накопителя первой группы и j-ro ревер- сивного накопителя второй группы, первые выходы которых подключены к третьим входам одноименных элементов II соответствующих групп, вторые выходы 1-го реверсивного накопителя первой группы и j-ro реверсивного накопителя второй группы соединены соответственно с (1+3)-ми входами (i+1) - р-го

I

10

5 о

5

элементов И первой группы и (л+3)-ми входами (j + 1) - r-го элементов И второй группы и соответственно с (1+1)-м H(J+P+)-M входами элемента Н, выходы (2р+2г+1)-го и (2р+2г+2)-го каналов многоканального преобразователя параллельного кода в последовательности импульсов подключены соответственно к (р+)-му входу первого и (г-Н)-му входу второго элементов ИЛИ, отличающееся тем, что, с целью повышения быстродействия, в устройство введены полусумматор, третий элемент ИЛИ и первая и вторая группы полусумматоров, выходы 1-го, (p+i)-ro, (2p+j)-ro и (2p+r+j)-ro каналов многоканального преобразователя параллельного кода в последовательности импульсов подключены к первому, второму входам соответственно 1-го полусумматора первой и j-ro полусумматора второй групп, выходы суммы и переноса которых соединены соответственно с первым и вторым суммирующими входами одноименных накопителей соответствующих групп, выходы первого и второго элементов ИЛИ подключены к первому и второму входам полусумматора, выходы суммы и переноса которого соединены соответственно с первым и вторым входами счетного блока, первый выход которого является информационным выходом устройства, второй выход счетного блока и выход элемента И подключены к входам третьего элемента ИЛИ, выход которого является выходом окончания работы устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения ошибок в равновесном коде К из @ | 1987 |

|

SU1564731A1 |

| Пороговый элемент | 1987 |

|

SU1647871A1 |

| Пороговый элемент | 1987 |

|

SU1584098A1 |

| Пороговый элемент | 1986 |

|

SU1387185A2 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ | 1987 |

|

RU2034401C1 |

| Устройство для контроля равновесного кода | 1987 |

|

SU1580563A1 |

| Пороговый элемент | 1985 |

|

SU1297219A1 |

| Многоканальный функциональный генератор | 1984 |

|

SU1191922A1 |

| Пороговый элемент | 1984 |

|

SU1277370A1 |

| Пороговый элемент | 1985 |

|

SU1297220A1 |

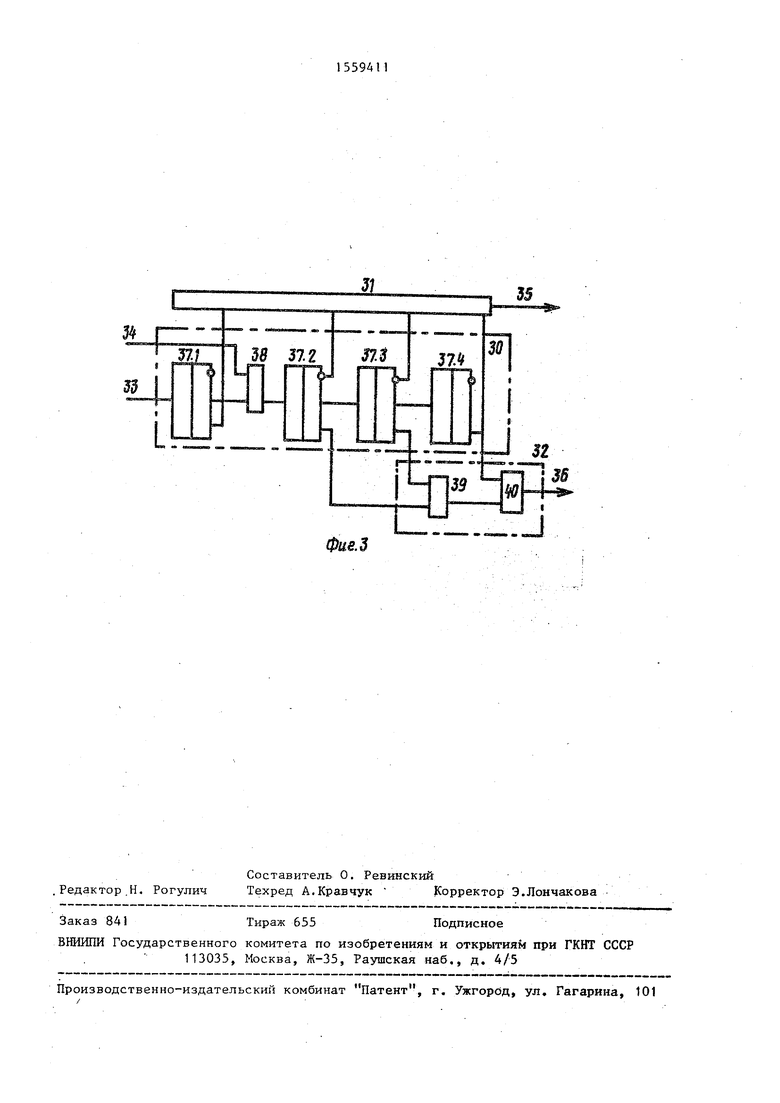

Изобретение относится к вычислительной технике. Его использование в системах передачи и обработки цифровой информации позволяет повысить быстродействие. Устройство содержит генератор 1 тактовых импульсов, многоканальный преобразователь 2 параллельного кода в последовательности импульсов, триггер 3, группы 5, 8 реверсивных накопителей, группы 6, 9 элементов И, элементы ИЛИ 10, 11, счетный блок 13 и элемент И 14. Благодаря введению групп 4, 7 полусумматоров, элемента ИЛИ 12 и полусумматора 15 контроль равновесного кода осуществляется быстрее, чем в прототипе. 3 ил.

25 |

Я

го

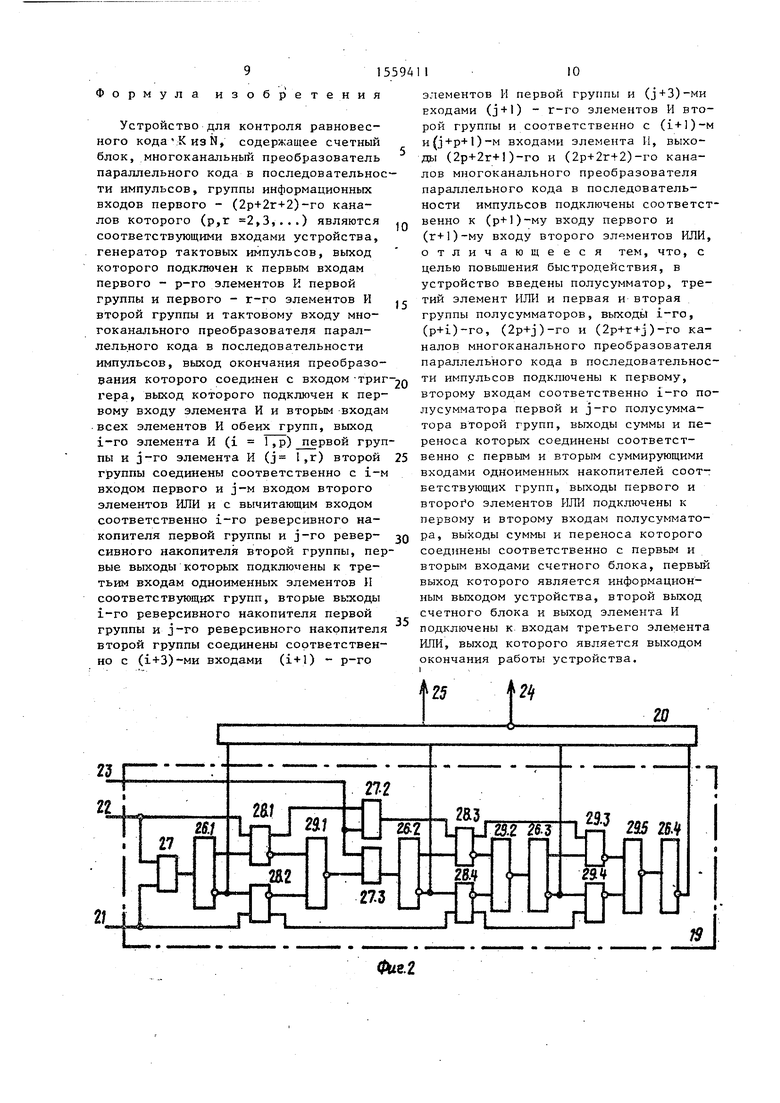

фие.З

tTr

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Преобразователь двоичного кода в последовательность импульсов | 1983 |

|

SU1277115A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля количества единиц двоичного кода по модулю К | 1986 |

|

SU1401464A2 |

Авторы

Даты

1990-04-23—Публикация

1987-12-08—Подача