1

(21)4357383/24-24

(22)05.01.88

(46) 23.05.90. Бюл. № 19

(71)Таганрогский радиотехнический институт им. В.Д.Калмыкова

(72)В.Е.Золотовский и Р.В.Коробков (53) 681.3(088.8)

(56) Авторское свидетельство СССР С 06 F 11/00, 1982. и др. Специализирован№ 1124312, кл. Сиолов В.Б.

ные ЦВМ. - М.: Высшая школа, 1981, с. 227, рис. 8.6.

(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДЕЛИТЕЛЯ ПО МОДУЛЮ

(57) Изобретение относится к вычислительной технике и может бить использовано при построении динамических систем. Цель изобретения - повышение достоверности контроля. Устройство содержит регистры 5,7, куда записываются контрольные разряды делимого и делителя соответственно, формирователи 10,12 вычетов по модулю, один из которых свертывает параллельный код, а другой - последовательный, группу 11 элементов И, умножители 13, 17, сумматоры 14,16, счетчик 18 по модулю, блок 19 сравнения. Устройство последовательно контролирует процесс деления, происходящий в контролируемом делителе 1, и обнаруживает ошибку в момент появления, а не по окончании операции деления. 4 ил.

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения в дополнительных кодах | 1988 |

|

SU1695307A2 |

| Устройство для сложения и вычитания с самоконтролем | 1988 |

|

SU1642469A1 |

| Устройство для регенерации биимпульсных сигналов | 1989 |

|

SU1688413A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1988 |

|

SU1580568A1 |

| Устройство для извлечения корня из суммы квадратов трех чисел | 1988 |

|

SU1624444A2 |

| УСТРОЙСТВО КОНТРОЛЯ ЭНЕРГИИ, ПЕРЕДАВАЕМОЙ ПО ВОЛОКОННО-ОПТИЧЕСКИМ ЛИНИЯМ СВЯЗИ (ВАРИАНТЫ) | 1999 |

|

RU2152133C1 |

| Устройство для обнаружения и исправления ошибок в системе остаточных классов | 1980 |

|

SU960823A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Устройство для контроля регистров сдвига | 1977 |

|

SU743038A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1989 |

|

SU1667065A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении динамических систем. Цель изобретения - повышение достоверности контроля. Устройство содержит регистры 5, 7, куда записываются контрольные разряды делимого и делителя соответственно, формирователи 10, 12 вычетов по модулю, один из которых свертывает параллельный код, а другой - последовательный, группу 11 элементов И, умножители 13, 17, сумматоры 14, 16, счетчик 18 по модулю, блок 19 сравнения. Устройство последовательно контролирует процесс деления, происходящий в контролируемом делителе 1, и обнаруживает ошибку в момент появления, а не по окончании операции деления. 4 ил.

ел

о

ОЭ 00 СЛ

к,

Изобретение относится к вычислительной технике и может быть использовано мри построении диагностических систем.

Целью изобретения является повышение достоверности контроля устройства.

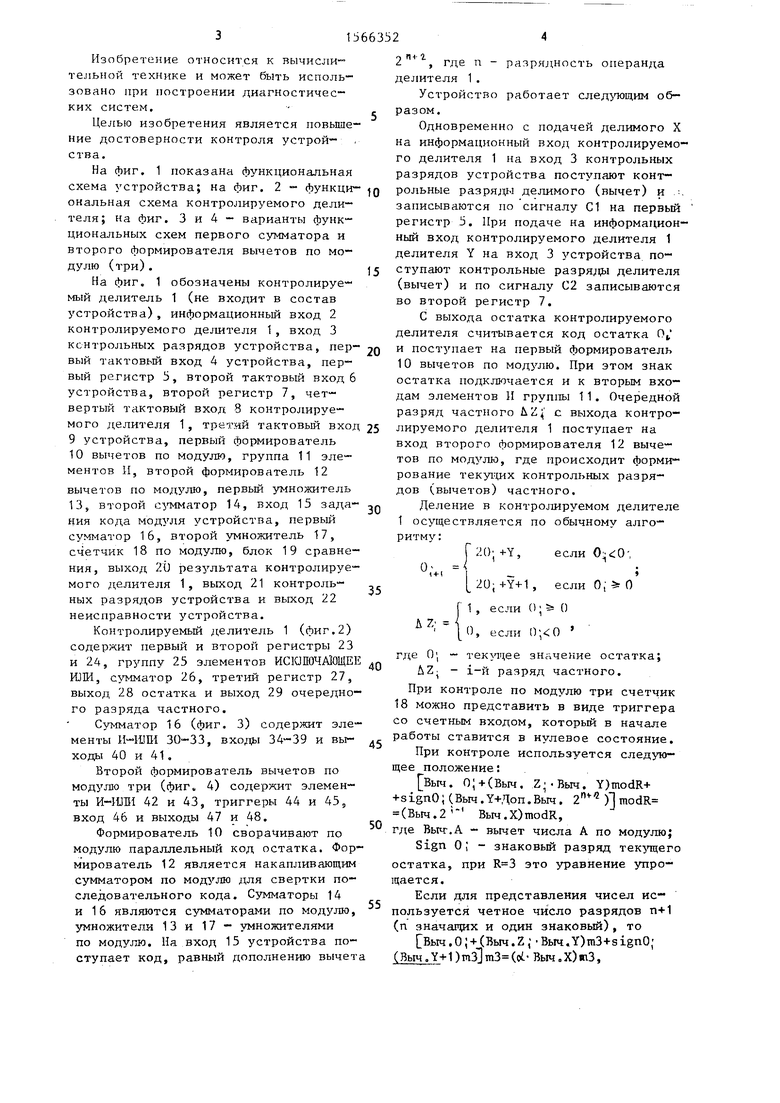

На Лиг. 1 показана Лункциональная схема гстройства; на Лиг. 2 - Лункци- опальная схема контролируемого делителя; на Лиг. 3 и 4 - варианты Лунк- циональных схем первого сумматора и второго Лормирователя вычетов по модулю (три) .

На Лиг, 1 обозначены контролируемый делитель 1 (не входит в состав устройства), инЛормационный вход 2 контролируемого делителя 1, вход 3 контрольных разрядов устройства, пер- вый тактовый вход 4 устройства, первый регистр Ь, второй тактовый вход 6 устройства, второй регистр 7, четвертый тактовый вход 8 контролируемого целителя 1, третий тактовый вход

9устройства, первый Лормирователь

10вычетов по модулю, группа 11 эле- менюв И, второй формирователь 12 вычетов по модулю, первый умножитель 13, второй сумматор 14, вход 15 задания кода модл дя устройства, первый сумматор 16, второй умножитель 17, счетчик 18 по модулю, блок 19 сравне-

ния, выход , 0 результата контролируе- мого делителя 1, выход 21 контрольных разрядов устройства и выход 22 неисправности устройства.

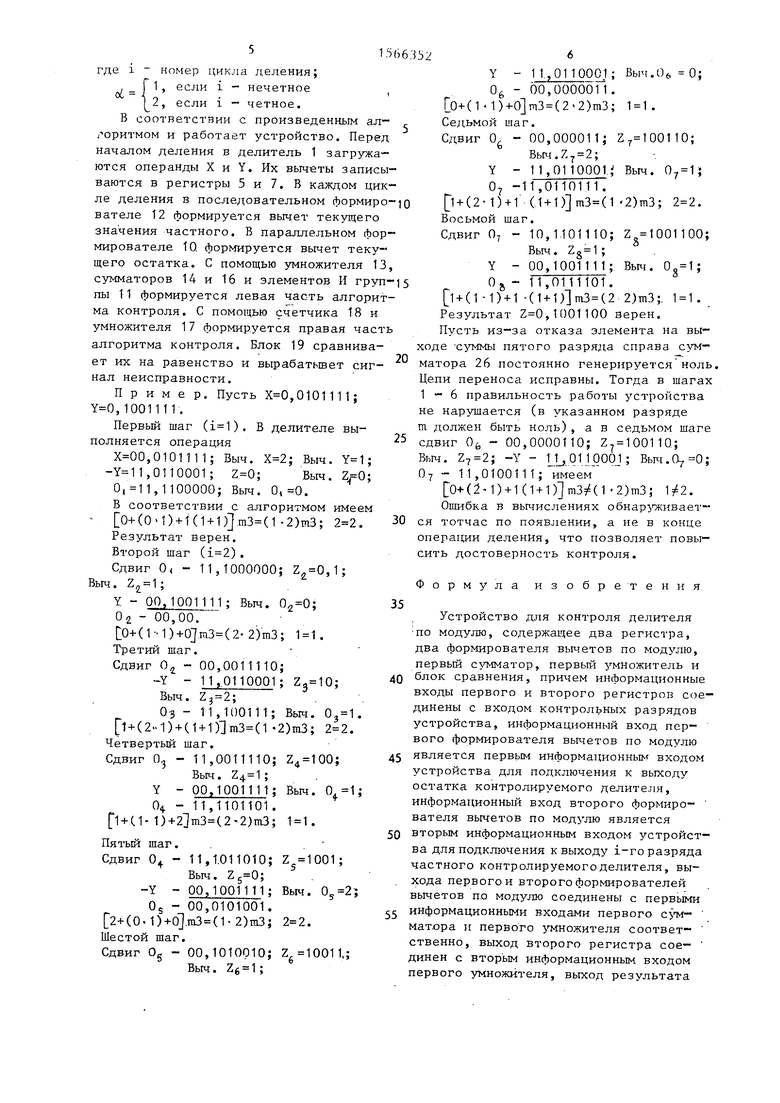

Контролируемый делитель 1 (Лиг.2) содернит первый и второй регистры 23 и 24, группу 5 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, сумматор 26, третий регистр 27, выход 28 остатка и выход 29 очередного разряда частного.

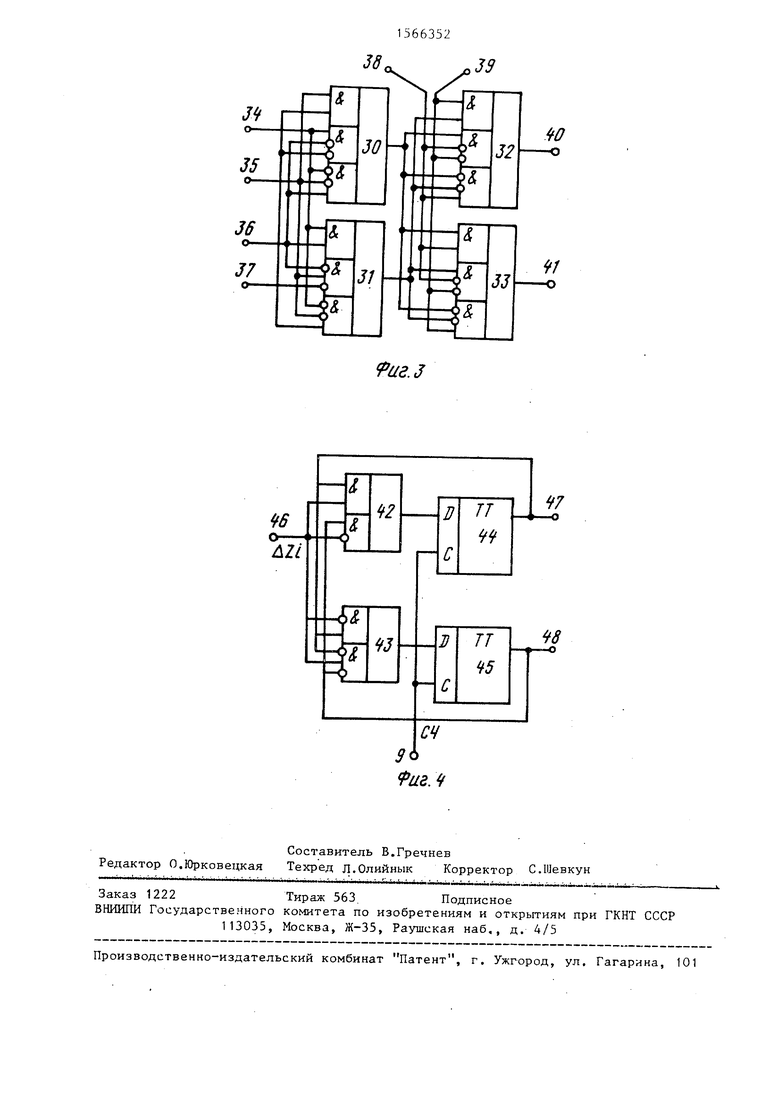

Сумматор 16 (фиг. 3) содержит элементы И-1ИШ 30-33, входы 34-39 и выходы 40 и 41.

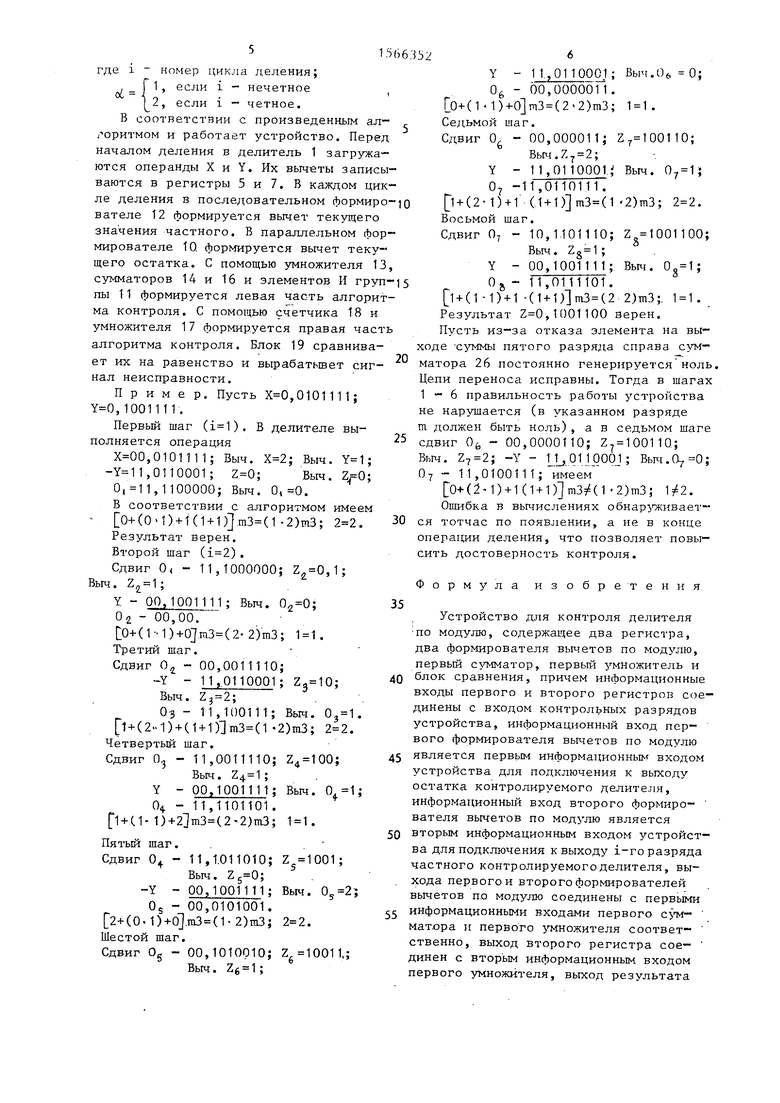

Второй Лормирователь вычетов по модулю три (фиг. 4) содержит элементы И-ШШ 42 и 43, триггеры 44 и 45, вход 46 и выходы 47 и 48.

Формирователь 10 сворачивают по модулю параллельный код остатка. Формирователь 12 является накапливающим сумматором по модулю для свертки последовательного кода. Сумматоры 14 и 16 являются сумматорами по модулю, умножители 13 и 17 - умножителями по модулю. На вход 15 устройства поступает код, равный дополнению вычет

15

JQ JQ25

663524

2 , где п - разрядность операнда делителя 1.

Устройство работает следующим образом.

Одновременно с подачей делимого X на информационный вход контролируемого делителя 1 на вход 3 контрольных разрядов устройства поступают контрольные разряды делимого (вычет) и записываются по сигналу С1 на первый регистр Ь. При подаче на информационный вход контролируемого делителя 1 делителя Y на вход 3 устройства поступают контрольные разряды делителя (вычет) и по сигналу С2 записываются во второй регистр 7.

С выхода остатка контролируемого делителя считывается код остатка и поступает на первый Лормирователь 10 вычетов по модулю. При этом знак остатка подключается и к вторым входам элементов И группы 11. Очередной разряд частного kZ с выхода контролируемого делителя 1 поступает на вход второго Лормирователя 12 вычетов по модулю, где происходит формирование текуцих контрольных разрядов (,вычетов) частного.

Деление в контролируемом делителе 1 осуществляется по обычному алгоритму

Л) +Y, если 0,0

30

0(

где

Ь 7. 20,+Y+1, если 0, О 1 , если 0,5s () О, t ели 0,0

5

о где

О1, - значение остатка; &Z( - i-й разряд частного.

При контроле по модулю три счетчик 18 можно представить в виде триггера со счетным входом, который в начале работы ставится в нулевое состояние.

При контроле используется следующее п оложе ние:

Выч. 0;+(Выч. Z;-Bbw. Y)modR+ + signO;(Bbi4.Y+T;on.Bbi4. 2n ) modR (Вьгч. Bbi4.X)modR, где Выч-.А - вычет числа А по модулю;

Sign 0, - знаковый разряд текущего остатка, при это уравнение упрощается.

Если для представления чисел используется четное число разрядов п+1 (п значащих и один знаковый), то

Выч.О; + (Выч.г, Bbnt.Y)m3+signO; (Выч.У+1)т31тЗ(о1-Выч.Х)юЗ.

0

где i ot

515

номер цик ы деления;

1,если i - нечетное

2,если i - четное.

В соответствии с произведенным алгоритмом и работает устройство. Перед началом деления в делитель 1 загружаются операнды X и Y. Их вычеты записываются в регистры 5 и 7. В каждом цикле деления в последовательном формиро вателе 12 формируется вычет текущего значения частного. В параллельном формирователе 10 формируется вычет текущего остатка. С помощью умножителя 13 сумматоров 14 и 16 и элементов И труп пы 11 формируется левая часть алгоритма контроля. С помощью счетчика 18 и умножителя 17 формируется правая част алгоритма контроля. Блок 19 сравнивает их на равенство и вырабатнвет сигнал неисправности.

Пример. Пусть ,0101111; ,1001111.

Первый шаг (). В делителе выполняется операция

,0101111; Выч. Выч. 1,0110001; Выч.

О,11,1100000; Выч. О, 0.

В соответствии с алгоритмом имеем 0+(01) + 1(1 + 1)тЗ(1 -2)тЗ; .

Результат верен.

Второй шаг ().

Сдвиг 0 - 11,1000000; ,1;

Выч. Z, 1;

Y - 00,1001111; Выч. О 2 - 00,00.

X)+()(2-2)m3; 1 1.

Третий шаг.

Сдвиг Ог - 00,0011110;

-Y - 11,0110001; Выч. Z3 2;

Оз - 11,100111; Выч. 03 и-(2«1) + ( 1 + 1)1 гаЗ(1 -2)тЗ; Четвертый шаг. Сдвиг 03 - 11,0011110;

Выч.

Y - 00,1001111; Выч. 04. - 1 1,1101101. 1 + U- 1)(2-2)m3; .

Пятый шаг.

Сдвиг Of - 11,1011010; Zs 1001;

04

Выч. Z,

-Y - 00,1001111;

Os - 00,0101001. 2+(0-1) 1-2)гаЗ; Шестой шаг.

Сдвиг 05 - 00,1010010; Выч.

5

0

0

Y О,

- 11, Olt 000.1;

Выч.Ое, 0;

J(t - 00,000001 1 . Го+(Ы) (2-2)тЗ; 1 1. Седьмой шаг.

Сдвиг Ofe - 00,000011; Z7 100110; Выч.Z 7 2;

Y - 11,01 10001. Выч. 07 1;

07 -11,0110111.

1 + (2-1) + 1 (1 + 1)тЗ (1 -2)тЗ; . Восьмой шаг. Сдвиг 07 - 10,1101110; Zs 1001100;

Выч. Y - 00,1001111; Выч, 08 - 11,0111101

o,i;

1 + (1 -П + 1 .(1 + 1)тЗ (2 2)тЗ; .

Результат ,1001100 верен.

Пусть из-за отказа элемента на выходе -суммы пятого разряда справа сумматора 26 постоянно генерируется ноль. Цепи переноса исправны. Тогда в шагах 1 - 6 правильность работы устройства не нарушается (в указанном разряде m должен быть ноль), а в седьмом шаге 5 сдвиг Оь - 00,0000110; Z7 100110;

Выч. -Y - ,011pOOJ; Выч. О7 - 11,0100111; имеем

0+(2-1) + 1(1 + 1)m35(12)m3; 1/2.

Ошибка в вычислениях обнаруживается тотчас по появлении, а не в конце операции деления, что позволяет повысить достоверность контроля.

Формула изобретения

Устройство для контроля делителя по модулю, содержащее два регистра, два формирователя вычетов по модулю, первый сумматор, первый умножитель и

блок сравнения, причем информационные входы первого и второго регистров соединены с входом контрольных разрядов устройства, информационный вход первого формирователя вычетов по модулю

является первым информационным входом устройства для подключения к выходу остатка контролируемого делителя, информационный вход второго Формирователя вычетов по модулю является

вторым информационным входом устройства для подключения к выходу 1-го разряда частного контролируемого делителя, выхода первого и второго Формирователей вычетов по модулю соединены с первыми

информационными входами первого сумматора и первого умножителя соответственно, выход второго регистра сое- динен с вторым информационным входом первого умножителя, выход результата

которого соединен с вторым информационным входом первого сумматора, выход результата которого соединен с первым информационным входом блока сравнения, выход которого является выходом неисправности устройства, тактовые входы первого и второго регистров являются первым и вторым тактовыми входами устройства для подключения к первому и второму тактовым входам контролируемого делителя, выход второго формирователя вычетов по модулю является выходом контрольных разрядов устройства, отличающее ся тем, что, с целью повышения достоверности контроля устройства, в него введены второй сумматор, второй умножитель, счетчик по модулю и группа элементов И, причем выход второго регист ра соединен с первым информационным входим второго сумматора, первые входы элементов И группы соединены с соответствующими разрядами выхода ре-

п

зулыата второго сумматора, вторые входы элементов И группы подключены к знаковому разряду первого информационного входа устройства, выходы элементов И группы соединены с соответствующими разрядами третьего информационного входа первого сумматора, выходы первого регистра и счетчика по модулю соединены соответственно с первым и вторым информационными входами второго умножителя, выход результата которого соединен с вторым информационным входом блока сравнения, второй информационный вход второго сумматора является входом задания кода модуля устройства, тактовый вход счетчика по модулю является третьим такто- вым входом устройства для подключения к третьему тактовому входу контролируемого делителя, четвертый тактовый вход которого является четвертым тактовым входом устройства.

Л

3d

Риг.з

Авторы

Даты

1990-05-23—Публикация

1988-01-05—Подача