СО СП

Изобретение относится к вычислительной технике и может использоваться в системах технического диагностирования дискретных объектов.

Целью изобретения является расширение функциональных возможностей устройства за счет локализации пакетов ошибок в двоичной последовательности.

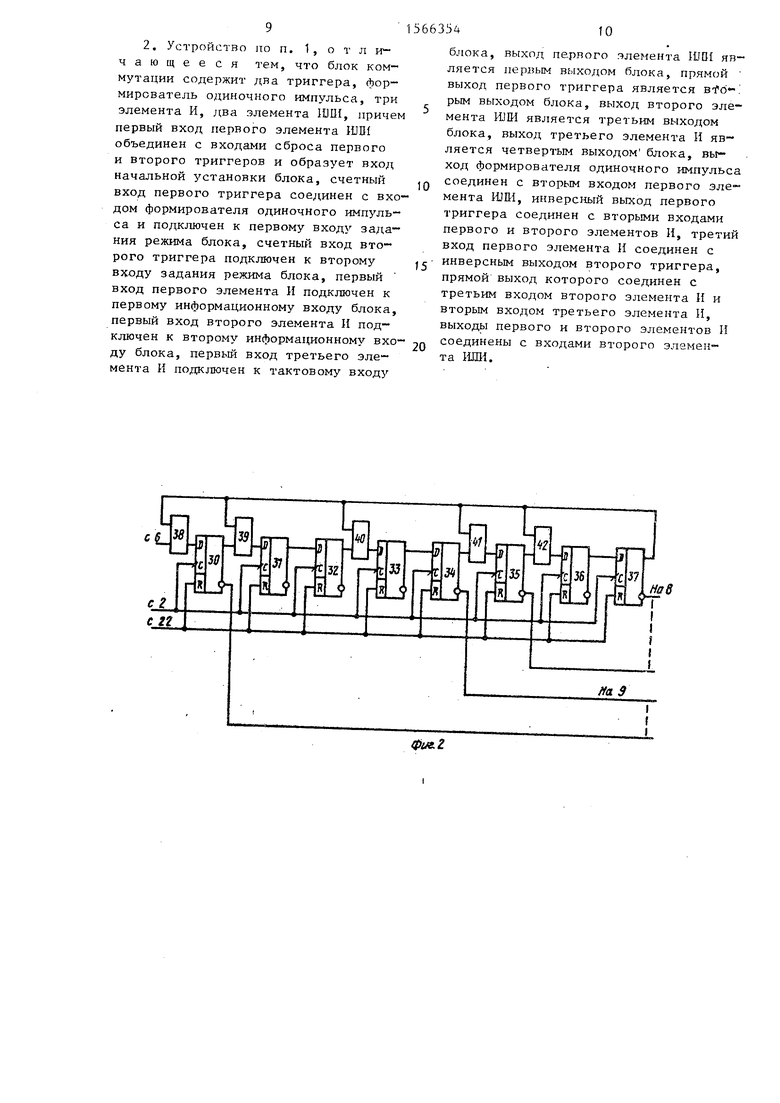

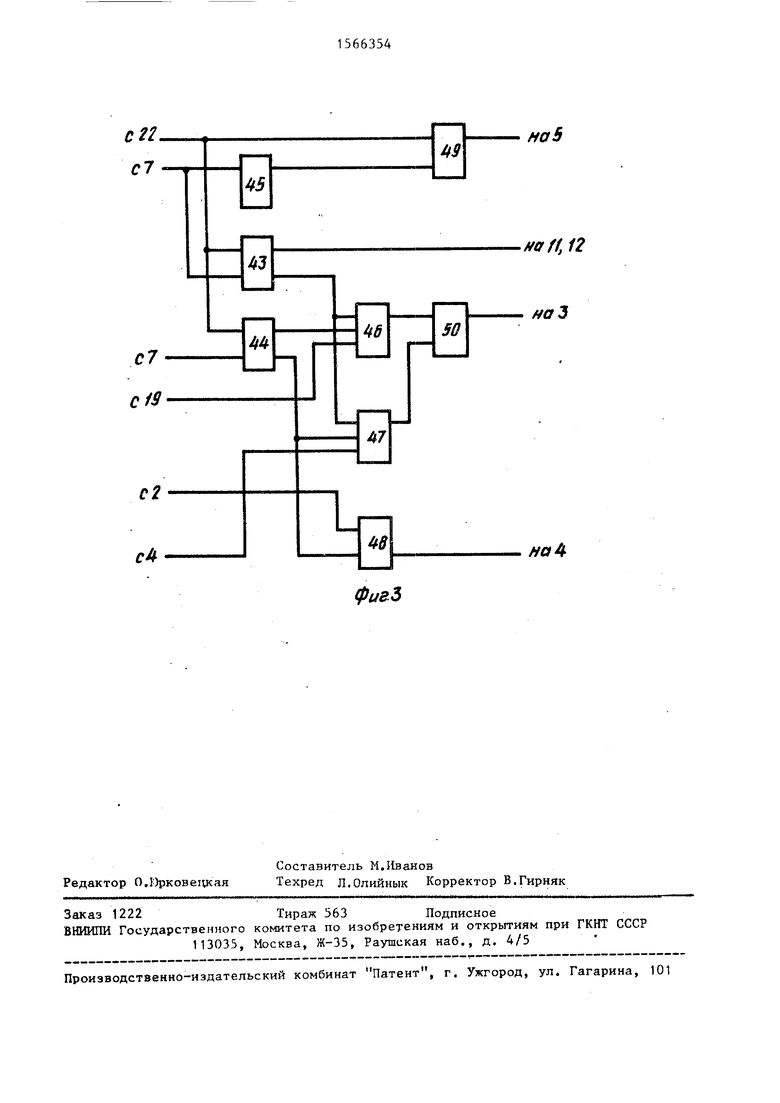

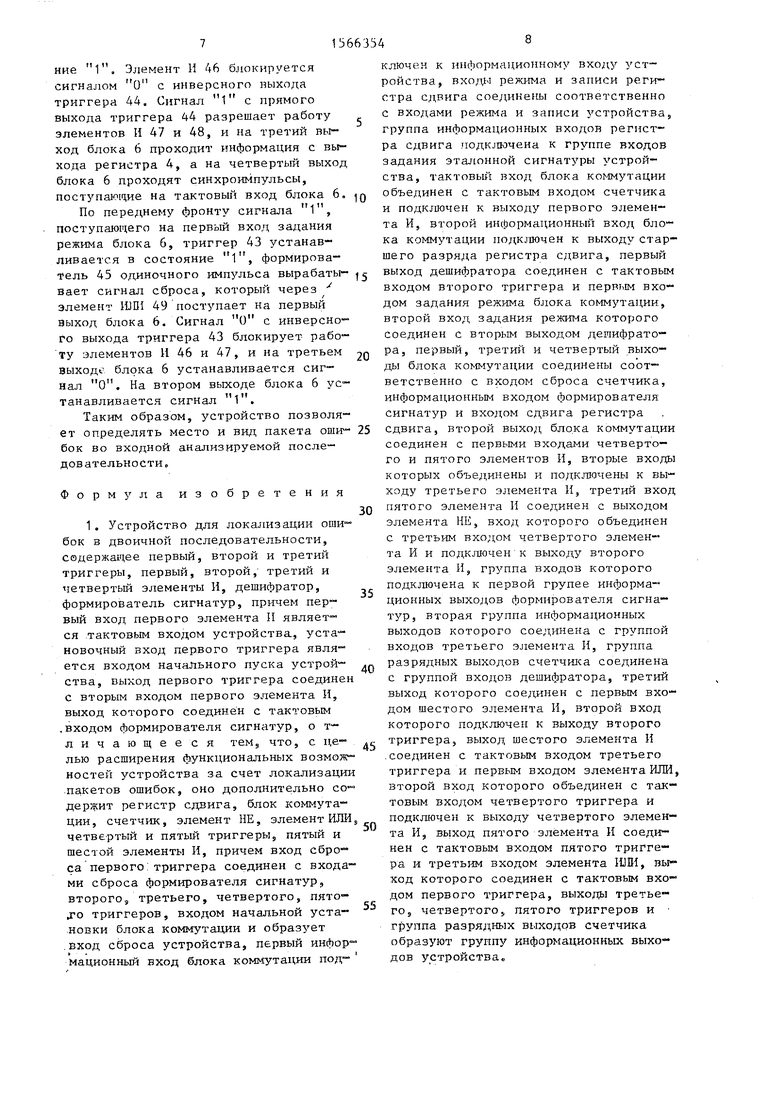

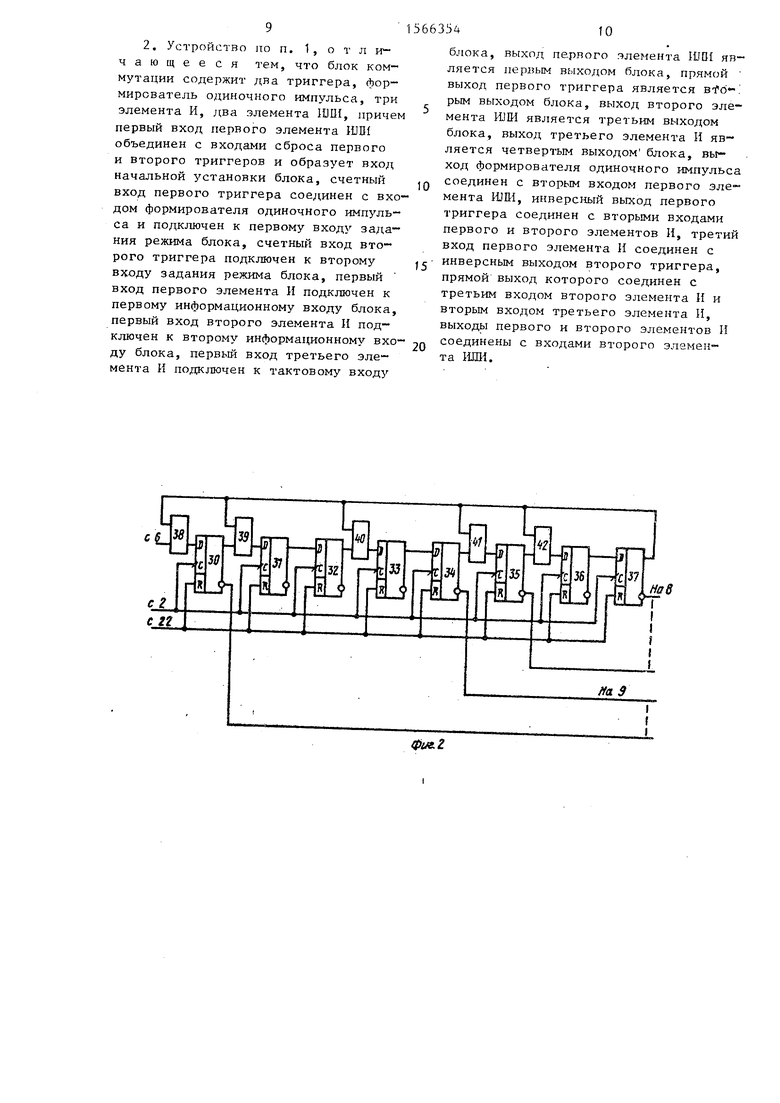

На фиг. 1 представлена схема устройства для локализации ошибок; на фиг. 2 - пример построения формирователя сигнатур с характеристическим многочленом g(x)x8+x6-t-x +x3+x+1 (х5+1)(х3+х+1); на фиг. 3 - схема блока коммутации.

Устройство (фиг. 1) содержит первый триггер 1, первый элемент И 2, формирователь 3 сигнатур, регистр 4 сдвига счетчик 5, блок 6 коммутации, дешифратор 7, второй 8 и третий 9 , элементы И, элемент НЕ 10, четвертый 11 и пятый 12 элементы И, второй 13 триггер, шестой элемент И 14, эле- мент 1UB1 15, третий 1Ь, четвертый 17 и пятый 18 триггеры, имеет информационный вход 19, тактовый вход 20, вход 21 начального пуска, вход 22 сброса, вход 23 режима, вход 24 за- писи, группу 25 входов эталонной сигнатуры 4 группу информационных выходов 26 - 29.

Формирователь сигнатур (фиг.2)

35

одержит D-триггеры 30 - 37 и элемены ИСКЛЮЧА10ЦЕЕ IDD1 38 - 42.

Блок коммутации (фиг. 3) содержит триггеры 43 и 44, формирователь 45 одиночного импульса, элементы И 46 - 0 48 и элементы ИЛИ 49 и 50.

Для определения места пакета ошибок в длинной последовательности для каждой контрольной точки определяют сигнатуру по формуле (все операции по д модулю 2)

, ч Јв(х) Г ( V I - -

ГСХ) g(x)

n-k

fe(x)-an, х - +...+авнсхп- +

., х

+. ..+а

0

а n-, а п-к коэффициенты, определяемые членами входной последовательности; ал„к,,...,а0 равны нулю; К - количество членов последовательности;g(x)(x -1 )р(х) , причем Ъ - максимальная длина пакета

0 5

5

0

0

5

ошибок; р(х) - неприводимый многочлен степени с- Ь; (2Ь-1),

где е - показатель неприводимого многочлена р(х), -1. Практически эталонную сигнатуру можно получить, если известный многочлен fQ(х) подавать на вход формирователя 3 начиная с коэффициентов высших разрядов до тех пор, пока последний коэффициент не попадет в ячейку младшего разряда формирователя 3. Для этого потребуется всего п сдвигов. В результате в Формирователе 3 останется остаток г(х) (эталонная сигнатура) от деления f0(х) на в(х). Если изменить какой-либо член последовательности f0(х), это приведет к изменению г (х).

При работе устройства на вход формирователя 3 подается контролируемая последовательность, состоящая из К элементов. После ее отключения пода- ется еще (n-К) элементов, ЯВЛЯЮРЩХСЯ коэффициентами г(х). Если в последовательности не было ошибок, то остаток в формирователе 3 г (х)0.

Если г (х)/0, то вход формирователя 3 сигнатур отключается от внешних цепей (подается постоянно О и производится сдвиг содержимого формирователя 3.

Если в процессе последовательных сдвигов в п-К-Ь младших разрядах формирователя 3 содержатся нули, то в остальных b ячейках окажется пакет ошибок, а количество проведенных сдвигов определяет номер первого ошибочного члена пакета.

Если в процессе последовательных сдвигов проведено п-2Ь-И сдвигов, а нули в п-К-Ь младших ячейках формирователя 3 не появились, это означает, что длина пакета больше чем b и обнаружить его место нельзя.

Изменяя разрядность формирователя 3 сигнатур, можно определять место ошибок, содержащихся в пакете любой длины.

Устройство работает следующим образом.

Перед началом работы по входу 22 устройства производится установка в состояние О триггеров 1,13,16,17, 18,43 и 44, формирователя 3, счетчика 5. На выходах 26,28 и 29 устройства устанавливаются нули. Блок 6 соединяет информационный вход 19 устройства с информационным входом формирователя 3, на нтором выходе блока 6 устанавливается состояние О.

Перед работой устройства на входе

23задания режима устанавливается сигнал 1, а на группу 25 входов подается код эталонной сигнатуры, который по сигналу, поступающему на вход

24записи устройства, записывается в регистр 4, при этом коэффициент старшего разряда эталонной сигнатуры будет на выходе регистра 4, Регистр 4 может быть реализован на микросхемах К155ИР1. После этого на входе 23 задания режима устанавливается сигнал О, который разрешает работу регистра 4 в режиме сдпига.

По сигналу Пуск, приходящему на вход 21 начального пуска устройства, триггер 1 переключается в состояние 1 и разрешает поступление синхроимпульсов через элемент И 2 на счетный вход счетчика 5 и тактовый вход фор-

30

35

40

мирователя 3. Происходит деление вход-25 устанавливается сигнал 1. Он озна- ной последовательности, поступающей на информационный вход формирователя 3, на характеристический многочлен. Число импульсов сдвига, подаваемых на вход формирователя 3, фиксируется счетчиком 5. Когда на формирователь 3 поступит К информационных символов, на втором выходе деыифрато- ра 7, соответствующем числу К, появится сигнал 1, который поступает на вход блока 6. Но этому сигналу блок 6 отключает информационный вход 19 устройства от информационного входа формирователя 3 и подключает к нему выход регистра 4, в котором находится эталонная сигнатура, а также разрешает поступление синхроимпульсов с выхода элемента И 2 на вход сдвига регистра 4.

После п сдвигов в формирователе 3 на первом выходе депифратора 7 появляется сигнал 1, который переключает триггер 13 в состояние 1, а также поступает на вход блока 6. По этому сигналу блок 6 отключает выход регистра 4 от информационного входа формирователя 3, подает на информационный вход формирователя 3 постоянно сигнал О, переключает второй выход в состояние 1, по первому выходу сбрасывает счетчик 5.

Если в последовательности ошибок нет, то остаток в формирователе 3 равен нулю, и на выходе элемента И 11

45

50

55

чает, что в последовательности есть ошибки. На прямом выходе трш гера 1 устанавливается сигнал О, который прекращает поступление синхроимпульсов через элемент И 2 на счетчик 5. Содержимое счетчика 5 указывает номер ошибочного такта. Оно поступает на выходы 27 устройства.

Если за п+2Ь+1 тактов сигнал 1 на выходе элемента И 12 не появляется, то на выходе элемента II 14 появляется сигнал 1, который переключает в состояние 1 триггер 16 и в состояние О триггер 1. На выходе 26 устройства устанавливается сигнал Этот сигнал означает, что пакет ошибок длиннее чем b и его место обнаружить нельзя.

Блок 6 (фиг. 3) работает следующим образом.

Перед началом работы сигнал сброса, приходящий на вход начальной установки блока 6, через элемент IUDI49 проходит на первый выход блока 6, а также устанавливает в состояние О триггеры 43 и 44. При этом на ьтором выходе блока 6 устанавливается сигнал О. Элементы И 47 и 48 заблокированы сигналом О с прямого выхода триггера 44. На третий выход блока 6 проходит информация с входа 19.

При поступлении сигнала 1 на второй вход задания режима блока 6 триггер 44 устанавливается в состоя-

6

II 1 II

, который норе- триггер 17 и

10

15

20

появляется сигнал 1 ключает в состояние I1 в состояние О триггер 1. Па прямом выходе триггера 1 уетанавливатся сигнал О, который блокирует прохождение синхроимпульсов через элемент И 2. На выходе 28 устройства Устанавливается сигнал 1. Он означает, что в последовательности ошибок нет.

При наличии сбоя остаток в формирователе 3 отличен от нуля, и на выходе элемента И 11 будет сигнал О. На выходе элемента ШП1 15 остается сигнал О, синхроимпульсы поступают на счетный вход счетчика 5 и тактовый вход формирователя 3. В процессе сдвига содержимого формирователя 3 элемент И 12 выдает сигнал 1, если в младших п-К-Ь разрядах формирователя 3 появляются нули. Сигнал 1 с элемента 11 12 переключает в состояние 1 триггер 18 и в состояние О триггер 1. На выходе 29 устройства

0

5

0

5 устанавливается сигнал 1. Он озна-

5

0

5

чает, что в последовательности есть ошибки. На прямом выходе трш гера 1 устанавливается сигнал О, который прекращает поступление синхроимпульсов через элемент И 2 на счетчик 5. Содержимое счетчика 5 указывает номер ошибочного такта. Оно поступает на выходы 27 устройства.

Если за п+2Ь+1 тактов сигнал 1 на выходе элемента И 12 не появляется, то на выходе элемента II 14 появляется сигнал 1, который переключает в состояние 1 триггер 16 и в состояние О триггер 1. На выходе 26 устройства устанавливается сигнал. Этот сигнал означает, что пакет ошибок длиннее чем b и его место обнаружить нельзя.

Блок 6 (фиг. 3) работает следующим образом.

Перед началом работы сигнал сброса, приходящий на вход начальной установки блока 6, через элемент IUDI49 проходит на первый выход блока 6, а также устанавливает в состояние О триггеры 43 и 44. При этом на ьтором выходе блока 6 устанавливается сигнал О. Элементы И 47 и 48 заблокированы сигналом О с прямого выхода триггера 44. На третий выход блока 6 проходит информация с входа 19.

При поступлении сигнала 1 на второй вход задания режима блока 6 триггер 44 устанавливается в состоя-

ние 1. Элемент И 46 блокируется сигналом О с инверсного выхода триггера 44. Сигнал 1 с прямого выхода триггера 44 разрешает работу элементов И 47 и 48, и на третий выход блока 6 проходит информация с выхода регистра 4, а на четвертый выход блока 6 проходят синхроимпульсы, поступающие на тактовый вход блока 6.

По переднему фронту сигнала 1, поступающего на первый вход задания режима блока 6, триггер 43 устанавливается в состояние 1м, формирователь 45 одиночного импульса вырабаты- вает сигнал сброса, который через / элемент HJCI 49 поступает на первый выход блока 6. Сигнал О с инверсного выхода триггера 43 блокирует работу элементов И 46 и 47, и на третьем выходь блока 6 устанавливается сигнал О. На втором выходе блока 6 устанавливается сигнал 1.

Таким образом, устройство позволяет определять место и вид пакета ошн- бок во входной анализируемой последовательности.

Формула изобретения

1. Устройство для локализации ошибок в двоичной последовательности, содержащее первый, второй и третий триггеры, первый, второй, третий и четвертый элементы И, дешифратор, формирователь сигнатур, причем первый вход первого элемента И является тактовым входом устройства, установочный вход первого триггера является входом начального пуска устрой- ства, выход первого триггера соединен с вторым входом первого элемента И, выход которого соединен с тактовым .входом формирователя сигнатур, о т- личающееся тем, что, с це- лью расширения функциональных возможностей устройства за счет локализации пакетов ошибок, оно дополнительно содержит регистр сдвига, блок коммутации, счетчик, элемент НЕ, элемент ИЛИ, четвертый и пятый триггеры, пятый и шестой элементы И, причем вход сброса первого триггера соединен с входами сброса формирователя сигнатур, второго, третьего, четвертого, пятого триггеров, входом начальной установки блока коммутации и образует вход сброса устройства, первый инЛор- мационный вход блока коммутации под

Q

5

0

д

ключен к информационному входу устройства, входы режима и записи регистра сдвига соединены соответственно с входами режима и записи устройства, группа информационных входов регистра сдвига подключена к группе входов задания эталонной сигнатуры устройства, тактовый вход блока коммутации объединен с тактовым входом счетчика и подключен к выходу первого элемента И, второй информационный вход блока коммутации подключен к выходу старшего разряда регистра сдвига, первый выход дешифратора соединен с тактовым входом второго триггера и первым входом задания режима блока коммутации, второй вход задания режима которого соединен с вторым выходом дешифратора, первый, третий и четвертый выходы блока коммутации соединены соответственно с входом сброса счетчика, информационным входом формирователя сигнатур и входом сдвига регистра сдвига, второй выход блока коммутации соединен с первыми входами четвертого и пятого элементов И, вторые входы которых объединены и подключены к выходу третьего -элемента И, третий вход пятого элемента И соединен с выходом элемента НЕ, вход которого объединен с третьим входом четвертого элемента И и подключен к выходу второго элемента И, группа входов которого подключена к первой групее информационных выходов формирователя сигнатур, вторая группа информационных выходов которого соединена с группой входов третьего элемента И, группа разрядных выходов счетчика соединена с группой входов дешифратора, третий выход которого соединен с первым входом шестого элемента И, второй вход которого подключен к выходу второго триггера, выход шестого элемента И соединен с тактовым входом третьего триггера и первым входом элемента ИЛИ, второй вход которого объединен с тактовым входом четвертого триггера и подключен к выходу четвертого элемента И, выход пятого элемента И соединен с тактовым входом пятого триггера и третьим входом элемента ШП1, выход которого соединен с тактовым входом первого триггера, выходы третьего, четвертого, пятого триггеров и группа разрядных выходов счетчика образуют группу информационных выходов устройства.

91

2. Устройство по п. отличающееся тем, что блок коммутации содержит два триггера, формирователь одиночного импульса, три элемента И, два .элемента 1001, причем первый вход первого элемента ILJDI объединен с входами сброса первого и второго триггеров и образует вход начальной установки блока, счетный вход первого триггера соединен с входом формирователя одиночного импульса и подключен к первому входу задания режима блока, счетный вход второго триггера подключен к второму входу задания режима блока, первый вход первого элемента И подключен к первому информационному входу блока, первый вход второго элемента И подключен к второму информационному входу блока, первый вход третьего элемента И подключен к тактовому входу

66354

блока

10

10

15

20

, выход первого элемента ИЖ является первым выходом блока, прямой выход первого триггера является Bfo- рым выходом блока, выход второго элемента ИЛИ является третьим выходом блока, выход третьего элемента И является четвертым выходом1 блока, выход формирователя одиночного импульса соединен с вторым входом первого элемента ИЛИ, инверсный выход первого триггера соединен с вторыми входами первого и второго элементов И, третий вход первого элемента И соединен с инверсным выходом второго триггера, прямой выход которого соединен с третьим входом второго элемента И и вторым входом третьего элемента И, выходы первого и второго элементов И соединены с входами второго элемента ИЛИ.

на В

на ft, 12

наЗ

на 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный сигнатурный анализатор | 1989 |

|

SU1837291A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

| Устройство для контроля логических блоков | 1980 |

|

SU902018A1 |

| Сигнатурный анализатор (его варианты) | 1984 |

|

SU1252784A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Устройство для определения свойств полноты логических функций | 1984 |

|

SU1170446A1 |

| Устройство для коррекции ошибок в блоках памяти | 1985 |

|

SU1257708A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1983 |

|

SU1157544A1 |

| Устройство для контроля и диагностики цифровых блоков | 1983 |

|

SU1167610A1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

Изобретение относится к вычислительной технике и может использоваться в системах технического диагностирования дискретных объектов. Цель изобретения - расширение функциональных возможностей устройства за счет локализации пакетов ошибок. Устройство содержит триггеры 1, 13, 16, элементы И 2, 8, 9, 11, формирователь 3 сигнатур, дешифратор 7. В устройство введены регистр 4 сдвига, блок 6 коммутации, счетчик 5, элемент НЕ 10, элемент ИЛИ 15, триггеры 17, 18, элементы И 12, 14. 1 з.п.ф-лы, 3 ил.

фигЗ

| Сигнатурный анализатор | 1985 |

|

SU1411748A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Ударно-вращательная врубовая машина | 1922 |

|

SU126A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-05-23—Публикация

1988-03-22—Подача