I2 I

20

(Л

J

9

ajO

41 °12

о

ND

| название | год | авторы | номер документа |

|---|---|---|---|

| Коммутационное устройство | 1990 |

|

SU1730635A1 |

| Устройство для обмена информацией | 1979 |

|

SU842773A1 |

| Коммутационное устройство | 1989 |

|

SU1672464A1 |

| Устройство коммутации | 1980 |

|

SU894866A1 |

| Коммутатор | 1987 |

|

SU1434541A1 |

| РАСПРЕДЕЛИТЕЛЬНАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1997 |

|

RU2122229C1 |

| Запоминающее устройство с переменным форматом данных | 1981 |

|

SU987678A1 |

| Коммутационное устройство | 1984 |

|

SU1246109A1 |

| РАСПРЕДЕЛЕННАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 2000 |

|

RU2185656C2 |

| Коммутационное устройство | 1988 |

|

SU1539790A1 |

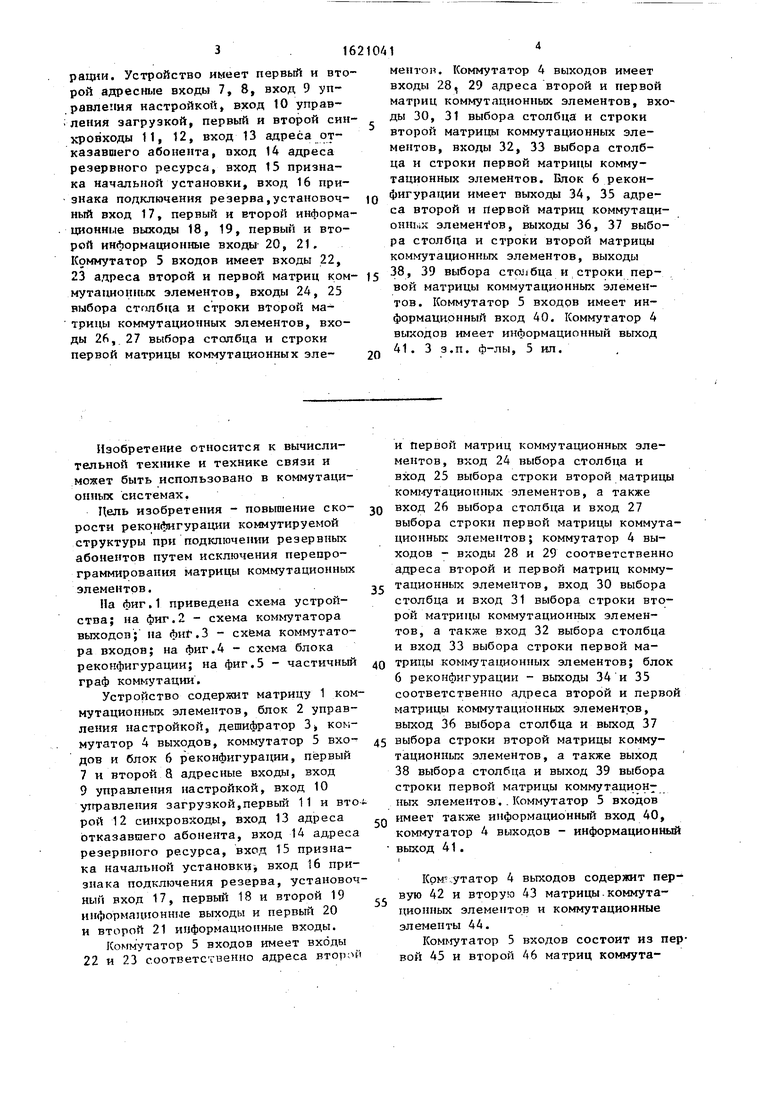

Изобретение относится к вычислительной технике и технике связи и мо- жет быть использовано в коммутационных системах. IT елью изобретения является повышение скорости реконфигурации коммутируемой структуры при подключении резервных абонентов путем исключения перепрограммирования коммутаторов. Устройство содержит матрицу коммутационных элементов 1, блок 2 управления настройкой, дешифратор 3, коммутатор 4 выходов, коммутатор 5 входов, блок 6 реконфигу

Фиг.1

рации. Устройство имеет первый и второй адресные входы 7, 8, вход 9 управления настройкой, вход 10 управления загрузкой, первый и второй син- хров ходы 11, 12, вход 13 адреса отказавшего абонента, вход 14 адреса резервного ресурса, вход 15 признака начальной установки, вход 16 признака подключения резерва,установочный вход 17, первый и второй информационные выходы 18, 19, первый и второй информационные входы 20, 21. Коммутатор 5 входов имеет входы 22, 23 адреса второй и первой матриц коммутационных элементов, входы 24, 25 выбора столбца и строки второй матрицы коммутационных элементов, входы 26, 27 выбора столбца и строки первой матрицы коммутационных элеИзобретение относится к вычислительной технике и технике связи и может быть использовано в коммутационных системах.

Цель изобретения - повышение ско- рости реконфигурации коммутируемой структуры при подключении резервных абонентов путем исключения перепрограммирования матрицы коммутационных элементов.

На фиг.1 приведена схема устройства; на фиг.2 - схема коммутатора выходов; на фиГ.З - схема коммутатора входов; на фиг.4 - схема блока реконфигурации; на фиг.5 - частичный граф коммутации.

Устройство содержит матрицу 1 коммутационных элементов, блок 2 управления настройкой, дешифратор 3, коммутатор 4 выходов, коммутатор 5 вхо- дов и блок 6 реконфигурации, первый 1 и второй а адресные входы, вход 9 управления настройкой, вход 10 утгравления загрузкой,первый 11 и BTO рой 12 синхровходы, вход 13 адреса отказавшего абонента, вход 14 адреса резервного ресурса, вход 15 признака начальной установки, вход 16 признака подключения резерва, установочным вход 17, первый 18 и второй 19 информационные выходы и первый 20 и второй 21 информационные входы.

Коммутатор 5 входов имеет входы 22 и 23 соответственно адреса второй

ментов. Коммутатор 4 выходов имеет входы 28, 29 адреса второй и первой матриц коммутационных элементов, входы 30, 31 выбора столбца и строки второй матрицы коммутационных элементов, входы 32, 33 выбора столбца и строки первой матрицы коммутационных элементов. Блок 6 рекон- фигурации имеет выходы 34, 35 адреса второй и Первой матриц коммутационных элементов, выходы 36, 37 выбора столбца и строки второй матрицы коммутационных элементов, выходы 38, 39 выбора столбца и строки первой матрицы коммутационных элементов. Коммутатор 5 входов имеет информационный вход 40. Коммутатор 4 выходов имеет информационный выход 41. 3 э.п. ф-лы, 5 ил.

5

0

5 Q

5

и первой матриц коммутационных элементов, вход 24 выбора столбца и вход 25 выбора строки второй матрицы коммутационных элементов, а также вход 26 выбора столбца и вход 27 выбора строки первой матрицы коммутационных элементов; коммутатор 4 выходов - входы 28 и 29 соответственно адреса второй и первой матриц коммутационных элементов, вход 30 выбора столбца и вход 31 выбора строки второй матрицы коммутационных элементов, а также вход 32 выбора столбца и вход 33 выбора строки первой матрицы коммутационных элементов; блок 6 реконфигурации - выходы 34 и 35 соответственно адреса второй и первой матрицы коммутационных: элементов, выход 36 выбора столбца и выход 37 выбора строки второй матрицы коммутационных элементов, а также выход 38 выбора столбца и выход 39 выбора строки первой матрицы коммутацией - ных элементов..Коммутатор 5 входов имеет также информационный вход 40, коммутатор 4 выходов - информационный выход 41.

Ком утатор 4 выходов содержит первую 42 и вторую 43 матрицы.коммутационных элементов и коммутационные элементы 44.

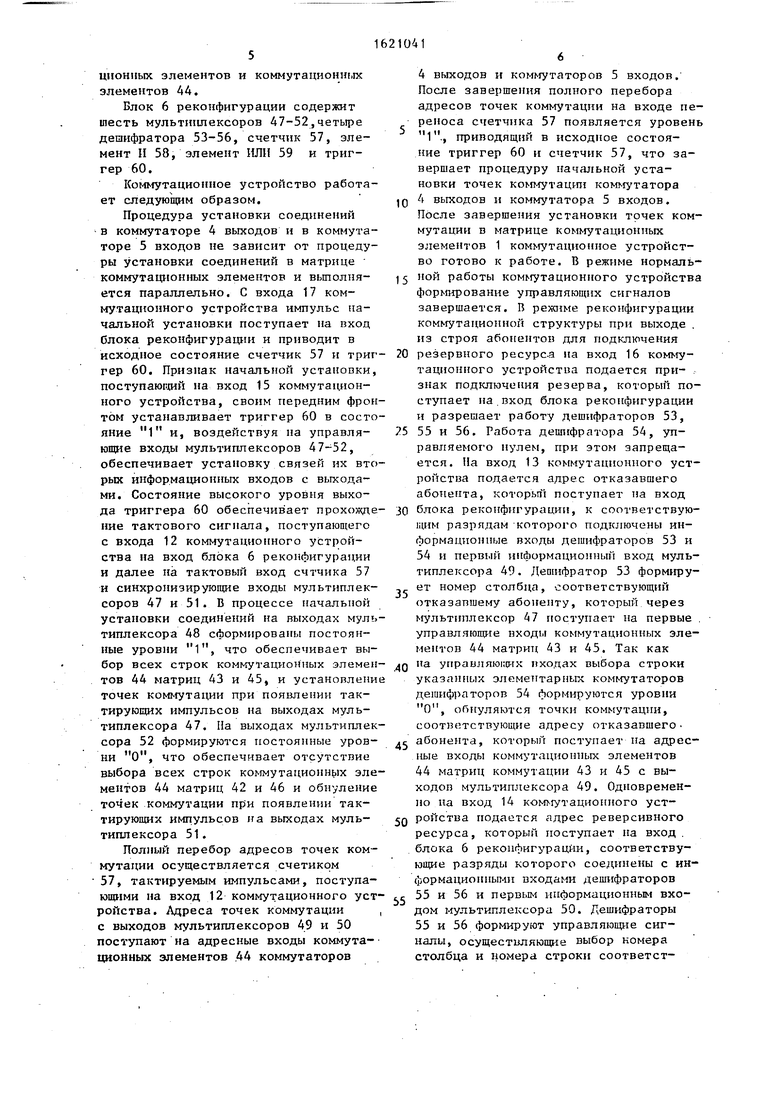

Коммутатор 5 входов состоит из первой 45 и второй 46 матриц коммутацнонных элементов и коммутационных элементов 44.

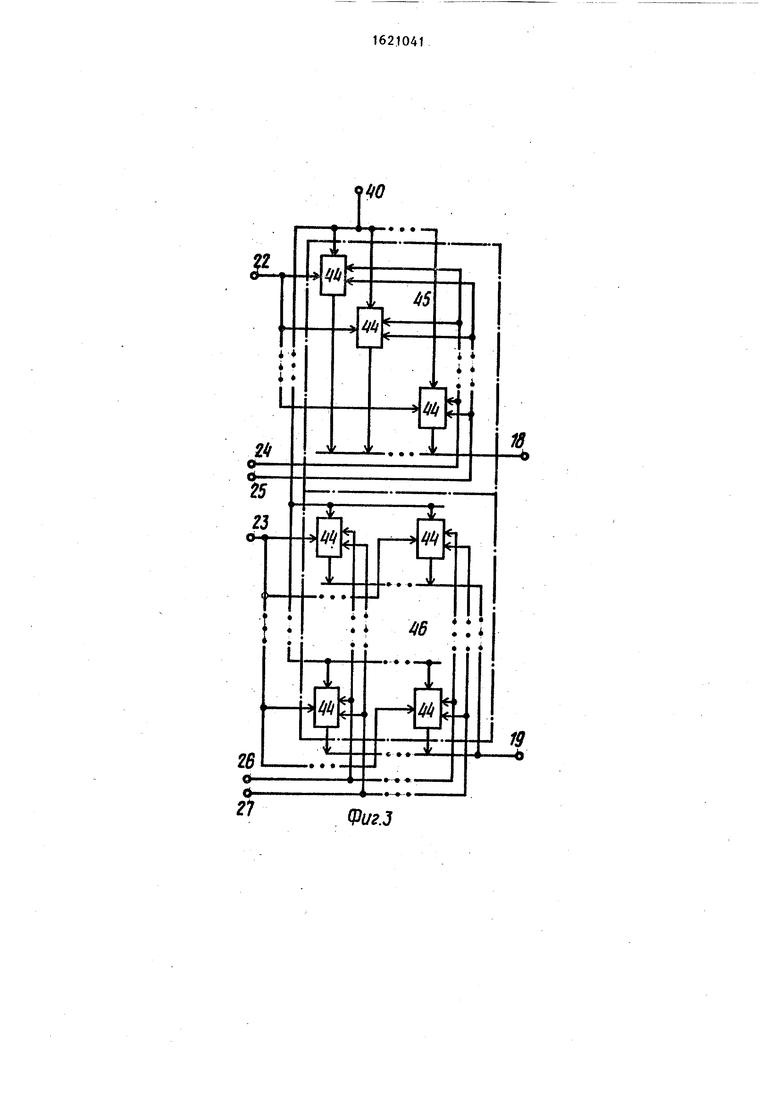

Блок 6 реконфигурации содержит шесть мультиплексоров 47-52,четыре дешифратора 53-56, счетчик 57, элемент И 58, элемент ИЛИ 59 и триггер 60.

Коммутационное устройство работает следующим образом.

Процедура установки соединений в коммутаторе 4 выходов и в коммутаторе 5 входов не зависит от процедуры установки соединений в матрице коммутационных элементов и выполняется параллельно. С входа 17 коммутационного устройства импульс начальной установки поступает на вход блока реконфигурации и приводит в исходное состояние счетчик 57 и триггер 60. Признак начальной установки, поступающий на вход 15 коммутационного устройства, своим передним фронтом устанавливает триггер 60 в состояние 1м и, воздействуя на управляющие входы мультиплексоров 47-52, обеспечивает установку связей их вторых информационных входов с выходами. Состояние высокого уровня выхода триггера 60 обеспечивает прохождение тактового сигнала, поступающего с входа 12 коммутационного устройства на вход блока 6 реконфигурации и далее на тактовый вход счтчика 57 и синхронизирующие входы мультиплексоров 47 и 51. В процессе начальной установки соединений на выходах мультиплексора 48 сформированы постоянные уровни 1, что обеспечивает выбор всех строк коммутационных элементов 44 матриц 43 и 45, и установление точек коммутации при появлении тактирующих импульсов на выходах мультиплексора 47. На выходах мультиплексора 52 формируются постоянные уровни О, что обеспечивает отсутствие выбора всех строк коммутационных элементов 44 матриц 42 и 46 и обнуление точек коммутации при появлении тактирующих импульсов на выходах мультиплексора 51.

Полный перебор адресов точек коммутации осуществляется счетиком 57, тактируемым импульсами, поступающими на вход 12 коммутационного устойства. Адреса точек коммутации , выходов мультиплексоров 49 и 50 оступают на адресные входы коммутаионных элементов 44 коммутаторов

0

4 выходов и коммутаторов 5 входов. После завершения полного перебора адресов точек коммутации на входе переноса счетчика 57 появляется уровень 1|1, приводящий в исходное состояние триггер 60 и счетчик 57, что завершает процедуру начальной установки точек коммутации коммутатора 4 выходов и коммутатора 5 входов. После завершения установки точек коммутации в матрице коммутационных элементов 1 коммутационное устройство готово к работе. В режиме нормаль5 ной работы коммутационного устройства формирование управляющих сигналов завершается. В режиме реконфигурации коммутационной структуры при выходе из строя абонентов для подключения

0 резервного ресурс.а на вход 16 коммутационного устройства подается признак подключения резерва, который поступает на вход блока реконфигурации и разрешает работу дешифраторов 53,

5 55 и 56. Работа дешифратора 54, управляемого нулем, при этом запрещается. На вход 13 коммутационного устройства подается адрес отказавшего абонента, который поступает на вход блока реконфигурации, к соответствующим разрядам которого подключены информационные входы дешифраторов 53 и

54и первый информационный вход мультиплексора 49. Дешифратор 53 формирует номер столбца, соответствующий отказавшему абоненту, который через мультиплексор 47 поступает на первые управляющие входы коммутационных элементов 44 матриц 43 и 45. Так как

на управляющих пхоцах выбора строки указанных элементарных коммутаторов дешифраторов 54 формируются уровни О, обнуляются точки коммутации, соответствующие адресу отказавшего

с абонента, который поступает на адресные входы коммутационных элементов 44 матриц коммутации 43 и 45 с выходов мультиплексора 49. Одновременно на вход 14 ком гутационного устQ ройства подается адрес реверсивного ресурса, который поступает на вход блока 6 реконфигурации, соответствующие разряды которого соединены с информационными входами дешифраторов

55и 56 и первым информационным входом мультиплексора 50. Дешифраторы 55 и 56 формируют управляющие сигналы, осуществляющие выбор номера столбца и номера строки соответст0

5

0

5

венно по адресу резервного ресурса, которые через мультиплексоры 51 и 52 соответственно поступают на соответствующие вторые управляющие входы коммутационных элементов 44, принадлежащих матрицам 42 и 46, и вызывают перевод в единичное состояние точек коммутации согласно адресу, поступающему с выхода мультиплексора 50.

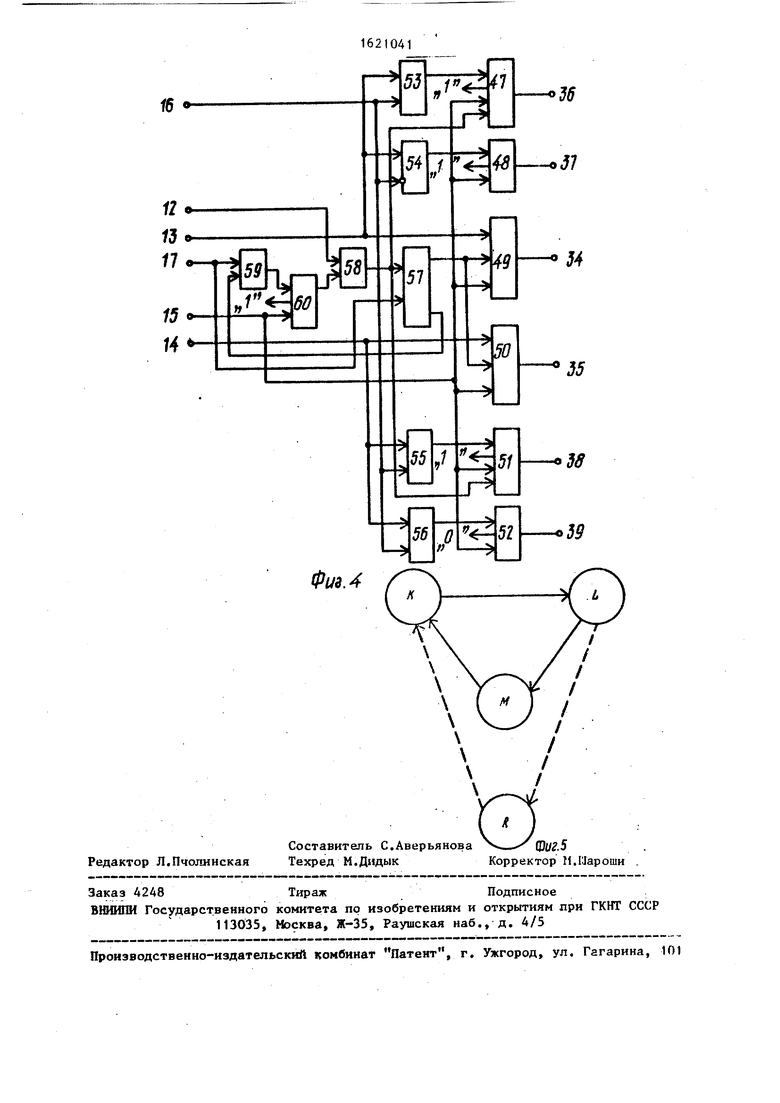

В качестве примера рассмотрим работу предлагаемого коммутационного устройства, реализующего мастичный граф коммутации, представленный на фиг,5, в котором абоненты К, L, М являются основными,а абонент R - резервным. При выходе из строя абонента М на его место подключается абонент R. Для этого коммутационное

25

30

35

устройство обеспечивает установку но-2Q фигурации формируется адрес точки вых связей (R, К) и (L, И), соответствующих резервному абоненту R, которые на фиг.5 показаны пунктиром и разрыв соединений (М, К) и (L, И), соответствующих отказавшему элементу М. В режиме начальной установки соединений параллельно с настройкой связей матричного коммутатора 1 устанавливаются соединения в коммутационных элементах 44, принадлежащим матрицам 43 и 45 коммутации. Точки коммутации в коммутационных элементах 44, принадлежащих матрицам .42 и 46 обнуляются. Для этого на входы 31 коммутатора 4 выходов и 25 коммутатора 5 входов с выходов 38 блока 6 реконфигурации задаются постоянные уровни 1, а на входы 30 коммутатора 4 выходов и 24 коммутатора 5 входов с выходов 36 блока 6 реконфи- ,гурации подаются тактирующие импульсы, синхронно с которыми на входы коммутатора 4 выходов ч на входы 22 коммутатора 5 входов с выхода 34 блока 6 реконфигурации подаются коды адресов точек коммутации. Кроме того, на входы 33 коммутатора 4 выходов и на входы 27 коммутатора 5 входов с выхода 39 блока 6 реконфигурации задаются постоянные уровни О, а на входы 32 коммутатора 4 выходов и на входы 26 коммуна та 5 входов с выхода 38 блока 6 реконфигурации подаются тактирующие импульсы, синхронно с которыми на входы 29 коммутатора 4 выходов и на входы 23 коммутатора 5 входов, с выходов 35 блока 6 реконфигурации подаются коды адресов точек коммутации. В режиме ре40

45

50

55

коммутации, соответствующий выбран ному элементарному коммутатору по адресу АМ. Указанные сигналы посту ют на соответствующие входы коммут ров 4 и 5, что обеспечивает устран соединения в выбранной точке комму ции коммутаторов 4 и 5. Кроме того на выходах 35 блока реконфигурации Формируется адрес точки коммутации соответствующий Ад, на выходах 38 39 блока 6 реконфигурации - код но мера столбца и строки соответствен но. Эти сигналы поступают на соотв ствующие управляющие и адресные вх коммутатора 4 выходов и коммутатор 5 входов, что обеспечивает организ цию соединений в коммутационных элементах 44, принадлежащих матриц 42 и 46.

Формула изобретени

конфигурации, когда вместо абонента М должен быть подключен абонент R, на входы 13 коммутационного устройства задается адрес AW абонента М, на входы 14 коммутационного устройства задается адрес AR абонента R. На вход 16 коммутационного устройства задается признак подключения резерва. В блоке 6 реконфигурации коды адресов Ам и AR обрабатываются таким обпачом, что на выходах 36 Злока 6 реконфигурации Формируется код номера столбца ком чутац очныу элементов 44, принадлежащих матрице коммутации 43 коммутатора 4 выходов и 45 коммутатора 5 входов, на выходах 37 блока 6 реконфигурации формируется уровень О, а на выходах 34 блока 6 рекон

5

0

5

фигурации формируется адрес точки

0

5

0

5

коммутации, соответствующий выбранному элементарному коммутатору по адресу АМ. Указанные сигналы поступают на соответствующие входы коммутаторов 4 и 5, что обеспечивает устранение соединения в выбранной точке коммутации коммутаторов 4 и 5. Кроме того, на выходах 35 блока реконфигурации Формируется адрес точки коммутации, соответствующий Ад, на выходах 38 и 39 блока 6 реконфигурации - код номера столбца и строки соответственно. Эти сигналы поступают на соответствующие управляющие и адресные входы коммутатора 4 выходов и коммутатора 5 входов, что обеспечивает организацию соединений в коммутационных элементах 44, принадлежащих матрицам 42 и 46.

Формула изобретения

0

5

0

5

0

5

0

5

0

5

второй матрицы коммутационных элементов которого соединен с входом выбора строки второтГ матрицы коммутационных элементов коммутатора выходов и подключен к пыхоцу выбора строки второй матрицы коммутационных элементов блока реконфигурации, выход выбора столбца первой матрицы коммутационных элементов которого соединен с входом выбора столбца первой матрицы коммутационных, элементов коммутатора входов и с входом выбора столбца первой матрицы коммутационных элементов коммутатора выходов, вход выбора строки первой матрицы коммутационных элементов которого соединен с выходом выбора строки первой матрицы коммутациошшх элементов блока реконфигурации и с входом выбора строки первой матрицы коммутационных: элементов коммутатора входов, первый и второй информационные выходы которого являются первым и вторым информационными выходами устройства, информационный вход комутатора входов соединен с информационным выходом матричного коммутатора, информационный вход которого подключен к информационному выходу коммутатора выходов, первый и второй информационные входы которого являются riL-pBbiM и вторым информационными входами устройства соответственно.

соединен своими разрядами с вторыми управляющими входами соответствующих коммутационных элементов второй матрицы, разряды входа адреса первой матрицы коммутационных элементов коммутатора выходов подключены к адресным входам соответствующих коммутационных элементов первой матрицы, первые управляющие входы которых соединены с соответствующими разрядами входа выбора столбца первой матрицы коммутационных элементов коммутатора выходов, вход выбора строки первой матрицы коммутационных элементов которого подключен своими разрядами к вторым управляющим входам соответствующих коммутационных элементов первой матрицы, разряды второго информационного входа коммутатора выходов соединены с информационными входами соответствующих коммутационных элементов первой матрицы коммутационных элементов.

столбца первой матрицы коммутационных элементов коммутатора входов, вход выбора строки первой матрицы коммутационных элементов которого своими разрядами подключен к вторым управляющим входам соответствующих коммутационных элементов первой матрицы, информационные выходы которых

являются соответствующими разрядами второго информационного выхода коммутатора входов.

устройства и подключен к управляющим входам мультиплексоров, вход признака подключения резерва блока соединен с управляющими входами дешифраторов и является входом признака подключе5 ния резерва устройства, информационные входы первого и второго дешифраторов соединены с первым информационным входом третьего мультиплексора и являются входом адреса отказав0 шего абонента устройства, вход адреса резервного ресурса устройства соединен с информационными входами третьего и четвертого дешифраторов и с первым информационным входом четвере того мультиплексора, второй информационный вход четвертого мультиплексора соединен с вторым информационным входом третьего мультиплексора и подключен к информационному выходу счетQ чика, тактовый вход которого соединен с сиихровходами первого и пятого типлексоров и подключен к выходу элемента И, первый вход которого является вторым синхровходом устройства,

5 второй вход элемента II подключен к прямому выходу триггера, вход установки в 1 которого подключен к выходу элемента ИЛИ, первый вход которого соединен с выходом переноса счет0 чика, а второй вход - с установочным входом устройства, выходы первого дешифратора подключены к соответствующим разрядам первого информационного входа ервого мультиплексора, второй

5 информационный вход которого соединен с генератором логической единицы устройства, а выход является выходом выбора столбца второй матрицы коммутации блока реконфигурации, выходы вто1316

рого дешифратора подключены к соответствующим разрядам первого информационного входа второго мультиплексора, второй информационный вход кото- рого соединен с генератором логической единицы устройства, а выход является выходом выбора строки второй матрицы коммутационных элементов блока реконфигурации, выходы третье- го дешифратора подключены к соответствующим разрядам первого информационного входа пятого мультиплексора, второй информационный вход которого соединен с генератором логической единицы устройства, а выход является выходом выбора столбца первой матрицы коммутации блока реконфигурации,

Фиг. Z

114

выходы четвертого дешифратора подключены к соответствующим разрядам первого информационного входа шестого мультиплексора, второй информационный вход которого соединен с генератором логического пуля устройства, а выход является выходом выбора строки первой матрицы коммутационных элементов блока реконфигурации, выход адреса второй матрицы коммутационных элементов которого соединен с выходом третьего мультиплексора, выход четвертого мультиплексора подключен . к выходу адреса первой матрицы коммутационных элементов блока реконфигурации.

I

Фи.4

Редактор Л.Пчолинская

Составитель С.Аверьянова 1Д/2.5 Техред М.Дидык Корректор Н.Иароши

| Коммутационное устройство | 1984 |

|

SU1246109A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР V , кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Коммутационное устройство | 1986 |

|

SU1387006A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-01-15—Публикация

1989-01-03—Подача