Сл

1

со

Јъ

СЛ

00

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адресации | 1989 |

|

SU1686449A2 |

| Устройство для адресации блоков памяти | 1986 |

|

SU1388877A1 |

| УСТРОЙСТВО ДЛЯ РАСПРЕДЕЛЕНИЯ ЗАДАНИЙ ПО ПРОЦЕССОРАМ | 1991 |

|

RU2017206C1 |

| Запоминающее устройство с переменным форматом данных | 1981 |

|

SU987678A1 |

| Устройство для адресации блоков памяти | 1988 |

|

SU1575189A1 |

| Устройство для адресации блоков памяти | 1989 |

|

SU1679490A1 |

| Устройство для сопряжения процессоров в однородной вычислительной системе | 1984 |

|

SU1179364A1 |

| Устройство для обмена информацией междуэлЕКТРОННОй ВычиСлиТЕльНОй МАшиНОй(эВМ) и уСТРОйСТВАМи ВВОдА и ВыВОдА | 1979 |

|

SU809140A1 |

| Устройство для вычисления спектраМОщНОСТи | 1978 |

|

SU805191A1 |

| Адаптивное телеизмерительное устройство | 1975 |

|

SU608186A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в качестве модуля для аппаратного взаимного преобразования логических и физических адресов любых функционально законченных блоков (процессоров, блоков памяти и т.д.). Целью изобретения является расширение функциональных возможностей устройства и области его применения за счет обратного преобразования физического адреса блока в его логический адрес. Устройство содержит группу переключателей 1-3 логического адреса, регистр 4 логического адреса, дешифратор 5 логического адреса, первую группу элементов 6 и 7 ИЛИ, блоки 8 и 9 коммутации первой, второй группы, шифратор 11 физического адреса, регистр 13 физического адреса, дешифратор 14 физического адреса, вторую группу элементов 15 и 16 ИЛИ, шифратор 17 логического адреса. Введение регистра 13, дешифратора 14, шифраторов 11, 17 и изменение конструкции блоков коммутации позволяет осуществлять как преобразование логического адреса в физический, так и наоборот, причем прямое и обратное преобразования могут происходить одновременно и независимо друг от друга. 3 ил.

м

является расширение функциональных боэможностей устройства и области его Применения за счет обратного преобразования физического адреса блока в это логический адрес. Устройство содержит группу переключателей 1-3 ло- гического адреса, регистр 4 логического адреса, дешифратор 5 логического адреса, первую группу элементов ИЛИ 6 и 7, блоки 8 и 9 коммутации первой, второй групп, шифратор 11 физического адреса, регистр 13 физического адИзобретение относится к автоматике j вычислительной технике, может быть использовано в качестве модуля для {аппаратного взаимного преобразования Логических и физических адресов любых функционально законченных блоков (процессоров, блоков памяти и т.д.) и является усовершенствованием устройства по авт. св. № 1388877.

Целью изобретения является расширение функциональных возможностей и области применения устройства за счет обратного преобразования физического адреса блока в его логический адрес,

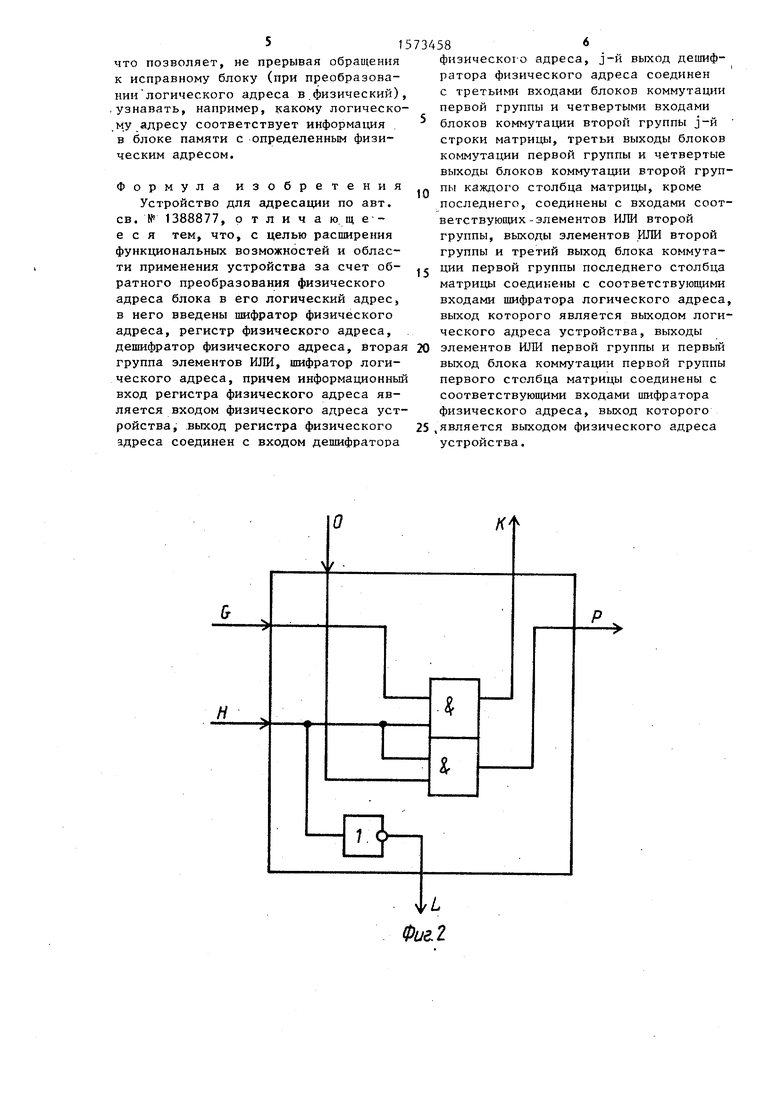

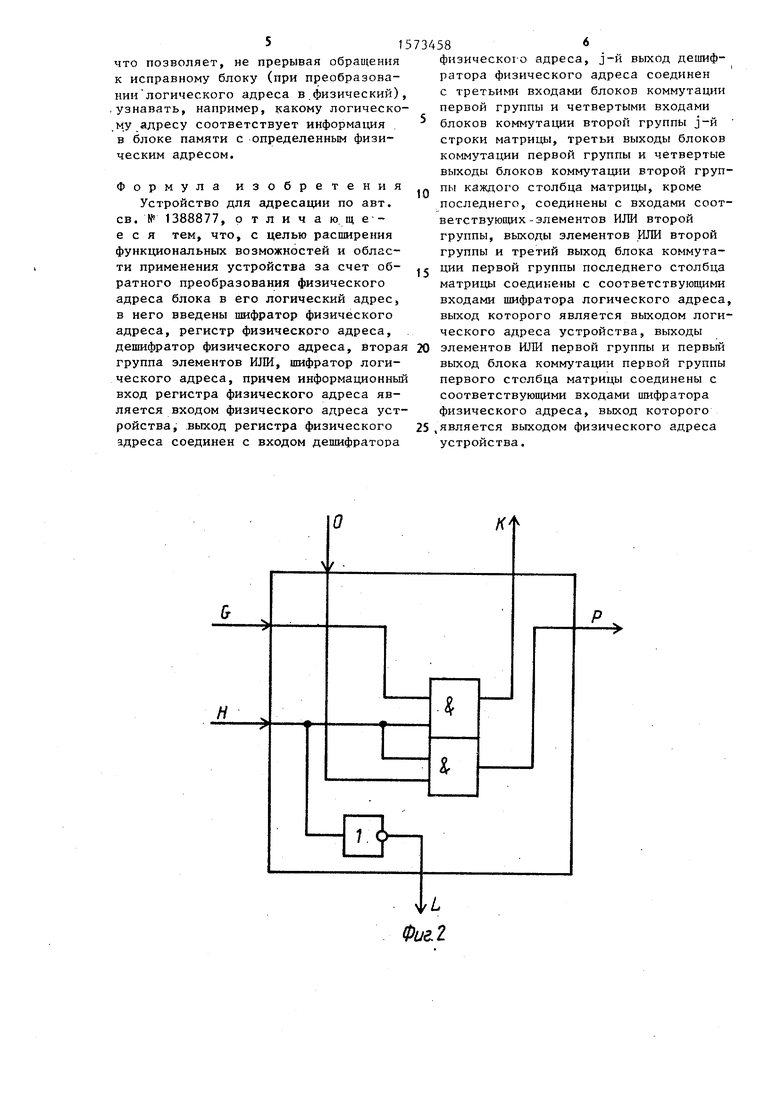

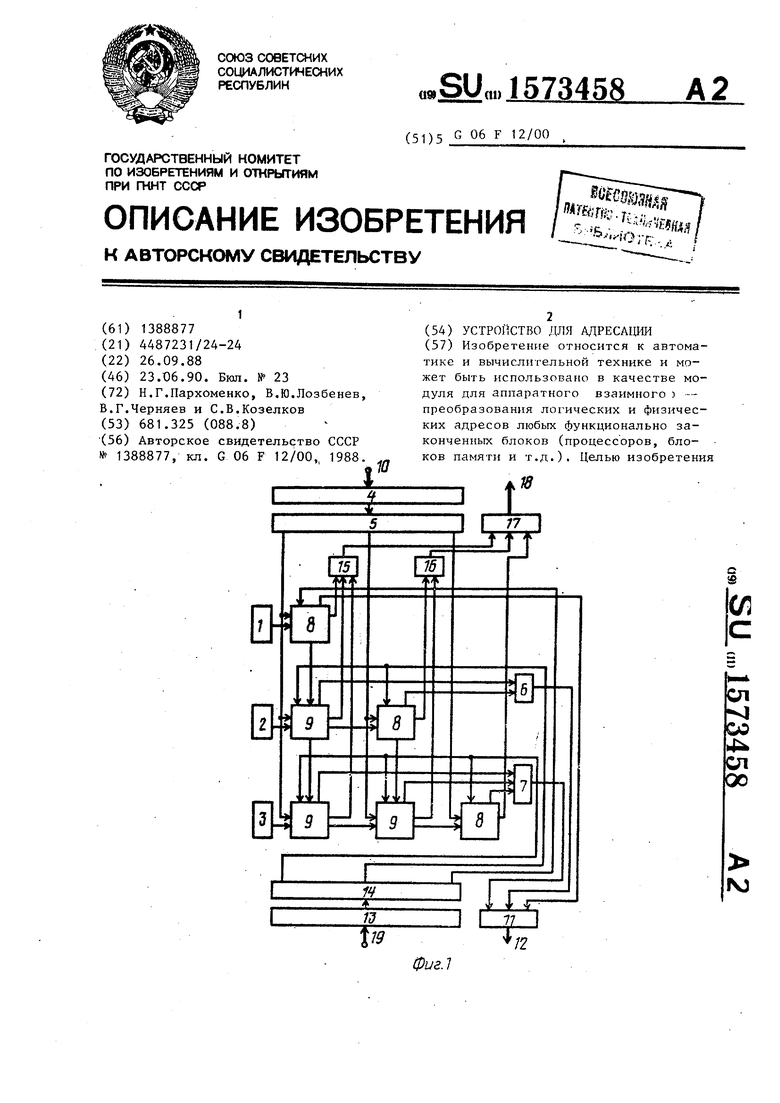

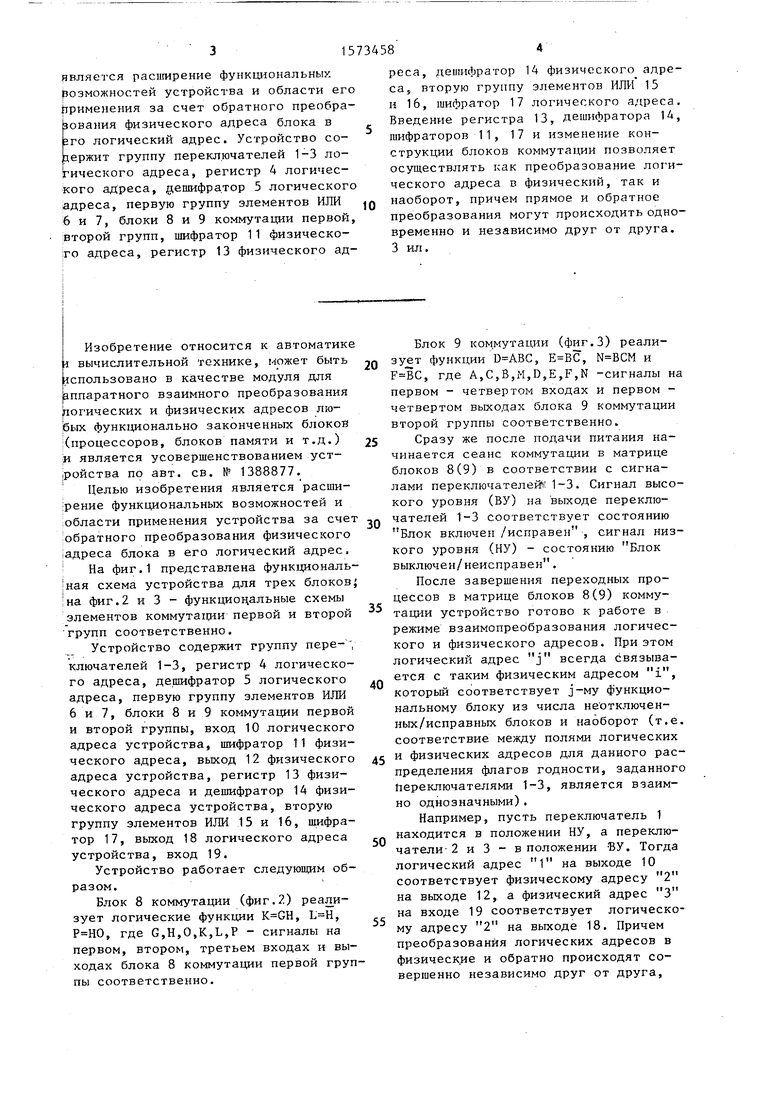

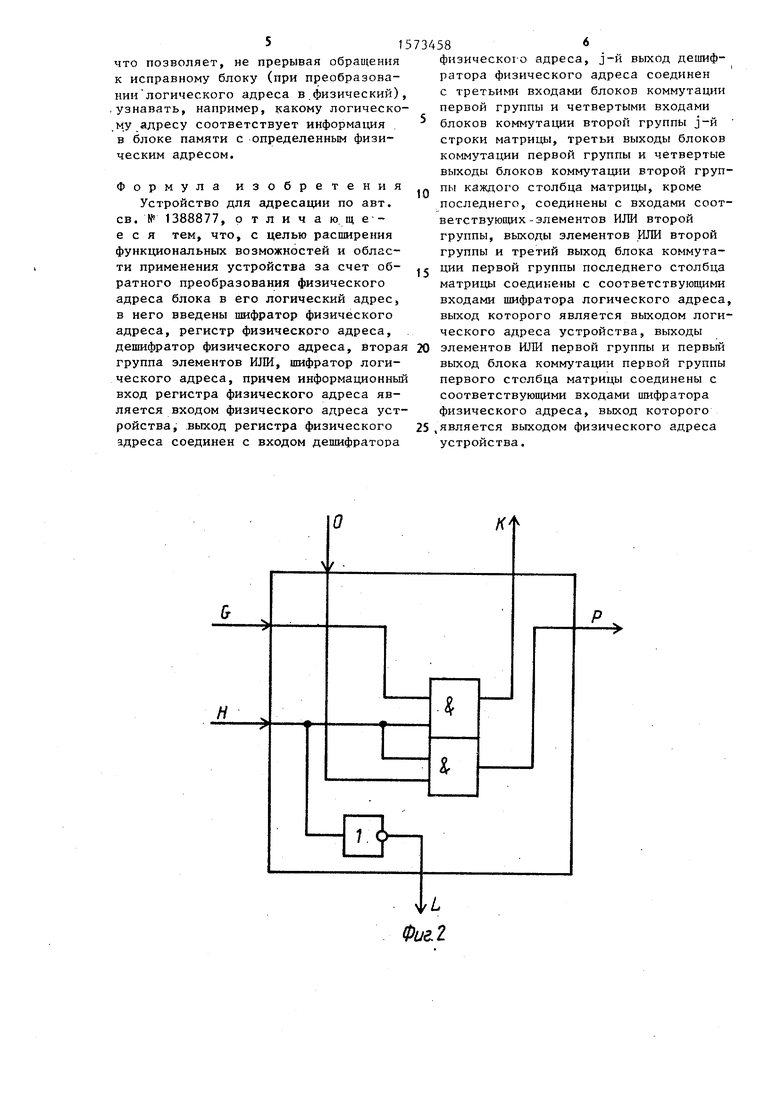

На фиг.1 представлена функциональ- ная схема устройства для трех блоков на фиг.2 и 3 - функциональные схемы элементов коммутации первой и второй групп соответственно.

Устройство содержит группу пере- , ключателей 1-3, регистр 4 логического адреса, дешифратор 5 логического адреса, первую группу элементов ИЛИ 6 и 7, блоки 8 и 9 коммутации первой и второй группы, вход 10 логического адреса устройства, шифратор 11 физического адреса, выход 12 физического адреса устройства, регистр 13 физического адреса и дешифратор 14 физического адреса устройства, вторую группу элементов ИЛИ 15 и 16, шифратор 17, выход 18 логического адреса устройства, вход 19.

Устройство работает следующим образом.

Блок 8 коммутации (фиг.2) реализует логические функции , , , где G,H,0,K,L,P - сигналы на первом, втором, третьем входах и выходах блока 8 коммутации первой группы соответственно.

реса, дешифратор 14 физического адреса s вторую группу элементов ИЛИ 15 и 16, шифратор 17 логического адреса. Введение регистра 13, дешифратора 14, шифраторов 11, 17 и изменение конструкции блоков коммутации позволяет осуществлять как преобразование логического адреса в физический, так и наоборот, причем прямое и обратное преобразования могут происходить одновременно и независимо друг от друга. 3 ил.

0

5

0

5

0

5

0

5

Блок 9 коммутации (фиг.З) реализует функции , , и , где A,C,B,M,D,E,F,N -сигналы на первом - четвертом входах и первом - четвертом выходах блока 9 коммутации второй группы соответственно

Сразу же после подачи питания начинается сеанс коммутации в матрице блоков 8(9) в соответствии с сигналами переключателей - 1 -3. Сигнал высокого уровня (ВУ) на выходе переключателей 1-3 соответствует состоянию Блок включен /исправен , сигнал низкого уровня (НУ) - состоянию Блок выключен/неисправен.

После завершения переходных процессов в матрице блоков 8(9) коммутации устройство готово к работе в режиме взаимопреобразования логического и физического адресов. При этом логический адрес j всегда связывается с таким физическим адресом i, который соответствует j-му функциональному блоку из числа неотключен- ных/исправных блоков и наоборот (т.е. соответствие между полями логических и физических адресов для данного распределения флагов годности, заданного переключателями 1-3, является взаимно однозначными).

Например, пусть переключатель 1 находится в положении НУ, а переключатели 2 и 3 - в положении -БУ. Тогда логический адрес 1 на выходе 10 соответствует физическому адресу 2 на выходе 12, а физический адрес 3 на входе 19 соответствует логическому адресу 2 на выходе 18. Причем преобразования логических адресов в физические и обратно происходят совершенно независимо друг от друга,

5

что позволяет, не прерывая обращения к исправному блоку (при преобразовании логического адреса в физический), узнавать, например, какому логическому адресу соответствует информация в блоке памяти с определенным физическим адресом.

Формула изобретения

Устройство для адресации по авт. св. № 1388877, отличающееся тем, что, с целью расширения функциональных возможностей и области применения устройства за счет обратного преобразования физического адреса блока в его логический адрес, в него введены шифратор физического адреса, регистр физического адреса, дешифратор физического адреса, втора группа элементов ИЛИ, шифратор логического адреса, причем информационны вход регистра физического адреса является входом физического адреса устройства, выход регистра физического адреса соединен с входом дешифратора

н

10

15

20

физическою адреса, j-й выход дешифратора физического адреса соединен с третьими входами блоков коммутации первой группы и четвертыми входами блоков коммутации второй группы j-й строки матрицы, третьи выходы блоков коммутации первой группы и четвертые выходы блоков коммутации второй группы каждого столбца матрицы, кроме последнего, соединены с входами соответствующих -элементов ИЛИ второй группы, выходы элементов ИЛИ второй группы и третий выход блока коммутации первой группы последнего столбца матрицы соединены с соответствующими входами шифратора логического адреса, выход которого является выходом логического адреса устройства, выходы элементов ИЛИ первой группы и первый выход блока коммутации первой группы первого столбца матрицы соединены с соответствующими входами шифратора физического адреса, выход которого 25.является выходом физического адреса устройства.

Ь

Фиг. 1

М

о

&

I

TS.J

Фиг. З

В

D

/у

F

| Устройство для адресации блоков памяти | 1986 |

|

SU1388877A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-06-23—Публикация

1988-09-26—Подача