CS VI

ю ю о

Изобретение относится к автоматике и вычислительной технике и может быть использовано для адресации блоков памяти с преобразованием логического адреса обращения в физический адрес в резервированных ЭВМ.

Целью изобретения является снижение аппаратурных затрат.

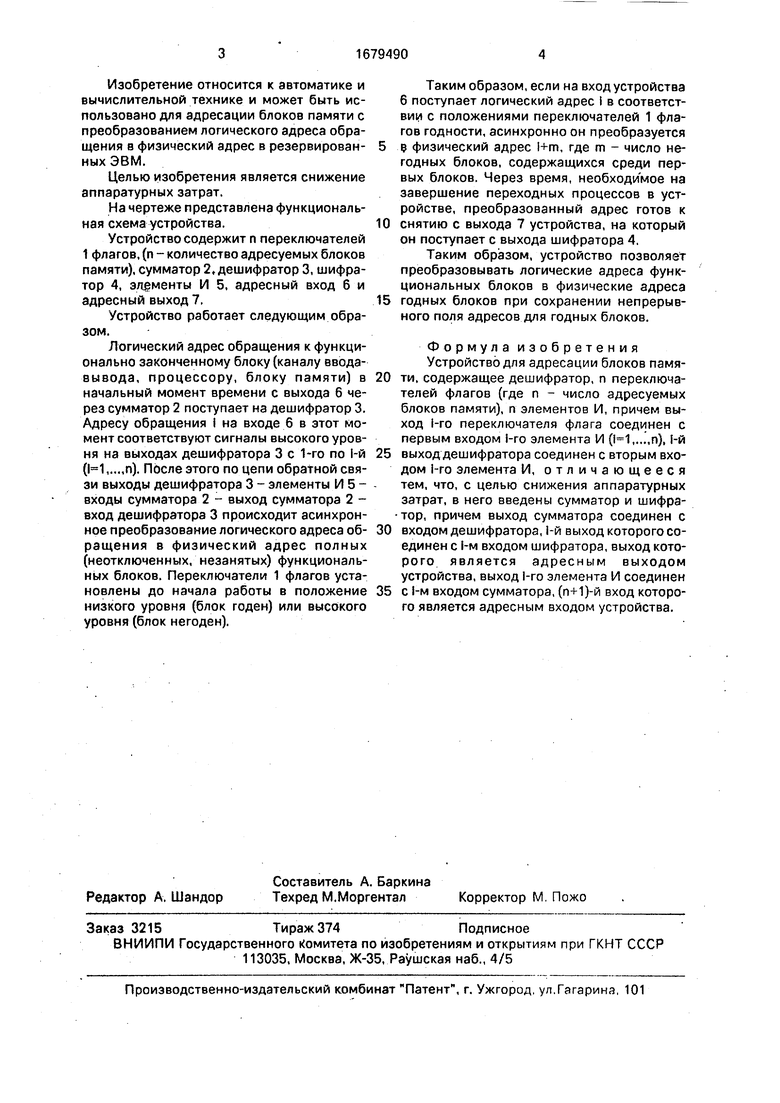

На чертеже представлена функциональная схема устройства.

Устройство содержит п переключателей 1 флагов, (п - количество адресуемых блоков памяти), сумматор 2, дешифратор 3, шифратор 4, элементы И 5, адресный вход 6 и адресный выход,

Устройство работает следующим образом.

Логический адрес обращения к функционально законченному блоку (каналу ввода- вывода, процессору, блоку памяти) в начальный момент времени с выхода 6 через сумматор 2 поступает на дешифратор 3. Адресу обращения I на входе 6 в этот момент соответствуют сигналы высокого уровня на выходах дешифратора 3 с 1-го по 1-й (,...,п). После этого по цепи обратной связи выходы дешифратора 3 - элементы И 5 - входы сумматора 2 - выход сумматора 2 - вход дешифратора 3 происходит асинхронное преобразование логического адреса об- ращения в физический адрес полных (неотключенных, незанятых) функциональных блоков. Переключатели 1 флагов установлены до начала работы в положение низкого уровня (блок годен) или высокого уровня (блок негоден).

0

5

Таким образом, если на вход устройства 6 поступает логический адрес I в соответствии с положениями переключателей 1 флагов годности, асинхронно он преобразуется в физический адрес l+m, где m - число негодных блоков, содержащихся среди первых блоков. Через время, необходимое на завершение переходных процессов в устройстве, преобразованный адрес готов к снятию с выхода 7 устройства, на который он поступает с выхода шифратора 4.

Таким образом, устройство позволяет преобразовывать логические адреса функциональных блоков в физические адреса годных блоков при сохранении непрерывного поля адресов для годных блоков.

Формула изобретения Устройство для адресации блоков памяти, содержащее дешифратор, п переключателей флагов (где п - число адресуемых блоков памяти), п элементов И, причем выход 1-го переключателя флага соединен с первым входом 1-го элемента И (), 1-й

выход дешифратора соединен с вторым входом 1-го элемента И, отличающееся тем, что, с целью снижения аппаратурных затрат, в него введены сумматор и шифра- тор, причем выход сумматора соединен с

входом дешифратора, 1-й выход которого соединен с i-м входом шифратора, выход которого является адресным выходом устройства, выход 1-го элемента И соединен

с 1-м входом сумматора, (п+1)-й вход которого является адресным входом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адресации | 1988 |

|

SU1675892A1 |

| Устройство для адресации блоков памяти | 1988 |

|

SU1575189A1 |

| Устройство для адресации | 1988 |

|

SU1573458A2 |

| Устройство для адресации блоков памяти | 1986 |

|

SU1388875A2 |

| Устройство для адресации блоков памяти | 1988 |

|

SU1580375A1 |

| Устройство для адресации блоков памяти | 1986 |

|

SU1394217A1 |

| Устройство для адресации | 1989 |

|

SU1686449A2 |

| Устройство для адресации памяти | 1986 |

|

SU1388876A2 |

| Устройство для адресации памяти | 1989 |

|

SU1656543A1 |

| Устройство для обработки данных | 1979 |

|

SU849222A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для адресации блоком памяти с преобразованием логического адреса обращения в физический адрес в резервированных ЭВМ. Целью изобретения является снижение аппаратурных затрат. Устройство содержит п переключателей 1 флагов, сумматор 2, дешифратор 3, шифратор 4, элементы И 5 и имеет адресный вход 6 и адресный выход 7. Т ил.

| Устройство для адресации памяти | 1985 |

|

SU1298755A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

| Устройство для адресации блоков памяти | 1987 |

|

SU1481777A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-09-23—Публикация

1989-09-11—Подача