22 Z4

12

&

V)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адресации блоков памяти | 1986 |

|

SU1388877A1 |

| Устройство для адресации | 1988 |

|

SU1573458A2 |

| Устройство для сопряжения | 1990 |

|

SU1784984A1 |

| Устройство для адресации блоков памяти | 1984 |

|

SU1198565A1 |

| Коммутационное устройство | 1984 |

|

SU1246109A1 |

| Устройство для адресации | 1989 |

|

SU1686449A2 |

| Устройство для адресации блоков памяти | 1988 |

|

SU1571595A2 |

| Устройство для сопряжения группы из М вычислительных машин с группой из К абонентов | 1986 |

|

SU1310830A1 |

| Запоминающее устройство с переменным форматом данных | 1981 |

|

SU987678A1 |

| Устройство для адресации блоков памяти | 1989 |

|

SU1661774A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для адресации блоков памяти в системе памяти. Целью изобретения является расширение функциональных возможностей устройства за счет придания ему функции самоконтроля. Устройство содержит группу переключателей 1...4, регистр 5 адреса, дешифратор 6 адреса, три группы элементов ИЛИ 7...9,17 и 18, группу элементов 19 ИСКЛЮЧАЮЩЕЕ ИЛИ, выходной элемент ИЛИ 20, группу элементов И 21, вход 22 "Контроль", выход 23 "Неисправность", вход 24 "Флаг". 1 ил.

Щ Щ Ш (Д

ел 1

СП

00 CD

Изобретение относится к автомрти- ке и вычислительной технике и может быть использовано для адресации блоков памяти в системе памяти.

Целью изобретения является расширение функциональных возможностей устройства за счет придания ему функции самоконтроля,

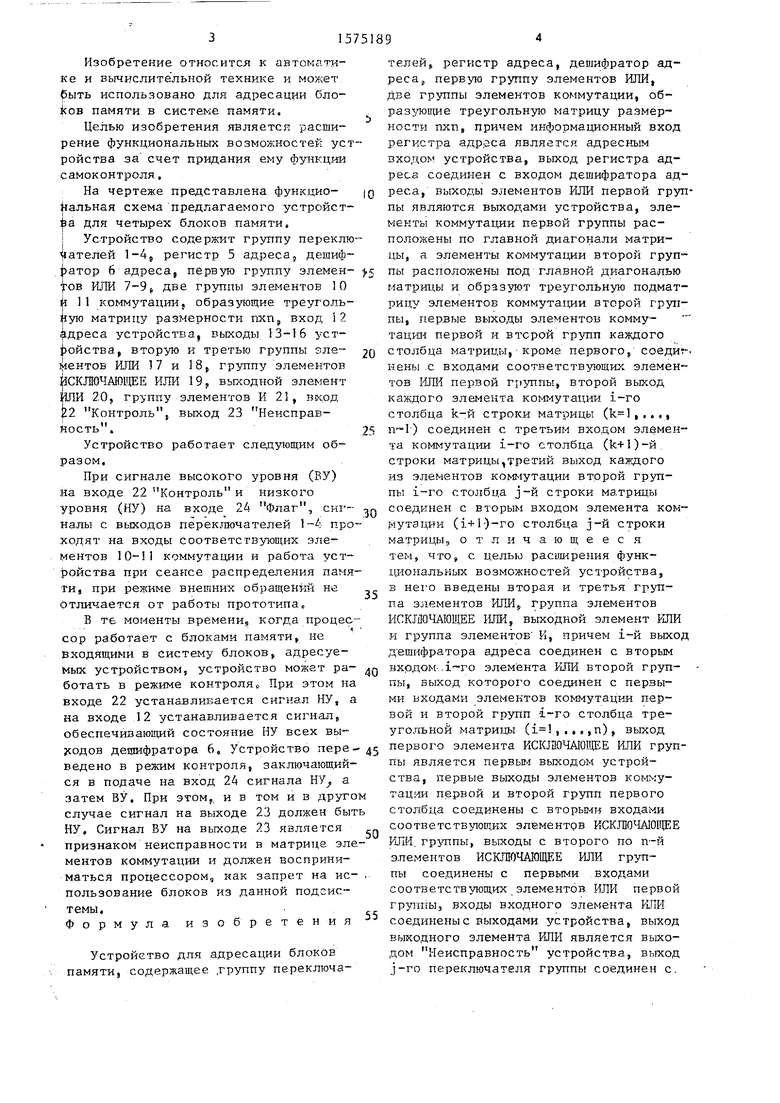

На чертеже представлена функцио- Нальная схема предлагаемого устройства для четырех блоков памяти,

Устройство содержит группу переключателей 1-4, регистр 5 адреса, дешифратор 6 адреса8 первую группу элемен- Тов ИЛИ 7-9s две группы элементов 10 и 11 коммутации, образующие треуголь- йую матрицу размерности пхпв вход 1 адреса устройства, выходы 13-16 устройства, вторую и третью группы эле- ментов ИЛИ 17 и 18, группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 19, выходной элемент

I

ИЛИ 20, группу элементов И 21, вкод 22 Контроль, выход 23 Неисправность.

Устройство работает следующим образом.

При сигнале высокого уровня (ВУ) на входе 22 Контроль и низкого уровня (НУ) на входе 2 Флаг, сиг- Налы с выходов переключателей 1- проходят на входы соответствующих элементов 10-И коммутации и работа устройства при сеансе распределения памяти, при режиме внешних обращений нг отличается от работы прототипа

В те моменты времени, когда процессор работает с блоками памяти, не Входящими в систему блоков, адресуемых устройством, устройство может pa- ботать в режиме контроля„ При этом на входе 22 устанавливается сигнал НУ, а на входе 12 устанавливается сигнал, обеспечивающий состояние НУ всех выходов дешифратора 6, Устройство пере- ведено в режим контроля, заключающийся в подаче на вход 24 сигнала НУ а затем ВУ. При этом,, и в том и в друго случае сигнал на выходе 23 должен быт НУ. Сигнал ВУ на выходе 23 является признаком неисправности в матрице элементов коммутации и должен восприниматься процессором,, как запрет на ис- пользование блоков из данной подсис

темы.

Формула изобретения

Устройство для адресации блоков памяти, содрржащее .группу переключа

з 0

5

д

Q 5

5

5

телейе регистр адреса, дешифратор адреса t первую группу элементов ИЛИ, две группы элементов коммутации, образующие треугольную матрицу размерности пхпв причем информационный вход регистра адреса является адресным входом устройства, выход регистра адреса соединен с входом дешифратора адреса, выходы элементов ИЛИ первой группы являются выходами устройства, элементы коммутации первой группы расположены по главной диагонали матрицы, а элементы коммутации второй группы расположены под главной диагональю патрицы и образуют треугольную подматрицу элементов коммутации второй группы, первые выходы элементов коммутации первой и второй групп каждого столбца матрицы, кроме первого, соедиг-. некы с входами соответствующих элементов ИЛИ первой группы, второй выход каждого элемента коммутации 1-го столбца k-й строки матрицы (,,.,, iv-1) соединен с третьим входом элемента коммутации 1-го столбца (k+l)-fl строки матрицы,третий выход каждого из элементов коммутации второй группы 1-го столбца j-й строки матрицы соединен с вюрым входом элемента коммутации (i+I)-ro столбца j-й строки матрицы, отличающееся тем, что, с целью расширения функциональных возможностей устройства, в него введены вторая и третья группа элементов ИЛИ, группа элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходной элемент ИЛИ и группа элементов К, причем i-й выход дешифратора адреса соединен с вторым входом элемента ИЛИ второй группы, выход которого соединен с первыми входами элементов коммутации первой и второй групп 1-го столбца треугольной матрицы (,,,,,п), выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ группы является первым выходом устройства, первые выходы элементов коммутации первой и второй групп первого столбца соединены с вторыми входами соответствующих элвментрв ИСКЛЮЧАЮЩЕЕ ИЛИ группы, выходы с второго по п-й элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы соединены с первыми входами соответствующих элементов ИЛИ первой группы, входы входного элемента ИЛИ соединены с выходами устройства, выход выходного элемента ИЛИ является выходом Неисправность устройства, выход j-ro переключателя группы соединен с

первым входом j-ro элемента К группы,соединен с вторым входом j-ro элемен вторые входы которых объединены .я сое-та коммутации (j«l,..,,n) первого динены с входом Контроль устройстпстолбца (-треугольной матрицы, первые ва, выход j-ro элемента И группы сое-входы элементов ИЛИ всех групп объединен с вторым входом j-ro элемента 5динены и соединены с входом Флаг ИЛИ третьей группы, выход которогоустройства.

| Устройство для адресации блоков памяти | 1986 |

|

SU1388877A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-06-30—Публикация

1988-09-26—Подача