сл J

сл

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Оперативное запоминающее устройство | 1990 |

|

SU1751812A1 |

| Устройство для управления сверхоперативной буферной памятью мультипроцессорной ЭВМ | 1981 |

|

SU980097A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1991 |

|

SU1807516A1 |

| СИСТЕМА ДЛЯ ОБРАБОТКИ КОМПОНЕНТ ПРОГРАММ И СХЕМА УПРАВЛЕНИЯ ПАМЯТЬЮ ДЛЯ ТРАНСПОРТНОГО ПРОЦЕССОРА | 1995 |

|

RU2145728C1 |

| Устройство обмена информацией | 1987 |

|

SU1532941A1 |

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1984 |

|

SU1187174A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ И ДЕМУЛЬТИПЛЕКСИРОВАНИЯ КОМПОНЕНТНЫХ СИГНАЛОВ В ЦИФРОВЫХ ПОТОКАХ | 2012 |

|

RU2514092C2 |

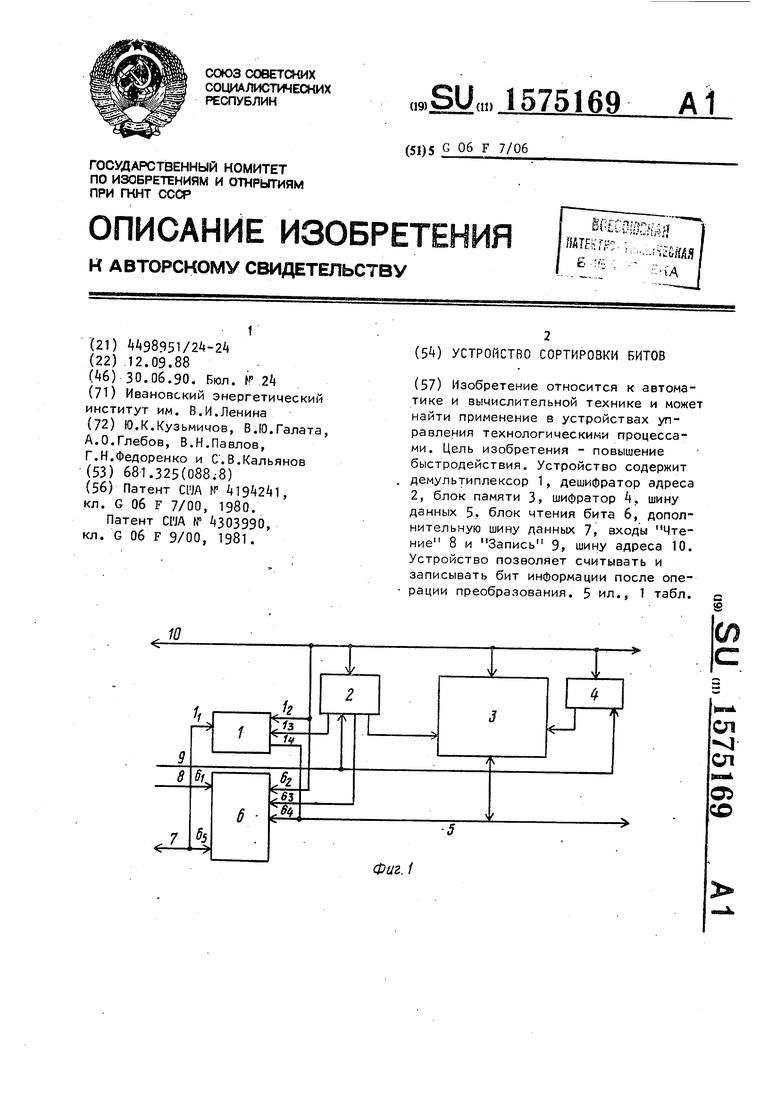

Изобретение относится к автоматике и вычислительной технике и может найти применение в устройствах управления технологическими процессами. Цель изобретения - повышение быстродействия. Устройство содержит демультиплексор 1, дешифратор адреса 2, блок памяти 3, шифратор 4, шину данных 5, блок чтения бита 6, дополнительную шину данных 7, входы "Чтение" 8 и "Запись" 9, шину адреса 10. Устройство позволяет считывать и записывать бит информации после операции преобразования. 5 ил., 1 табл.

о со

Изобретение относится ,к автоматике и вычислительной технике и может найти применение в устройствах управления технологическими процессами.

Цель изобретения - повышение быстродействия.

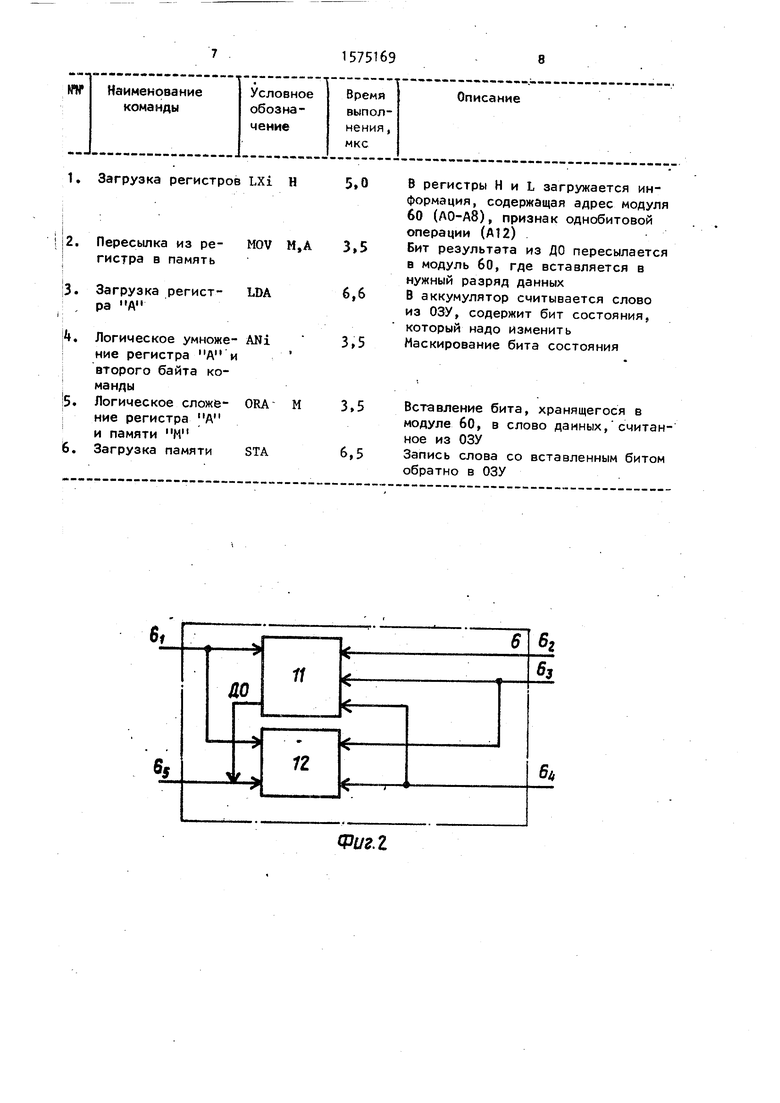

На фиг. 1 приведена блок-схема устройства сортировки битов на фиг. - варианты построения блока чтения бита на фиг. 4 - временная диаграмма работы прототипа;на фиг.5 временная диаграмма работы устройства сортировки битов о

Устройство содержит демультиплек- сор 1, дешифратор 2 адреса, блок 3 памяти, шифратор 4, шину 5 данных, блок 6 чтения бита, дополнительную шину 7 данных, входы Чтение 8 и Запись 9, шину 10 адреса, элементы вариантов построения блока 6 с 11 по 1.

Демультиплексор 1 принимает по входу 1, значение младшего бита Д0 шины 7 данных и на выходе устанавливает его в разряд, указанный группой адресных проводников с шины 10 адреса и поступающий на его вход. В остальных разрядах выхода 14 устанавливается логическая 1. Вход выборки 1Э запрещает (разрешает) рабо-у ту демультиплексора 1.

Дешифратор 2 адреса выбирает элементы 1, 3 6 при их адресации с шины 10 адреса, о учетом состояния входа 9 устройства. Демультиплексор 1 выбирается при появлении адреса однобитовых операций на шине 10 адреса и сигнала Запись на вход 9 устройства. Блок 3 памяти выбирается при появлении адреса однобитовых операций или при адресации блока памяти. Блок 6 чтения бита выбирается при появлении адреса однобитовых операций и отсутствии сигнала Запись.

Блок 3 памяти служит для хранения данных и состоит из одноразрядных элементов памяти, адресные входы которых присоединены к шине 10 адреса, входы записи/считывания, к шифратору 4, входы-выходы данных - к разрядам шины 5 данных, а входы выборки - к выходу дешифратора 2.

Шифратор k служит для управления входом Запись-чтение блока 3 памяти. Если ла адресный вход шифратора А пр иходит адрес однобитовой опера

Q 5

0

5

5

0

5

0

5

0

ции, то на всех разрядах выхода устанавливается значение, соответствующее сигналу Чтение, за исключением разряда для битовой операции (номер разряда указан на шине 10 адреса), В остальных случаях все разряды выхода принимают значение, равное значению управляющего входа шифратора 4.

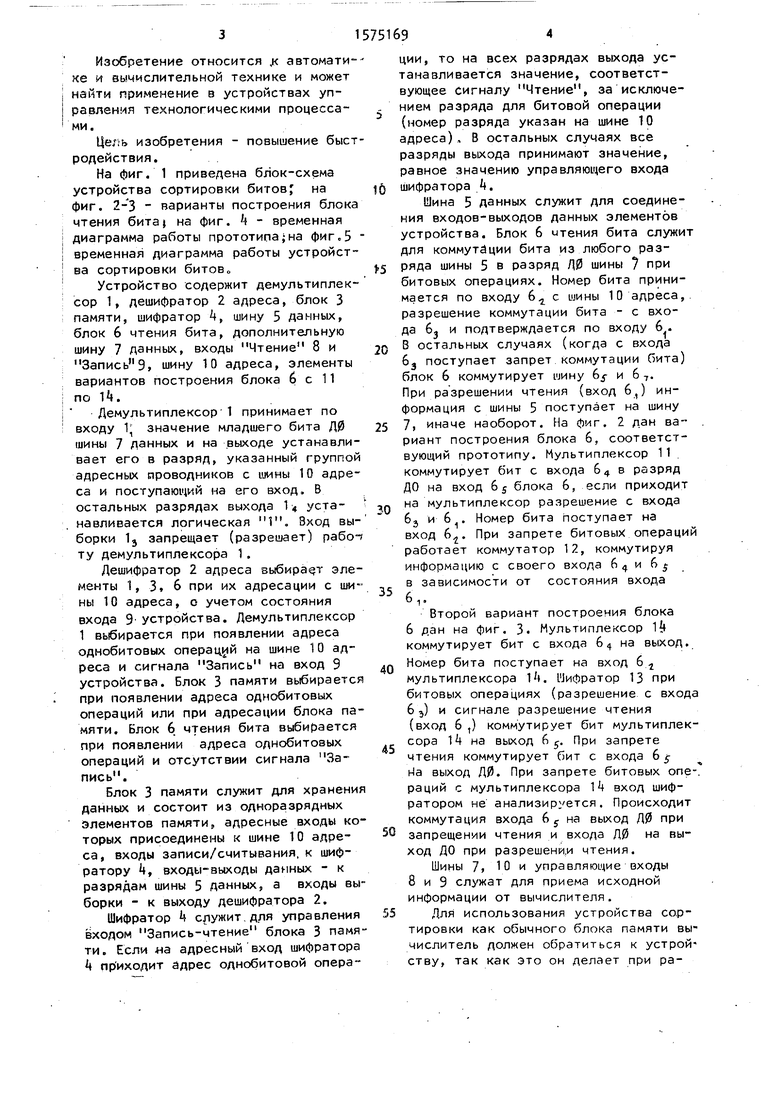

Шина 5 данных служит для соединения входов-выходов данных элементов устройства. Блок 6 чтения бита служит для коммутации бита из любого разряда шины 5 в разряд Д0 шины 7 при битовых операциях. Номер бита принимается по входу 6г с шины 10 адреса, разрешение коммутации бита - с входа 6 и подтверждается по входу 6 . В остальных случаях (когда с входа 63 поступает запрет коммутации бита) блок 6 коммутирует шину и 6 7. При разрешении чтения {вход 6,) информация с шины 5 поступает на шину 7, иначе наоборот. На фиг. 2 дан вариант построения блока 6, соответствующий прототипу. Мультиплексор 11 коммутирует бит с входа 64 в разряд ДО на вход 65 блока 6, если приходит на мультиплексор разрешение с входа 63 и 6 . Номер бита поступает на вход 62. При запрете битовых операций работает коммутатор 12, коммутируя информацию с своего входа 64 и 6 $ в зависимости от состояния входа 6V

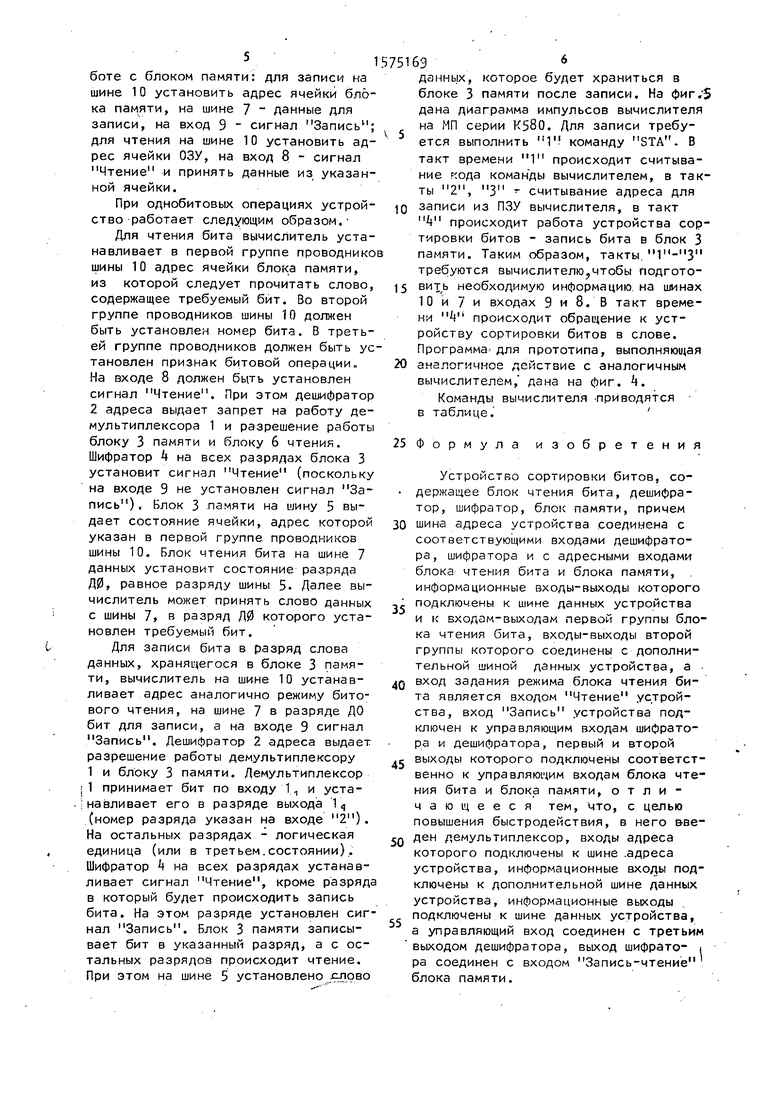

Второй вариант построения блока 6 дан на фиг. 3. Мультиплексор 1 коммутирует бит с входа 64 на выход.

Номер бита поступает на вход 6 г мультиплексора 1. Шифратор 13 при битовых операциях (разрешение с входа 6 э) и сигнале разрешение чтения (вход 6 t) коммутирует бит мультиплексора 14 на выход 6 у. При запрете чтения коммутирует бит с входа 65 Иа выход Д0. При запрете битовых one- раций с мультиплексора 14 вход шифратором не анализируется. Происходит коммутация входа 6s на выход Д0 при запрещении чтения и входа Д0 на выход ДО при разрешении чтения.

Шины 7 Ю и управляющие входы 8 и 9 служат для приема исходной информации от вычислителя.

Для использования устройства сортировки как обычного блока памяти вычислитель должен обратиться к устройству, так как это он делает при раv 5

515751

боте с блоком памяти: для записи на шине 10 установить адрес ячейки блока памяти, на шине 7 данные для записи, на вход 9 - сигнал Запись ; для чтения на шине 10 установить адрес ячейки ОЗУ, на вход 8 - сигнал Чтение и принять данные из указанной ячейки.

При однобитовых операциях устрой- JQ ство работает следующим образом.

Для чтения бита вычислитель устанавливает в первой группе проводников шины 10 адрес ячейки блока памяти, из которой следует прочитать слово, щ содержащее требуемый бит. Во второй группе проводников шины 10 должен быть установлен номер бита. В третьей группе проводников должен быть установлен признак битовой операции. 20 На входе 8 должен быть установлен сигнал Чтение. При этом дешифратор 2 адреса выдает запрет на работу де- мультиплексора 1 и разрешение работы блоку 3 памяти и блоку 6 чтения. 25 Шифратор k на всех разрядах блока 3 установит сигнал Чтение (поскольку на входе 9 не установлен сигнал Запись), Блок 3 памяти на шину 5 выдает состояние ячейки, адрес которой 30 указан в первой группе проводников шины 10. Блок чтения бита на шине 7 данных установит состояние разряда Д0, равное разряду шины 5. Далее вычислитель может принять слово данных -,, с шины 7, в разряд Д0 которого установлен требуемый бит.

Для записи бита в разряд слова анных, хранящегося в блоке 3 памяти, вычислитель на шине 10 устанав- лп ивает адрес аналогично режиму битового чтения, на шине 7 в разряде ДО ит для записи, а на входе 9 сигнал Запись. Дешифратор 2 адреса выдает разрешение работы демультиплексору 1 и блоку 3 памяти. Демультиплексор 1 принимает бит по входу 11 и устаавливает его в разряде выхода 1,, (номер разряда указан на входе 2). На остальных разрядах - логическая 5Q единица (или в третьем.состоянии). ифратор А на всех разрядах устанавивает сигнал Чтение, кроме разряда в который будет происходить запись бита. На этом разряде установлен сигнал Запись. Блок 3 памяти записывает бит в указанный разряд, а с остальных разрядов происходит чтение. При этом на шине 5 установлено .слово

45

5

751

JQ

щ 20 25 30 -,,

лп 5Q

45

636

данных, которое будет храниться в

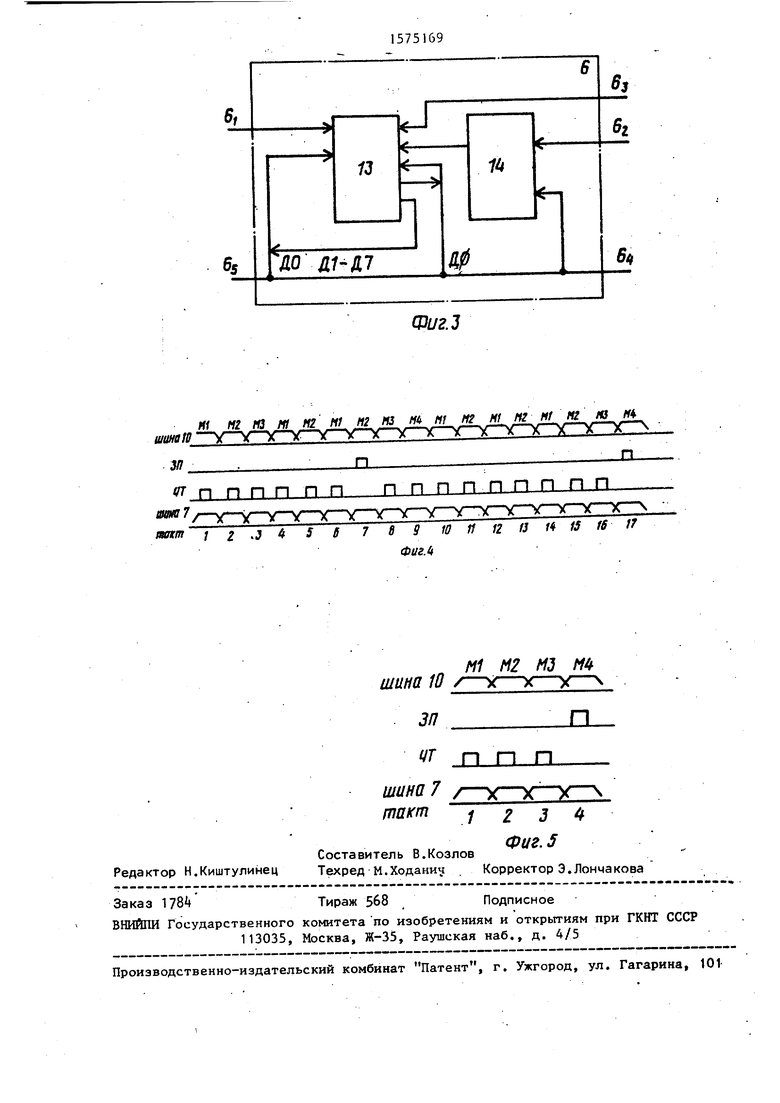

блоке 3 памяти после записи. На фиг. 5 дана диаграмма импульсов вычислителя на МП серии К580. Для записи требуется выполнить 1 команду STA. В такт времени 1 происходит считывание гсода команды вычислителем, в такты 2, 3 - считывание адреса для записи из ПЗУ вычислителя, в такт V происходит работа устройства сор- тмровки битов - запись бита в блок 3 памяти. Таким образом, такты требуются вычислителю.,чтобы подготовить необходимую информацию на шинах 10 и 7 и входах 9 и 8. В такт времени V1 происходит обращение к устройству сортировки битов в слове. Программа для прототипа, выполняющая аналогичное действие с аналогичным вычислителем, дана на фиг. .

Команды вычислителя приводятся в таблице.

Формула изобретения

Устройство сортировки битов, содержащее блок чтения бита, дешифратор, шифратор, блок памяти, причем шина адреса устройства соединена с соответствующими входами дешифратора, шифратора и с адресными входами блока чтения бита и блока памяти, информационные входы-выходы которого подключены к шине данных устройства и к входам-выходам первой группы блока чтения бита, входы-выходы второй группы которого соединены с дополнительной шиной данных устройства, а вход задания режима блока чтения бита является входом Чтение устройства, вход Запись устройства подключен к управляющим входам шифратора и дешифратора, первый и второй выходы которого подключены соответственно к управляющим входам блока чтения бита и блока памяти, отличающееся тем, что, с целью повышения быстродействия, в него в-ве- ден демультиплексор, входы адреса которого подключены к шине адреса устройства, информационные входы подключены к дополнительной шине данных устройства, информационные выходы подключены к шине данных устройства, а управляющий вход соединен с третьим выходом дешифратора, выход шифрато- i pa соединен с входом Запись-чтение1 блока памяти.

k. Логическое умноже- ANi ние регистра А и второго байта команды

5,0 В регистры Н и L загружается информация, содержащая адрес модуля 60 (АО-А8), признак однобитовой операции (А12)

Маскирование бита состояния

и памяти М

М

Вставление бита, хранящегося в

модуле 60, в слово данных, считанное из ОЗУ

6,5 Запись слова со вставленным битом обратно в ОЗУ

Фиг. 2

и/оно Ш М

т т из nt HZ т т нз т т т га нг / нг to /к.

XL

XL

Редактор Н.Киштулинец

Составитель В.Козлов

Техред М.ХоданнчКорректор Э.Лончакова

Фиг.З

XL

XL

шина JO

ЗП

М1 М2 МЗ Mb

П

w п п п

шит 7 такт

| Патент США N° 4194241, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США № 4303990, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-06-30—Публикация

1988-09-12—Подача