оо

4

Изобретение относится к вычислительной технике и может быть использовано в устройствах цифровой обработки сигналовt в частности в цифровых фильтрах.

Цель изобретения - сокращение погрешности вычисления при сохранении разрядности сомножителей,

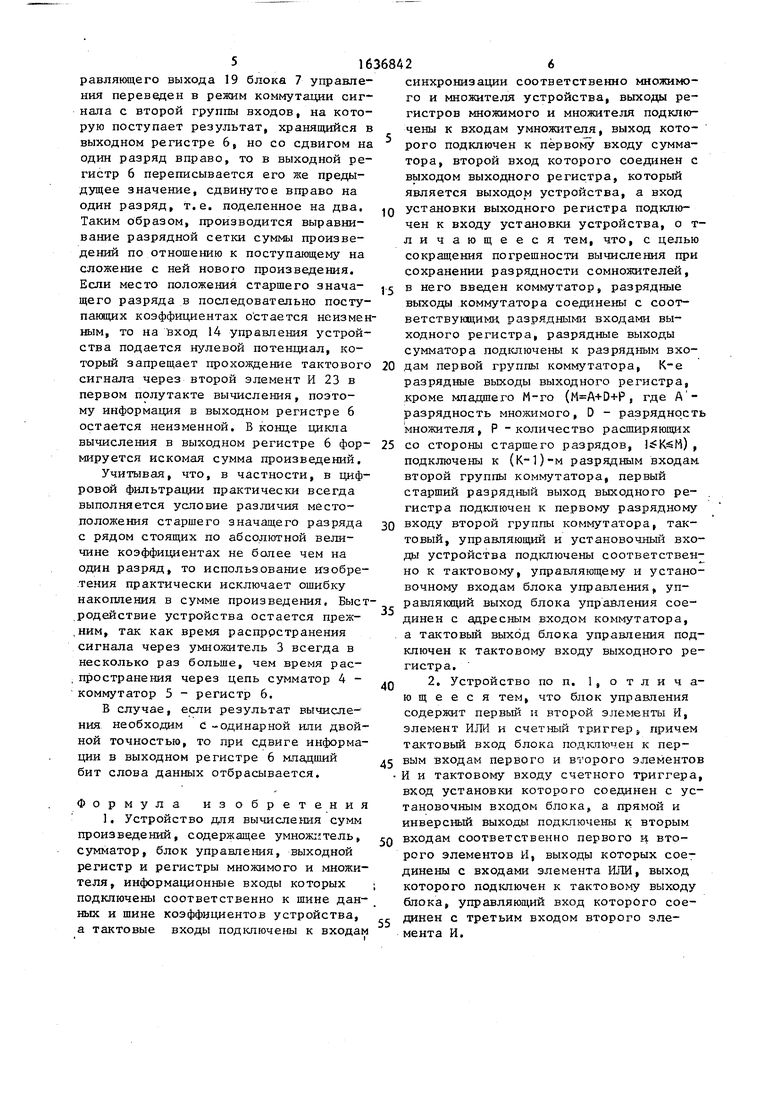

На чертеже изображена структурная схема устройства для вычисления сумм произведений.

Устройство содержит регистр 1 множимого, регистр 2 множителя, умножи

поступление данных и коэффициентов4 организуется внешним устройством так, j что абсолютное значение каждого нового коэффициента больше предыдущего, но меньше последующего. Это/позволяет добиться того, что старший значащий раз- ряд коэффициента располагается в старшем разряде (не считая самого старшего знакового разряда) слова, поступающего по шине 9 коэффициентов в регистр 2 множителя,

Каждый такт вычисления, равный по длительности двум тактам сигнала, пос

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1981 |

|

SU1007101A1 |

| Устройство для умножения | 1980 |

|

SU960805A1 |

| Устройство для умножения на коэффициенты | 1984 |

|

SU1242925A1 |

| УСТРОЙСТВО ВЫЧИСЛЕНИЯ СУММ ПРОИЗВЕДЕНИЙ | 2006 |

|

RU2306595C1 |

| Устройство для умножения | 1985 |

|

SU1254473A1 |

| УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249845C1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| Вычислительное устройство | 1988 |

|

SU1532917A1 |

| Устройство для умножения | 1981 |

|

SU1018115A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах цифровой обработ Ю ки сигналов, в частности в цифровых фильтрах. Цель изобретения - сокращение погрешности вычисления при сохранении разрядности сомножитечей. Устройство содержит регистр 1 множимого, регистр 2 множителя, умножитель 3, сумматор 4, коммутатор 5, выходной регистр 6, блок 7 управления, шину 8 данных, шину 9 коэффициентов, входы 10, 11 синхронизации множимого и множителя, входы 12, 13, 14 установки, тактирования и управления, выход 15 результата, входы 16, 17, 18 установки, тактирования и управления блока 7 и выходы 19, 20 управления и тактирования блока 7. Блок 7 управления содержит счетный триггер 21, элементы И 22, 23, элемент ИЛИ 24. 1 з.п. ф-лы, 1 ил. с (О

тель 3, сумматор 4, коммутатор 5, вы-15 тупающего на вход 13 тактирования ходной регистр 6, блок 7 управления, шину 8 данных, шину 9 коэффициентов, входы 10 и 11 синхронизации соответустройства, делится на два полутак На протяжении первого полутакта, к да управляющий сигнал с выхода 19 ка 7 управления переводит коммутат 5 в режим коммутации сигнала, пост ющего на разрядные входы второй гр пы входов коммутатора 5 на его вых осуществляется собственно операция ножения в умножителе 3 очередного ва данных с выхода регистра 1 множ го на соответствующий ему коэффици поступающий с выхода регистра 2 мн теля. Во время второго полутакта, да коммутатор 5 пропускает на свой ход сигналы, поступающие на разряд входы первой группы входов, произв дится суммирование произведений с хода умножителя 3 с уже частично н копленной суммой произведений и за пись новой частично накопленной су мы произведений в выходной регистр В этом случае запись в выходной ре гистр 6 осуществляется тактовым им пульсом, проходящим через элементы 22 и ИЛИ 24.

ственно множимого и множителя, входы 12-14 соответственно установки, тактирования и управления устройства, выход 15 результата, входы 16-18 соответственно установки, тактирования и управления блока 7 управления и выходы 19 и 20 соответственно управления и тактирования блока 7 управления. Блок 7 управления содержит счетный триггер 21, первый 22 и второй 23 элементы И и элемент ИЛИ 24.

Устройство работает следующим образом.

Вначале каждого цикла вычисления . суммы произведений на вход 12 установки устройства поступает импульс, который обнуляет выходной регистр 6 и триггер 21. Последнее необходимо для того, чтобы обеспечить фазировку тактовых сигналов, поступающих на тактовый вход выходного регистра 6. Затем на вход 13 тактирования устройства начинают поступать тактовые импульсы, причем их частота в два раза выше, чем тактовая частота, поступающая на входы 10 и 11 синхронизации множимого и множителя. В качестве сигналов для тактирования регистров 1 и 2 множимого и множителя при определенных условиях можно использовать сигнал с выхода 19 управления блока 7 управления

Синхронно с каждым вторым тактовым импульсом, поступающим на вход 13 так тирования устройства, на шины 8 и 9 данных и коэффициентов поступают из внешнего устройства слова данных и коэффициентов. Причем последовательность их поступления такова, что пер выми поступают минимальный по абсолютному значению коэффициент и соответствующее ему слово данных. Последующее

э5 тупающего на вход 13 тактирования

0

5

0

5

0

0

5

5

устройства, делится на два полутакта. На протяжении первого полутакта, когда управляющий сигнал с выхода 19 блока 7 управления переводит коммутатор 5 в режим коммутации сигнала, поступающего на разрядные входы второй группы входов коммутатора 5 на его выход, осуществляется собственно операция умножения в умножителе 3 очередного слова данных с выхода регистра 1 множимого на соответствующий ему коэффициент, поступающий с выхода регистра 2 множителя. Во время второго полутакта, когда коммутатор 5 пропускает на свой выход сигналы, поступающие на разрядные входы первой группы входов, производится суммирование произведений с выхода умножителя 3 с уже частично накопленной суммой произведений и запись новой частично накопленной суммы произведений в выходной регистр 6. В этом случае запись в выходной регистр 6 осуществляется тактовым импульсом, проходящим через элементы И 22 и ИЛИ 24.

В случае, если старший значащий разряд вновь поступающего на умножение коэффициента превышает на один разряд положение старшего значащего разряда предыдущего коэффициента, то этот коэффициент все равно подается так, что его старший значащий разряд располагается в старшем значащем разряде слова на шине 9 коэффициентов, т.е. деленный на 2 по отношению к своему значению. Однако при этом на вход 14 управления устройства подается единичный потенциал, который совместно с сигналом с инверсного выхода счетного триггера 21 разрешает прохождение тактового сигнала через второй элемент И 23 и элемент ИЛИ 24 в конце первого полутакта. Так как в это время коммутатор 5 сигналом с управляющего выхода 19 блока 7 управления переведен в режим коммутации сигнала с второй группы входов, на которую поступает результат, хранящийся в выходном регистре 6, но со сдвигом на один разряд вправо, то в выходной регистр 6 переписывается его же предыдущее значение, сдвинутое вправо на один разряд, т.е. поделенное на два. Таким образом, производится выравнивание разрядной сетки суммы произведений по отношению к поступающему на сложение с ней нового произведения. Если место положения старшего значащего разряда в последовательно поступающих коэффициентах остается неизменным, то на вход 14 управления устройства подается нулевой потенциал, который запрещает прохождение тактового сигнала через второй элемент И 23 в первом полутакте вычисления, поэтому информация в выходном регистре 6 остается неизменной. В конце цикла вычисления в выходном регистре 6 формируется искомая сумма произведений.

Учитывая, что, в частности, в цифровой фильтрации практически всегда выполняется условие различия местоположения старшего значащего разряда с рядом стоящих по абсолютной величине коэффициентах не более чем на один разряд, то использование изобретения практически исключает ошибку накопления в сумме произведения. Быстродействие устройства остается прежним, так как время распространения сигнала через умножитель 3 всегда в несколько раз больше, чем время распространения через цепь сумматор 4 - коммутатор 5 - регистр 6.

В случае, если результат вычисления необходим С -одинарной или двойной точностью, то при сдвиге информации в выходном регистре 6 младший бит слова данных отбрасывается.

Формула изобретения 1. Устройство для вычисления сумм произведений, содержащее умножитель, сумматор, блок управления, выходной регистр и регистры множимого и множителя, информационные входы которых подключены соответственно к шине данных и шине коэффициентов устройства, а тактовые входы подключены к входам

0

5

0

синхронизации соответственно множимого и множителя устройства, выходы регистров множимого и множителя подключены к входам умножителя, выход которого подключен к первому входу сумматора, второй вход которого соединен с выходом выходного регистра, который является выходом устройства, а вход установки выходного регистра подключен к входу установки устройства, о т- личающееся тем, что, с целью сокращения погрешности вычисления при сохранении разрядности сомножителей, в него введен коммутатор, разрядные выходы коммутатора соединены с соответствующими, разрядными входами выходного регистра, разрядные выходы сумматора подключены к разрядным входам первой группы коммутатора, К-е разрядные выходы выходного регистра, кроме младшего М-го (M A+D+P, где А разрядность множимого, D - разрядность множителя, Р -количество расширяющих

5 со стороны старшего разрядов, ) , подключены к (К-1)-м разрядным входам второй группы коммутатора, первый старший разрядный выход выходного регистра подключен к первому разрядному входу второй группы коммутатора, тактовый, управляющий и установочный входы устройства подключены соответственно к тактовому, управляющему и установочному входам блока управления, управляющий выход блока управления соединен с адресным входом коммутатора, а тактовый выход блока управления подключен к тактовому входу выходного регистра.

0

5

0

0

5

| Устройство для вычисления сумм произведений | 1980 |

|

SU905814A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Электронная промышленность, 1986, вып | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для охлаждения водою паров жидкостей, кипящих выше воды, в применении к разделению смесей жидкостей при перегонке с дефлегматором | 1915 |

|

SU59A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-03-23—Публикация

1987-10-05—Подача