СП

ч

СП

со

СП

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адресации блоков памяти | 1988 |

|

SU1575189A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1661766A1 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Устройство для адресации блоков памяти | 1986 |

|

SU1388877A1 |

| Устройство для имитации отказов и сбоев ЭВМ | 1987 |

|

SU1564628A1 |

| Устройство для адресации | 1989 |

|

SU1686449A2 |

| Устройство для контроля хода программы и перезапуска ЭВМ | 1987 |

|

SU1501066A2 |

| Устройство отсчета времени в цвм | 1977 |

|

SU691828A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Устройство для обмена данными между оперативной памятью и внешними устройствами | 1985 |

|

SU1295404A1 |

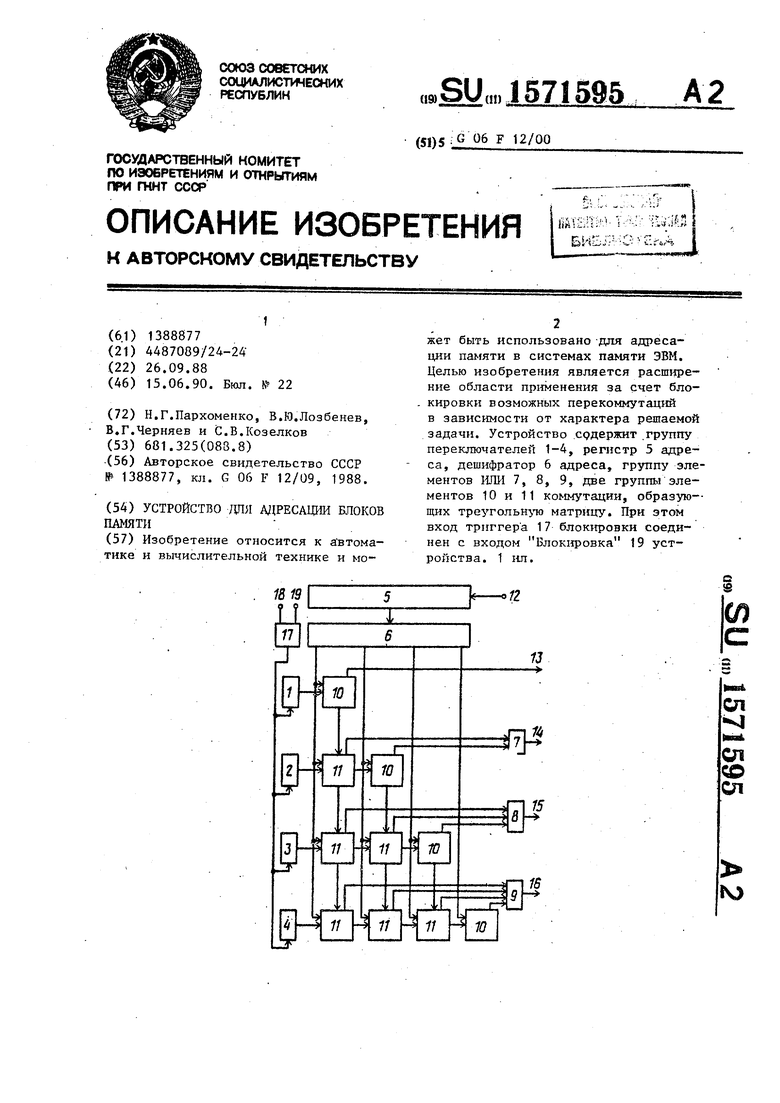

Изобретение относится к автоматике и вычислительной технике и может быть использовано для адресации памяти в системах памяти ЭВМ. Целью изобретения является расширение области применения за счет блокировки возможных перекоммутаций в зависимости от характера решаемой задачи. Устройство содержит группу переключателей 1 - 4, регистр 5 адреса, дешифратор 6 адреса, группу элементов ИЛИ 7, 8, 9, две группы элементов 10 и 11 коммутации, образующих треугольную матрицу. При этом вход триггера 17 блокировки соединен с входом "Блокировка" 19 устройства. 1 ил.

N

Изобретение относится к автоматике и вычислительной технике и мо- кет быть использовано для адресации блоков памяти в системе памяти ЭВМ и является усовершенствованием основного изобретения по авт.св. 1388877.

Цель изобретения - расширение области применения устройства за счет блокировки возможных переком - мутаций в зависимости от характера решаемой процессором задачи.

На чертеже представлена функциональная схема устройства (для слу- чая, когда устройство содержит четыре блока памяти).

Устройство для адресации блоков памяти содержит группу переключателей 1-4, регистр 5 адреса, дешифратор 6 адреса, группу элементов ИЛИ 7-9, две группы элементов 10 и 11 коммутации, образующих треугольную матрицу размером 4x4, адресный вход 12 устройства, выходы 13-16 устройства, триггер 17 блокировки, вход 18 Снятие блокировки и вход 19 Блокировка устройства.

Устройство работает следующим образом.

На сеансе распределения памяти и в режиме внешних обращений при сигнале низкого уровня (НУ) на выходе триггера 17 работа устройства не отличается от работы прототипа,, В случае программной или аппаратной выработки внешнего по отношению к данному устройству сигнала о переходе объекта управления в аварийный режим требующий оперативного вывода объекта из него, такой сигнал поступает на вход 19 Блокировка и устанавливает на выходе триггера 17 блокировк сигнал высокого уровня. Этот сигнал высокого уровня (ВУ) с выхода триггера 17 блокирует возможные изменения в состояниях переключателей группы 1-4, тем самым устраняя потери времени, которые пришлось бы затратить на обработку прерывания, т.е. на установление нового соответствия между логическими и физическими адресами вследствие произошедшей перекоммутации элементов 10-11.

Таким образом, в режиме блокировки устройство игнорирует любые изменения в состояниях переключателей 1-4 для уменьшения времени обращения к высокоприоритетным (в данной ситу571595

ации)

10

блокам памяти. При отказе одного из высокоприоритетных (в данной ситуации) блоков, если такой отказ произошел уже после начала режима, блокировки,процессор программно классифицирует ситуацию как катастрофический отказ субсистемы памяти, о чем извещает центральный процессор. Вход в режим блокировки и выход из него последовательно осуществляется следующим образом.

режима блокировки

НУ НУ ВУ Сигнал блокировки снят, но режим не отменен. Происходит проверка факта выхода объекта из аварийной ситуации

ВУ НУ НУ Отмена режима

блокировки. Начало сеанса распределения памяти вследствие изменения в состояниях переключателей

НУ НУ НУ Обычный режим

5

0

5

Формула изобретения

Устройство для адресации блоков памяти по авт.св. № 1388877, отличающееся тем, что, с целью расширения области применения устройства за счет блокировки возможных перекоммутаций в зависимости от характера решаемой задачи, в него введен триггер блокировки, выход которого соединен с входами блокировки всех переключателей группы, вход сброса триггера блокировки соединен с входом Снятие блокировки устройства, а вход установки триггера блокировки соединен со входом Блокировка

- устройства.

| Устройство для адресации блоков памяти | 1986 |

|

SU1388877A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-06-15—Публикация

1988-09-26—Подача