1

Изобретение относится к вычис- ли те.пьной технике и может быть использовано в многомашинных и многопроцессорных вычислительных системах , .

Цель изобретения - повышение скорости обмена информацией устройства.

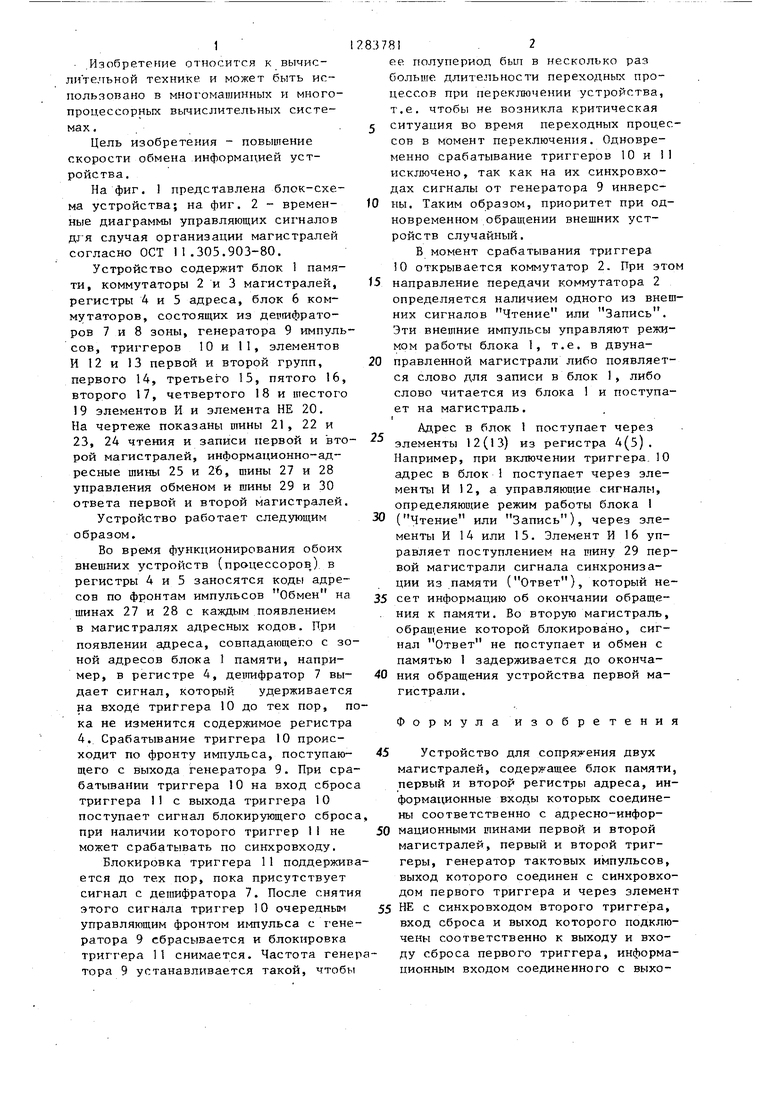

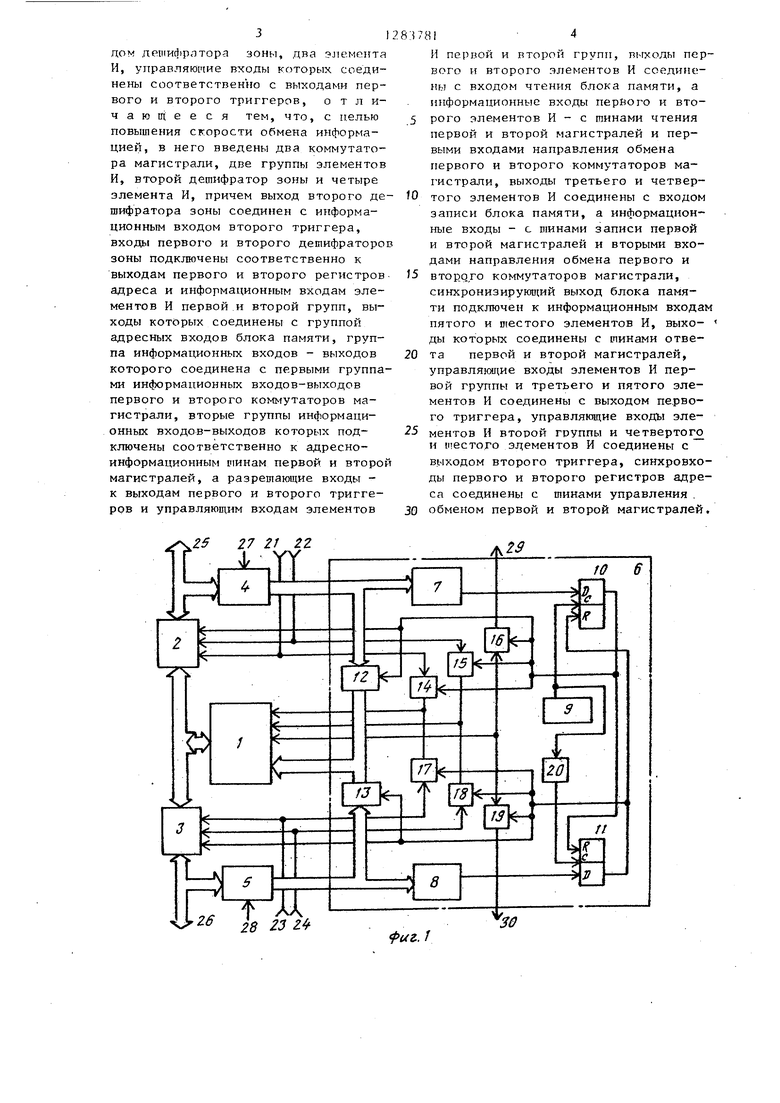

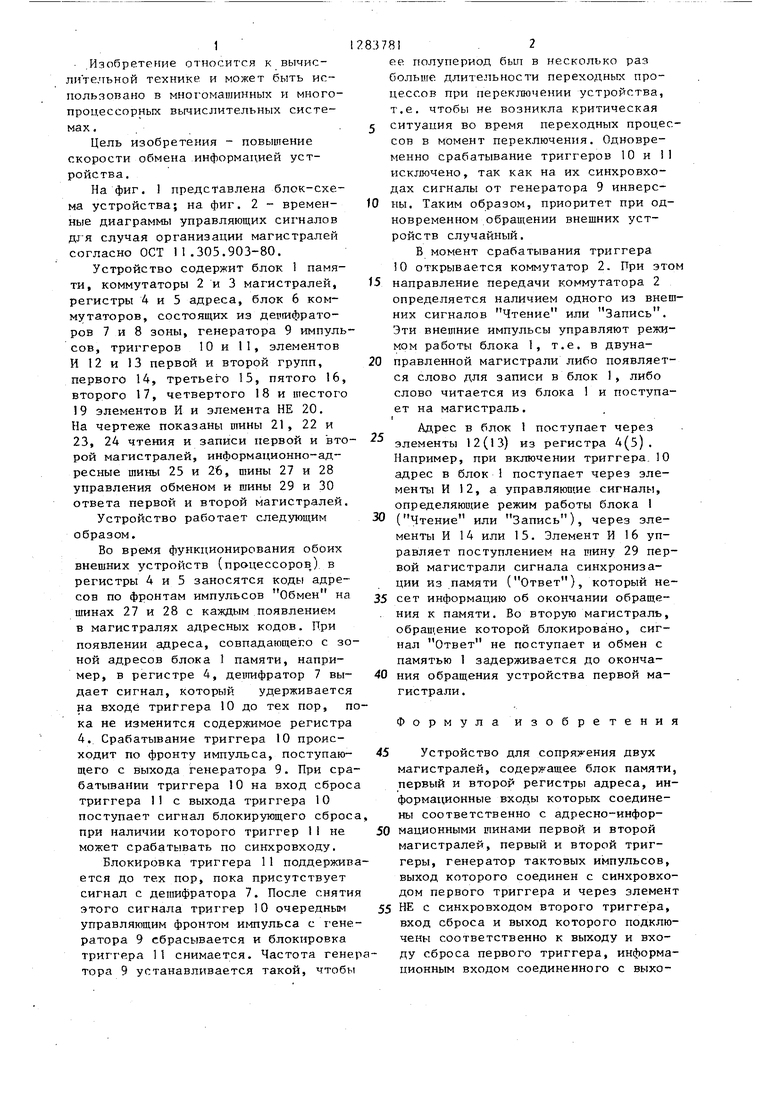

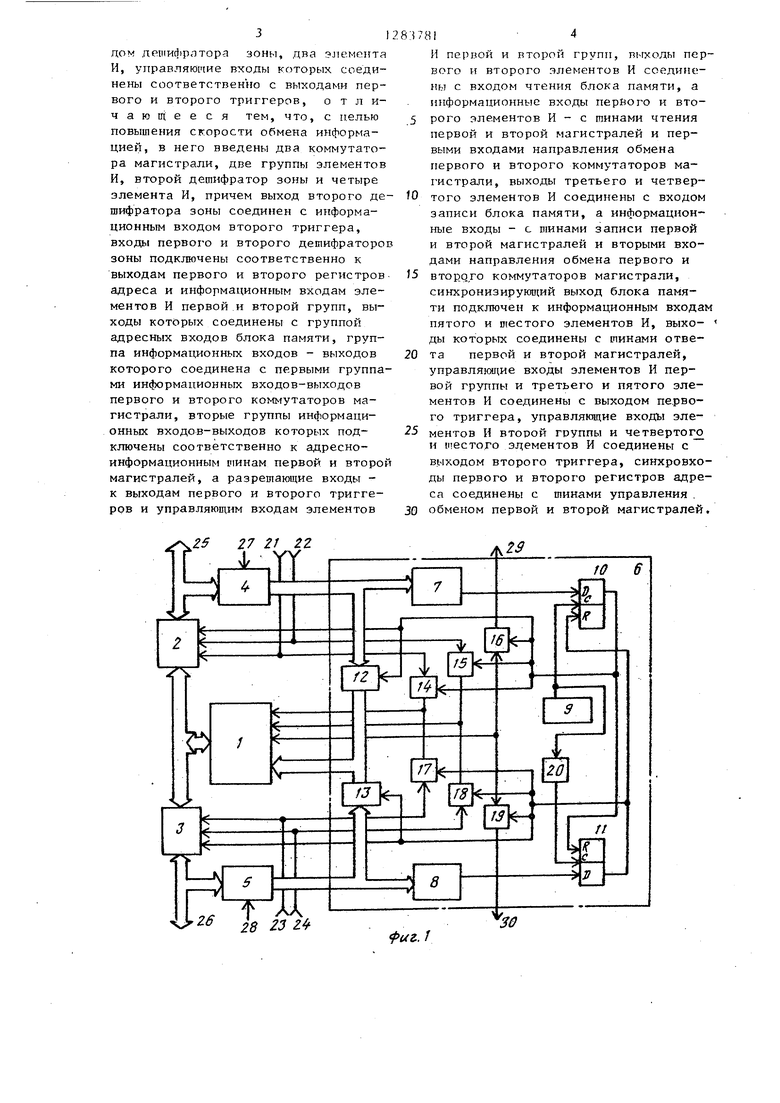

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - временные диаграммы управляющих сигналов дгя случая организации магистралей согласно ОСТ 11.305.903-80.

Устройство содержит блок 1 памяти, коммутаторы 2 и 3 магистралей, регистры 4 и 5 адреса, блок 6 коммутаторов, состоящих из дерифрато- ров 7 и 8 зоны, генератора 9 импульсов, триггеров 10 и 11, элементов И 12 и 13 первой и второй групп, первого 14, третьего 15, пятого 16 второго 17, четвертого 18 и шестого 19 элементов И и элемента НЕ 20. На чертеже показаны шины 21, 22 и 23, 24 чтения и записи первой и втрой магистралей, информационно-адресные шины 25 и 26, шины 27 и 28 управления обменом и шины 29 и 30 ответа первой и второй магистралей

Устройство работает следующим образом.

Во время функционирования обоих внешних устройств (процессоров в регистры 4 и 5 заносятся коды адресов по фронтам импульсов Обмен н

шинах 27 и 28 с каждым появлением в магистралях адресных кодов. При появлении адреса, совпадающего с зоной адресов блока 1 памяти, например, в регистре 4, деигафратор 7 выдает сигнал, который удерживается на входе триггера 10 до тех пор, пока не изменится содержимое регистра 4, Срабатывание триггера 10 происходит по фронту импульса, поступающего с выхода генератора 9. При срабатывании триггера 10 на вход сброса триггера 11 с выхода триггера 10 поступает сигнал блокирующего сброса при наличии которого триггер 11 не может срабатывать по синхровходу.

Блокировка триггера 11 поддерживается до тех пор, пока присутствует сигнал с дешифратора 7. После снятия этого сигнала триггер 10 очередным управляющим фронтом импульса с генератора 9 сбрасывается и блокировка Триггера 11 снимается. Частота генертора 9 устанавливается такой, чтобы

83781 . 2

ее полупериод бьш в несколько раз больнге длительности переходных процессов при переключении устройства, т.е. чтобы не возникла критическая

5 ситуация во время переходных процессов в момент переключения. Одновременно срабатывание триггеров 10 и ii исктючено, так как на их синхровхо- дах сигналы от генератора 9 инверс10 ны. Таким образом, приоритет при одновременном обращении внешних устройств случайный.

В момент срабатывания триггера 10 открывается коммутатор 2. При этом

15 направление передачи коммутатора 2 определяется наличием одного из внешних сигналов Чтение или Запись. Эти внешние импульсы управляют режимом работы блока 1, т.е. в двуна20 правленной магистрали либо появляется слово для записи в блок 1, либо слово читается из блока 1 и поступает на магистраль.

t

Адрес в блок 1 поступает через элементы 12(13) из регистра 4(5). Например, при включении триггера.10 адрес в блок 1 поступает через элементы И 12, а управляющие сигналы, определяющие режим работы блока 1

(Чтение или Запись), через элементы И 14 или 15. Элемент И 16 управляет поступлением на шину 29 первой магистрали сигнала синхронизации из памяти (Ответ), который не35 сет информацию об окончании обращения к памяти. Во вторую магистраль, обраш.ение которой блокирова но, сигнал Ответ не поступает и обмен с памятью 1 задерживается до оконча40 ния обращения устройства первой магистрали.

25

Формула изобретения

45 Устройство для сопряжения двух магистралей, содержащее блок памяти, первый и второй регистры адреса, информационные входы которых соединены соответственно с адресно-инфор50 мационными шинами первой и второй магистралей, первый и второй триггеры, генератор тактовых импульсов, выход которого соединен с синхровхо- дом первого триггера и через элемент

55 НЕ с синхровходом второго триггера, вход сброса и выход которого подключены соответственно к выходу и входу сброса первого триггера, информационным входом соединенного с выходом дешифрлтора зоны, два элемента И, управляютие входы которых соединены соответственно с выходами первого и второго триггеров, отличающееся тем, что, с целью повышения скорости обмена информацией, в него введены два коммутатора магистрали, две группы элементов И, второй дешифратор зоны и четыре элемента И, причем выход второго дешифратора зоны соединен с информационным входом второго триггера, входы первого и второго дешифраторо зоны подключены соответственно к выходам первого и второго регистров адреса и информационным входам элементов И первой и второй групп, выходы которых соединены с группой адресных входов блока памяти, группа информационных: входов - выходов которого соединена с первыми группами информапионных входов-выходов первого и второго KOMNfyTaTopOB магистрали, вторые группы информационных входов-выходов которых подключены соответственно к адресно- информационным минам первой и второй магистралей, а разрепшющие входы - к выходам первого и второго триггеров и управляющим входам элементов

.5

to

8378 4

И первой и второй групп, выходы первого и второго элементов И соединены с входом чтения блока памяти, а информационные входы первого и второго элементов И - с тинами чтения первой и второй магистралей и первыми входами направления обмена первого и второго коммутаторов магистрали, выходы третьего и четвертого элементов И соединены с входом записи блока памяти, а информационные входы - с шинами записи первой и второй магистралей и вторыми входами направления обмена первого и второго коьтмутаторов магистрали, cинxpoнизиpyюD ий выход блока памяти подключен к информационным входам пятого и DiecToro элементов И, выхо- ды которых соединены с шинами ответа первой и второй магистралей, управляняцие входы элементов И первой группы и третьего и пятого элементов И соединены с выходом первого триггера, управляющие входы эле- S ментов И ВТОРОЙ группы и четвертог и шестого элементов И соединены с выходом второго триггера, синхровхо- ды первого и второго регистров адреса соединены с тинами управления 30 обменом первой и второй магистралей.

15

20

fPU2.2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1545225A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1522224A1 |

| Устройство для сопряжения магистралей | 1990 |

|

SU1737460A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1619286A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1619285A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1539788A2 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1550523A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1575193A2 |

| Устройство для сопряжения двух магистралей | 1990 |

|

SU1778760A1 |

| Устройство для сопряжения двух процессоров с общей памятью | 1988 |

|

SU1569840A1 |

Изобретение относится к области вычислительной техники и может быть использовано в многомашинных и многопроцессорных вычислительных системах. Целью изобретения является повьппение скорости обмена информацией. Цель достигается тем, что в устройство, содержащее два,триггера, генератор импульсов, элемент НЕ, дешифратор зоны, блок памяти, два элемента И и два регистра адреса, введены два коммутатора магистрали, две группы элементов И, второй дешифратор зоны и четыре элемента И. 2 ил. Ш

| Патент США № 4156923, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обмена данными | 1981 |

|

SU1012235A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-15—Публикация

1985-06-27—Подача