Изобретение относится к устройствам вычислительной техники и может быть использовано при создании многомашинных и многопроцессорных систем.

Известно устройство для сопряжения, содержащее генератор тактовых импульсов, управляющий дешифратор, дешифратор ввода/вывода, блок памяти, линейный блок ввода/вывода блок микропрограммного управления, блэк прерываний, блок связи с магистралью, блок регистров и блок связи с линиями.позволяет сопрягат э две магистрали, но облада т большими аппаратными затратами и низким быстродействием за счет поочередной сиязи с магистралями.

Известно также устройство для сопря- жения содержащее блок оперативной памяти, мультиплексор адреса, первый шинный формирователь, триггер, второй шинный формирователь, мультиплексор управления оперативной памятью и элемент НЕ позволяет сопрягать две магистрали и имеет широкую область применения.

Недостатком устройства является низкое быстродействие за счет поочередного обмена информацией процессорами

Наиболее близким по технической сущности к заявляемому устройству является выбранное в качестве прототипа устройство для сопряжения двух магистралей.содержа- щее блок памяти, первый и второй регистры

VI

VI оо vi о ю

адреса, первый и второй триггеры, генератор тактовых импульсов, элемент НЕ, два дешифратора зоны, шесть элементов И, два коммутатора магистрали и две группы элементов И, причем информационные входы регистров адреса соединены соответственно с адресно-информационными шинами первой и второй магистрали, выход генератора тактовых импульсов соединен с синх- ровходом первого триггера и через элемент НЕ с синхровходом второго триггера, вход сброса и выход которого подключены соответственно к выходу и входу сброса первого триггера, информационным входом соединенного с выходом первого дешифратора зоны, управляющие входы первого и второго элементов И соединены соответственно с выходами первого и второго триггеров, выход второго дешифратора зоны соединен с информационным входом второго триггера, входы первого и второго дешифраторов зоны подключены соответственно к выходам первого и второго регистров адреса и информационным входам элементов И первой и второй групп, выходы которых соединены с группой адресных входов блока памяти, группа информационных входов- выходов которого соединена с первыми группами информационных входов-выходов первого и второго коммутаторов магистрали, вторые группы информационных входов-выходов которых подключены соответственно к адресно-информационным шинам первой и второй магистралей, а разрешающие входы - к выходам первого и второго триггеров и управляющим входам элементов И первой и второй групп, выходы первого и второго элементов И соединены с входом чтения блока памяти, а информационные входы первого и второго элементов И - с шинами чтения первой и второй магистралей и первыми входами направления обмена первого и второго коммутаторов магистрали, выходы третьего и четвертого элементов И соединены с входами записи блока памяти, а информационные входы - с шинами записи первой и второй магистралей и вторыми входами направления обмена первого и второго коммутаторов магистрали, синхронизирующий выход блока памяти подключен к информационным входам пятого и шестого элементов И, выходы которых соединены с шинами ответа первой и второй магистралей, управляющие входы элементов И первой группы и третьего и пятого элементов И соединены с выходом первого триггера, управляющие входы элементов И второй группы и четвертого и шестого элементов И соединены с выходом второго триггера, синхровходы первого и

второго регистров адреса соединены с шинами управления обменом первой и второй магистралей.позчоляет сопрягать магистрали.

Недостатком прототипа является недостаточное быстродействие вследствие потерь времени при поочередном выполнении операций записи и чтения информации в/из блока памяти в магистрали и потерь време0 ни на многократно повторяющиеся операции занесения адреса ячейки памяти при обмене массивами информации между магистралями.

Целью изобретения является повы5 шение быстродействия устройства за счат совмещения во времени операций записи/чтения информации в/из блока памяти в обе магистрали и исключения множества операций занесения адреса

0 ячейки памяти при обмене массивами информации между магистралями.

Поставленная цель достигается тем, что в известное устройство для сопряжения двух магистралей, содержащее блок памя5 ти, генератор тактовых импульсов, первый и второй триггеры, элемент НЕ, шесть элементов И, два коммутатора магистрали, причем выход генератора тактовых импульсов соединен с синхровходом первого триггера

0 и через элемент НЕ с синхровходом второго триггера, группа информационных входов- выходов блока памяти соединена с группой информационных входов-выходов первого коммутатора магистрали, информационные

5 входы первого и второго элементов И соединены с первыми входами направления обмена второго и первого коммутаторов магистрали, управляющие входы третьего и пятого элементов И соединены с выходом

0 первого триггера, управляющие входы четвертого и шестого элементов И соединены с выходом второго триггера, введены шесть приемников, две группы приемников, четыре элемента НЕ, два счетчика адреса, два

5 элемента сравнения зоны, четыре триггера, два коммутатора адреса, два элемента И пять элементов ИЛИ, два элемента задержки четыре элемента И-НЕ и блок памяти разделен на две зоны адресов - первую

0 (младшую) и вторую (старшую), причем входы первого, второго и третьего приемника соединены соответственно с линиями вывода, синхронизации и ввода первой магистрали, группа входов первой группы

5 приемников соединена с линиями адреса первой магистрали, группа линий данных которой соединена с группой входов и группой выходов первого и второго коммутатора магистрали, соответственно, входы четвертого, пятого и шестого приемника соединены, соответственно, с линиями ввода, синхронизации и вывода второй магистрали, группа входов второй группы приемников соединена с линиями адреса второй магистрали, группа линий данных которой соединена с группой выходов и группой входов первого и второго коммутатора магистрали, соответственно, выход первого приемника соединен со вторым входом третьего элемента И, третий вход которого соединен с инверсным выходом пятого триггера, третий вход седьмого элемента И соединен с выходом третьего триггера, информационный вход которого соединен с младшим разрядом группы выходов группы приемников, соединенных с группой входов первого счетчика адреса, группа выходов которого соединена с первыми группами входов первого и второго коммутатора адреса и с первой группой входов элемента сравнения первой зоны, вторая группа входов которого является входами установки адреса первой зоны, выход элемента сравнения первой зоны соединен с информационным входом первого триггера, выход третьего элемента И соединен со входом первого элемента НЕ, с первым входом третьего элемента ИЛИ, с первым входом пятого элемента ИЛИ, со вторым входом направления обмена первого коммутатора магистрали, с первым входом разрешения передачи первого коммутатора адреса, группа выходов которого соединена с группой входов адреса первой зоны блока памяти, вход выборки которой соединен с выходом первого элемента И-НЕ, первый вход которого соединен с выходом пятого элемента ИЛИ, второй вход которого соединен с первым входом второго элемента И и со вторым входом разрешения передачи первого коммутатора адреса, вторая группа входов которого соединена со второй группой входов второго коммутатора адреса, с группой выходов второго счетчика адреса и с первой группой входов элемента сравнения второй зоны, вторая группа входов которого является входами установки адреса второй зоны, выход элемента сравнения второй зоны соединен с информационным входом второго триггера, выход шестого приемника соединен со вторым входом четвертого элемента И, третий вход которого соединен с инверсным выходом шестого триггера, третий вход восьмого элемента И соединен с выходом четвертого триггера, информационный вход которого соединен с младшим разрядом группы выходов группы приемни- ков соединенных с группой входов второго счетчика адреса, вход синхронизации которого соединен со входом синхронизации

четвертого триггера и с выходом пятого приемника, выход четвертого приемника соединен со вторым входом шестого элемента И, первый вход которого является управляющим и соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с первым управляющим входом пятого элемента И, второй вход которого соединен с выходом третьего приемника, выход пято0 го элемента И соединен со вторым входом третьего элемента ИЛИ, со входом второго элемента НЕ и с первым входом первого элемента И, выход третьего элемента ИЛИ соедиЯен со входом первого элемента за5 держки и с первым входом третьего элемента И-НЕ, второй вход которого соединен с выходом первого элемента задержки, выход третьего элемента И-НЕ соединен с линией ответа первой магистрали, выход первого

0 элемента НЕ соединен с входом автоувеличения счетчика адреса и с первым входом седьмого элемента И, выход которого соединен с входом синхронизации пятого триггера, .прямой выход и информационный

5 вход которого соединены с третьим входом шестого элемента И, выход которого соединен с первым входом первого элемента ИЛИ, с входом третьего элемента НЕ и с первым входом второго элемента И, выход

0 которого соединен со входом записи/чтения первой зоны блока памяти, вход записи-чтения второй зоны которого соединен с выходом первого элемента И, второй вход которого соединен со вторым входом перво5 го элемента И-НЕ, со вторым входом второго элемента И, с выходом второго элемента ИЛИ и с первым входом второго элемента И-ИЕ, выход которого соединен с входом выборки второй зоны блока памяти, группа

0 информационных входов-выходов которой соединена с группой входов/выходов второго коммутатора магистрали, первый вход направления обмена которого соединен с первым входом четвертого элемента ИЛИ, с

5 первым входом разрешения передачи второго коммутатора адреса, с выходом четвертого элемента И, с входом четвертого элемента НЕ и со вторым входом первого элемента ИЛИ, выход которого соединен с

0 входом второго элемента задержки и .с первым входом четвертого элемента И-НЕ, второй вход которого соединен с выходом второго элемента задержки, выход четвертого элемента И-НЕ соединен с линией от5 вета второй магистрали, выход четвертого элемента НЕ соединен со вторым входом восьмого элемента И и со входом автоувеличения второго счетчика адреса, вход автоуменьшения которого соединен с выходом третьего элемента НЕ и со вторым входом

седьмого элемента И, выход восьмого элемента И соединен с входом синхронизации шестого триггера, прямой выход и информационный вход которого соединены с третьим входом пятого элемента И, первый вход восьмого элемента И соединен с выходом второго элемента НЕ и со входом автоуменьшения первого счетчика адреса, вход синхронизации которого соединен со входом синхронизации третьего триггера и с выходом второго приемника, группа адресных входов второй зоны блока памяти соединена с группой выходов второго коммутатора адреса, второй вход разрешения передачи которого соединен с первым входом первого элемента И и со вторым входом четвертого элемента ИЛИ, выход которого соединен со вторым входом второго элемента И-НЕ.

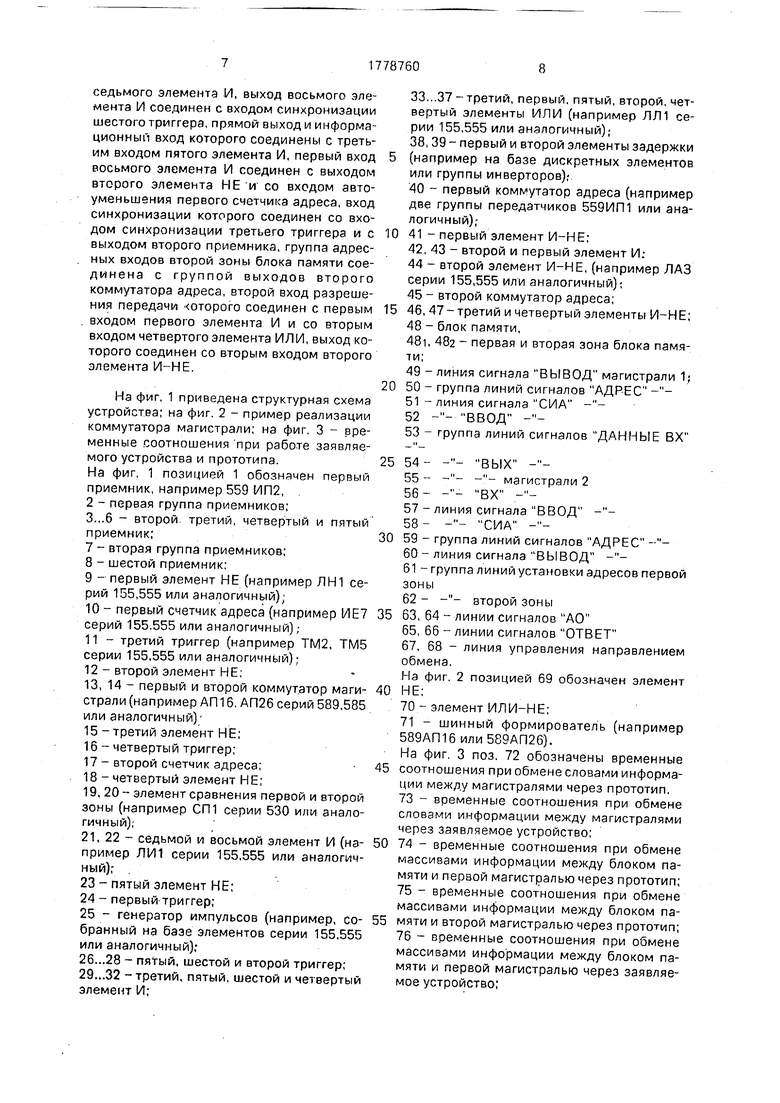

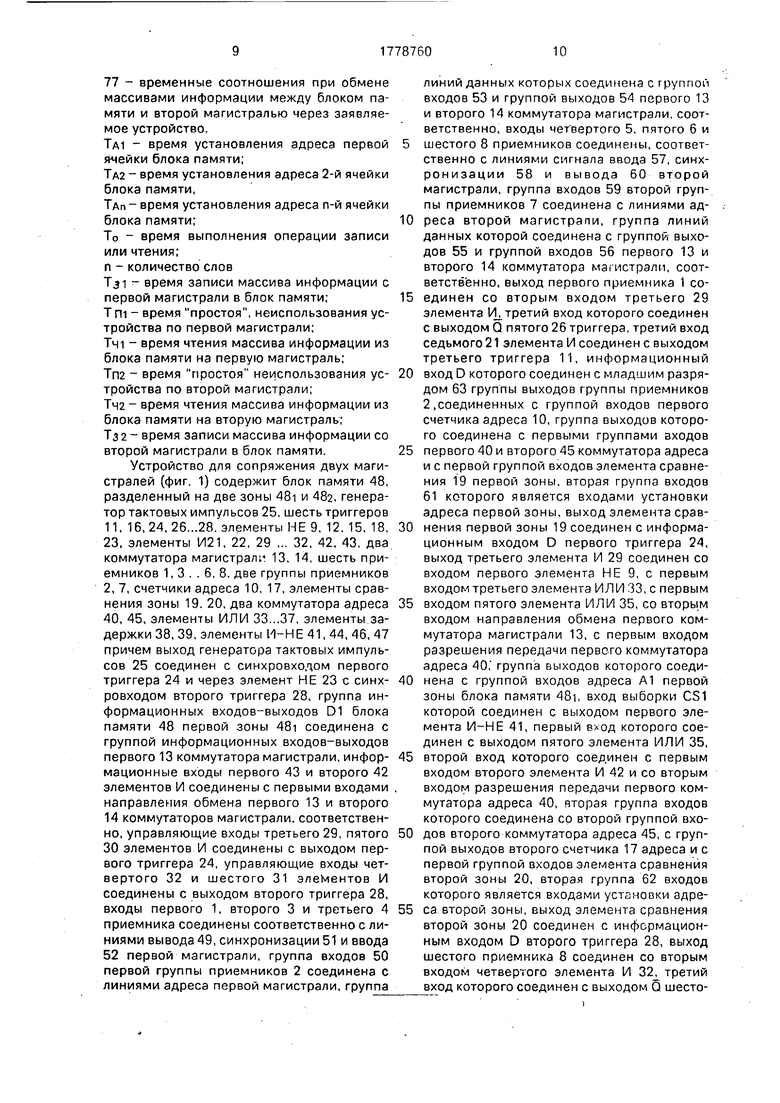

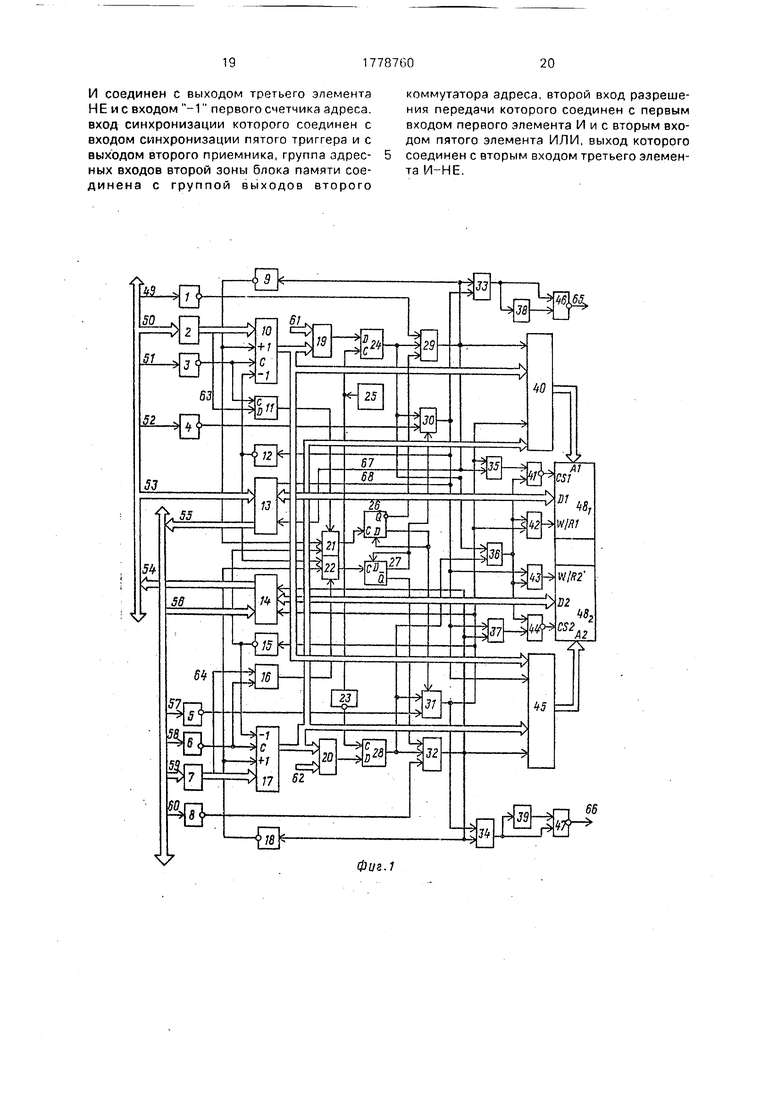

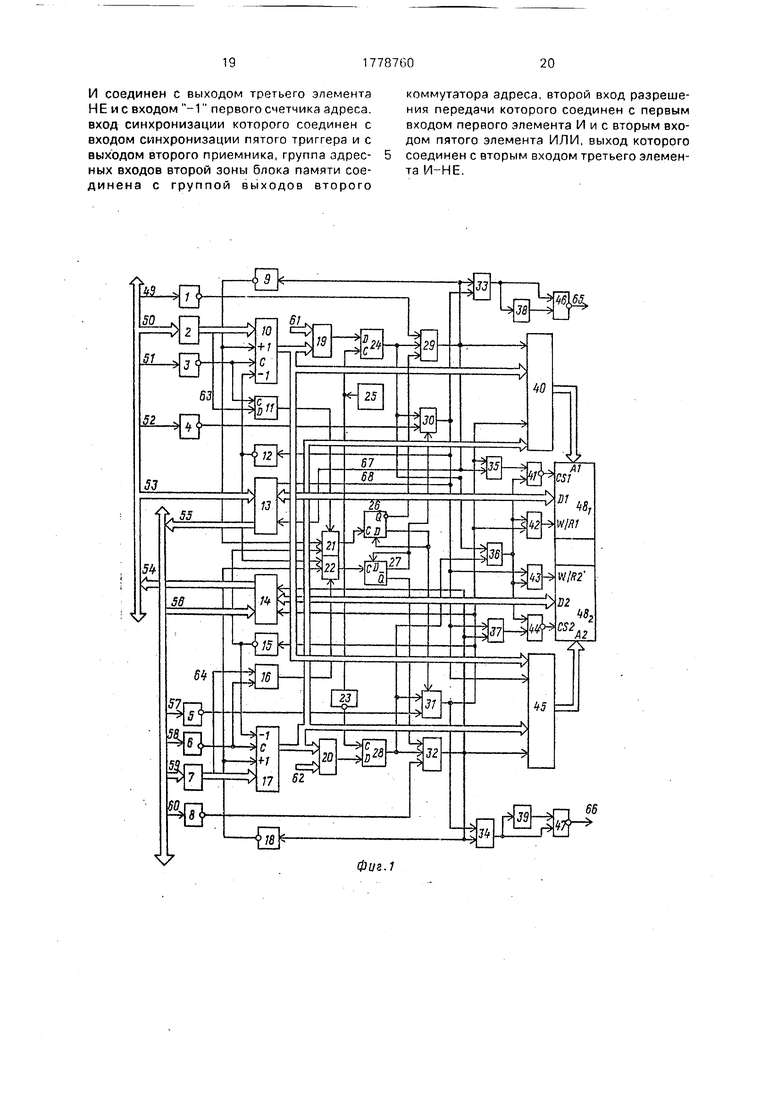

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - пример реализации коммутатора магистрали; на фиг. 3 - временные соотношения при работе заявляемого устройства и прототипа. На фиг, 1 позицией 1 обозначен первый приемник, например 559 ИП2, 2 - первая группа приемников; 3...6 - второй третий, четвертый и пятый приемник;

7- вторая группа приемников;

8- шестой приемник;

9- первый элемент НЕ (например ЛН1 серий 155,555 или аналогичный);

10- первый счетчик адреса (например ИЕ7 серий 155.555 или аналогичный);

11- третий триггер (например ТМ2, ТМ5 серии 155,555 или аналогичный);

12- второй элемент НЕ;

13, 14 - первый и второй коммутатор магистрали (например АП16, АП26 серий 589,585 или аналогичный)

15- третий элемент НЕ;

16- четвертый триггер;

17- второй счетчик адреса;

18- четвертый элемент НЕ;

19, 20 - элемент сравнения первой и второй зоны (например СП1 серии 530 или аналогичный);

21, 22 - седьмой и восьмой элемент И (например ЛИ1 серии 155,555 или аналогичный);

23- пятый элемент НЕ;

24- первый триггер;

25- генератор импульсов (например, собранный на базе элементов серии 155,555 или аналогичный);

26...28 - пятый, шестой и второй триггер; 29...32 -третий, пятый, шестой и четвертый элемент И;

33...37-третий, первый, пятый, второй, четвертый элементы ИЛИ (например ЛЛ1 серии 155,555 или аналогичный); 38,39 - первый и второй элементы задержки

(например на базе дискретных элементов или группы инверторов); 40 - первый коммутатор адреса (например две группы передатчиков 559ИП1 или аналогичный);

41 - первый элемент И-НЕ;

42, 43 - второй и первый элемент И;

44- второй элемент И-НЕ, (например ЛАЗ серии 155,555 или аналогичный):

45- второй коммутатор адреса;

46, 47 - третий и четвертый элементы И-НЕ;

48- блок памяти,

48т, 482 - первая и вторая зона блока памяти;

49- линия сигнала ВЫВОД магистрали 1; 50 - группа линий сигналов АДРЕС - 51- линия сигнала СИА - 52- - ВВОД - 53- группа линий сигналов ДАННЫЕ ВХ

54- ВЫХ - магистрали 2

56- ВХ - линия сигнала ВВОД СИА 59 - группа линий сигналов АДРЕС - 60- линия сигнала ВЫВОД - 61- группа линийустановки адресов первой зоны

62- второй зоны

63, 64 - линии сигналов АО 65, 66 - линии сигналов ОТВЕТ 67, 68 - линия управления направлением обмена. На фиг. 2 позицией 69 обозначен элемент

НЕ;

70-элемент ИЛИ-НЕ;

71 - шинный формирователь (например

589АП16или589АП26).

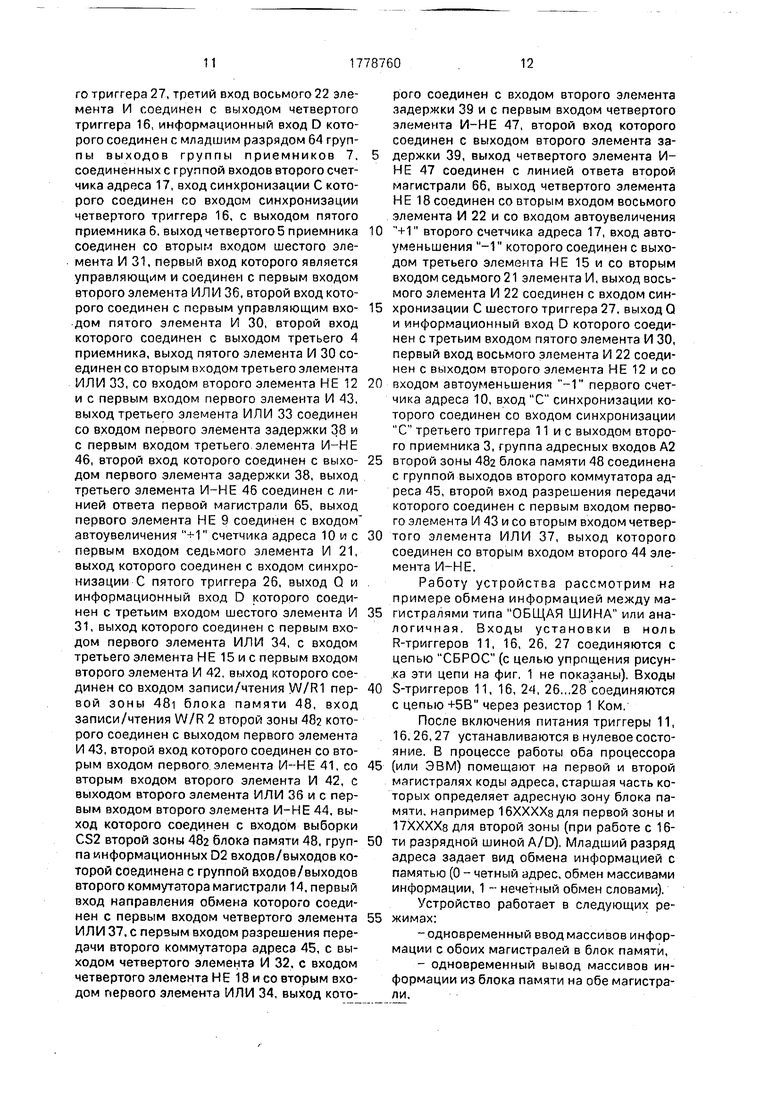

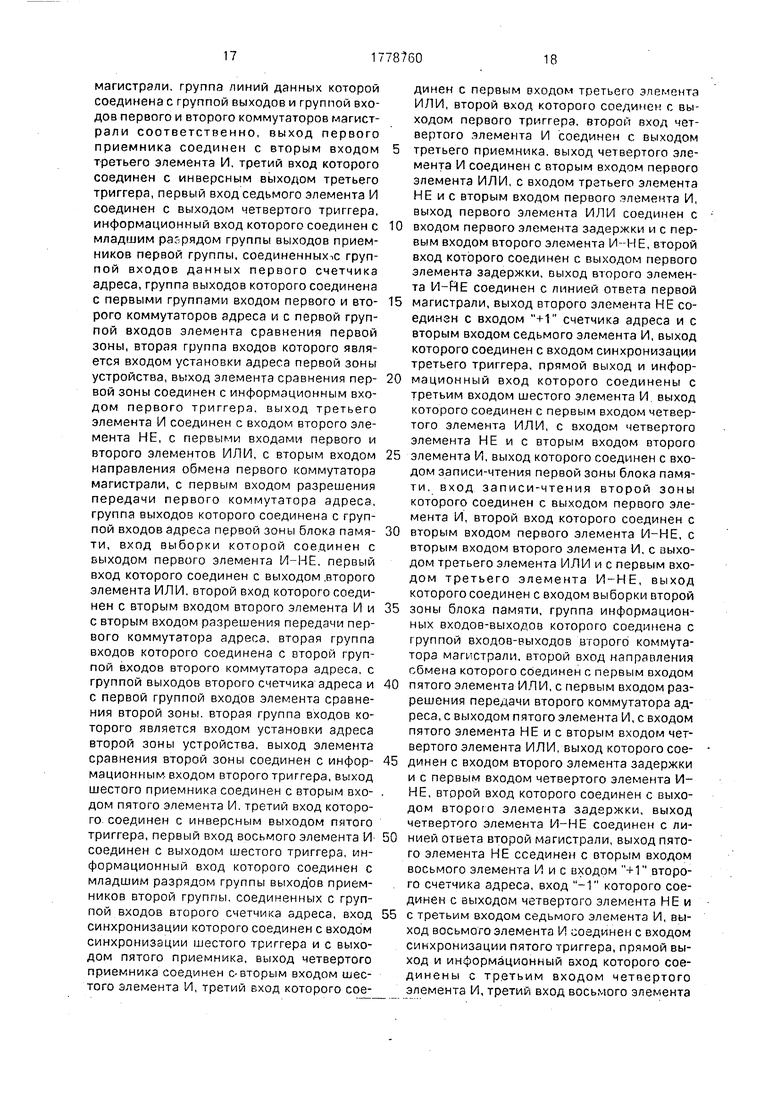

На фиг. 3 поз. 72 обозначены временные

соотношения при обмене словами информации между магистралями через прототип. 73 - временные соотношения при обмене словами информации между магистралями через заявляемое устройство;

74 - временные соотношения при обмене массивами информации между блоком памяти и первой магистралью через прототип;

75- временные соотношения при обмене массивами информации между блоком памяти и второй магистралью через прототип;

76- временные соотношения при обмене массивами информации между блоком памяти и первой магистралью через заявляемое устройство;

77 - временные соотношения при обмене массивами информации между блоком памяти и второй магистралью через заявляемое устройство.

TAI - время установления адреса первой ячейки блока памяти;

Тд2 - время установления адреса 2-й ячейки блока памяти,

ТАП - время установления адреса n-й ячейки блока памяти;

То - время выполнения операции записи или чтения; п - количество слов

Тз1 - время записи массива информации с первой магистрали в блок памяти; Тщ - время простоя, неиспользования устройства по первой магистрали; Тч1 - время чтения массива информации из блока памяти на первую магистраль; Тп2 время простоя неиспользования устройства по второй магистрали; Тч2 - время чтения массива информации из блока памяти на вторую магистраль; Тз 2 - время записи массива информации со второй магистрали в блок памяти.

Устройство для сопряжения двух магистралей (фиг. 1) содержит блок памяти 48, разделенный на две зоны 48i и 482, генератор тактовых импульсов 25, шесть триггеров 11, 16, 24, 2Б...28, элементы НЕ 9, 12, 15. 18, 23, элементы 1/121. 22, 29 ... 32, 42, 43, два коммутатора магистрали 13. 14, шесть приемников 1, 3 . . 6, 8, две группы приемников 2, 7, счетчики адреса 10, 17, элементы сравнения зоны 19. 20, два коммутатора адреса 40, 45, элементы ИЛИ 33...37, элементы задержки 38, 39, элементы И-НЕ 41, 44, 46, 47 причем выход генератора тактовых импульсов 25 соединен с синхровходом первого триггера 24 и через элемент НЕ 23 с синхровходом второго триггера 28, группа информационных входов-выходов D1 блока памяти 48 первой зоны 48i соединена с группой информационных входов-выходов первого 13 коммутатора магистрали, информационные входы первого 43 и второго 42 элементов И соединены с первыми входами направления обмена первого 13 и второго 14 коммутаторов магистрали, соответственно, управляющие входы третьего 29, пятого 30 элементов И соединены с выходом первого триггера 24, управляющие входы четвертого 32 и шестого 31 элементов И соединены с выходом второго триггера 28, входы первого 1, второго 3 и третьего 4 приемника соединены соответственное линиями вывода 49, синхронизации 51 и ввода 52 первой магистрали, группа входов 50 первой группы приемников 2 соединена с линиями адреса первой магистрали, группа

линий данных которых соединена с группой входов 53 и группой выходов 54 первого 13 и второго 14 коммутатора магистрали, соответственно, входы четвертого 5. пятого б и

шестого 8 приемников соединены, соответственно с линиями сигнала ввода 57, синхронизации 58 и вывода 60 второй магистрали, группа входов 59 второй группы приемников 7 соединена с линиями ад0 реса второй магистрапи, группа линий данных которой соединена с группой выходов 55 и группой входов 56 первого 13 и второго 14 коммутатора магистрали, соответственно, выход первого приемника 1 со5 единен со вторым входом третьего 29 элемента И третий вход которого соединен с выходом Q пятого 26 триггера, третий вход седьмого 21 элемента И соединен с выходом третьего триггера 11, информационный

0 вход D которого соединен с младшим разрядом 63 группы выходов группы приемников 2 .соединенных с группой входов первого счетчика адреса 10, группа выходов которого соединена с первыми группами входов

5 первого 40 и второго 45 коммутатора адреса и с первой группой входов элемента сравнения 19 первой зоны, вторая группа входов 61 которого является входами установки адреса первой зоны, выход элемента срав0 нения первой зоны 19 соединен с информационным входом D первого триггера 24. выход третьего элемента И 29 соединен со входом первого элемента НЕ 9, с первым входом третьего элемента ИЛ И 33, с первым

5 входом пятого элемента ИЛИ 35, со вторым входом направления обмена первого коммутатора магистрали 13, с первым входом разрешения передачи первого коммутатора адреса 40, группа выходов которого соеди0 нена с группой входов адреса А1 первой зоны блока памяти 48i, вход выборки CS1 которой соединен с выходом первого элемента И-НЕ 41, первый вход которого соединен с выходом пятого элемента ИЛИ 35,

5 второй вход которого соединен с первым входом второго элемента И 42 и со вторым входом разрешения передачи первого коммутатора адреса 40, вторая группа входов которого соединена со второй группой вхо0 дов второго коммутатора адреса 45, с группой выходов второго счетчика 17 адреса и с первой группой входов элемента сравнения второй зоны 20, вторая группа 62 входов которого является входами установки адре5 са второй зоны, выход элемента сравнения второй зоны 20 соединен с информационным входом D второго триггера 28, выход шестого приемника 8 соединен со вторым входом четвертого элемента И 32 третий вход которого соединен с выходом Q шестого триггера 27, третий вход восьмого 22 элемента И соединен с выходом четвертого триггера 16, информационный вход D которого соединен с младшим разрядом 64 груп- пы выходов группы приемников 7, соединенных с группой входов второго счетчика адреса 17, вход синхронизации С которого соединен со входом синхронизации четвертого триггера 16, с выходом пятого приемника 6, выход четвертого 5 приемника соединен со вторым входом шестого элемента И 31, первый вход которого является управляющим и соединен с первым входом второго элемента ИЛИ 36, второй вход которого соединен с первым управляющим входом пятого элемента И 30, второй вход которого соединен с выходом третьего 4 приемника, выход пятого элемента И 30 соединен со вторым входом третьего элемента ИЛИ 33, со входом второго элемента НЕ 12 и с первым входом первого элемента И 43, выход третьего элемента ИЛИ 33 соединен со входом первого элемента задержки 38 и с первым входом третьего элемента И-НЕ 46, второй вход которого соединен с выходом первого элемента задержки 38, выход третьего элемента И-НЕ 46 соединен с линией ответа первой магистрали 65, выход первого элемента НЕ 9 соединен с входом автоувеличения +1 счетчика адреса 10 и с первым входом седьмого элемента И 21, выход которого соединен с входом синхронизации С пятого триггера 26, выход Q и информационный вход D которого соединен с третьим входом шестого элемента И 31, выход которого соединен с первым входом первого элемента ИЛИ 34, с входом третьего элемента НЕ 15 и с первым входом второго элемента И 42, выход которого соединен со входом записи/чтения W/R1 первой зоны 48i блока памяти 48, вход записи/чтения W/R 2 второй зоны 482 которого соединен с выходом первого элемента И 43, второй вход которого соединен со вторым входом первого элемента И-НЕ 41, со вторым входом второго элемента И 42, с выходом второго элемента ИЛИ 36 и с первым входом второго элемента И-НЕ 44, выход которого соединен с входом выборки CS2 второй зоны 482 блока памяти 48, группа информационных D2 входов/выходов которой соединена с группой входов/выходов второго коммутатора магистрали 14, первый вход направления обмена которого соединен с первым входом четвертого элемента ИЛИ 37, с первым входом разрешения передачи второго коммутатора адреса 45, с выходом четвертого элемента И 32. с входом четвертого элемента НЕ 18 и со вторым входом первого элемента ИЛИ 34, выход которого соединен с входом второго элемента задержки 39 и с первым входом четвертого элемента И-НЕ 47, второй вход которого соединен с выходом второго элемента задержки 39, выход четвертого элемента И- НЕ 47 соединен с линией ответа второй магистрали 66, выход четвертого элемента НЕ 18 соединен со вторым входом восьмого элемента И 22 и со входом автоувеличения

0 +1 второго счетчика адреса 17, вход автоуменьшения -1 которого соединен с выходом третьего элемента НЕ 15 и со вторым входом седьмого 21 элемента И, выход восьмого элемента И 22 соединен с входом син5 хронизации С шестого триггера 27, выход Q и информационный вход D которого соединен с третьим входом пятого элемента И 30, первый вход восьмого элемента И 22 соединен с выходом второго элемента НЕ 12 и со

0 входом автоуменьшения -1 первого счетчика адреса 10, вход С синхронизации которого соединен со входом синхронизации С третьего триггера 11 и с выходом второго приемника 3, группа адресных входов А2

5 второй зоны 482 блока памяти 48 соединена с группой выходов второго коммутатора адреса 45, второй вход разрешения передачи которого соединен с первым входом первого элемента И 43 и со вторым входом четвер0 того элемента ИЛИ 37, выход которого соединен со вторым входом второго 44 элемента И-НЕ.

Работу устройства рассмотрим на примере обмена информацией между ма5 гистралями типа ОБЩАЯ ШИНА или аналогичная. Входы установки в ноль R-триггеров 11, 16, 26, 27 соединяются с цепью СБРОС (с целью упрощения рисунка эти цепи на фиг, 1 не показаны). Входы

0 S-триггеров 11, 16, 24, 26...28 соединяются с цепью +5В через резистор 1 Ком.

После включения питания триггеры 11, 16, 26,27 устанавливаются в нулевое состояние. В процессе работы оба процессора

5 (или ЭВМ) помещают на первой и второй магистралях коды адреса, старшая часть которых определяет адресную зону блока памяти, например 16ХХХХздля первой зоны и 17XXXXs для второй зоны (при работе с 160 ти разрядной шиной A/D), Младший разряд

адреса задает вид обмена информацией с

памятью (0 - четный адрес, обмен массивами

информации, 1 - нечетный обмен словами).

Устройство работает в следующих ре5 жимах:

-одновременный ввод массивов информации с обоих магистралей в блок памяти,

- одновременный вывод массивов информации из блока памяти на обе магистрали.

- одновременный ввод/вывод информационных слов в/из блока памяти на обе магистрали.

Одновременный ввод массивов информации с магистралей в блок памяти. В программном режиме ввода (записи) информации ЭВМ, подключенные к магистралям, выполняют по отношению друг к другу стандартную операцию ВЫВОД за два цикла.

При выполнении первого (адресного) цикла ЭВМ выставляют на линиях 50 и 59 адреса (например четные 1110ХХХХХХХХХХ 02 и 1111ХХХХХХХХХХ02). Коды адреса поступают через группы при- емников 2 и 7 на информационные входы счетчиков 10 и 17, Адреса сопровождаются сигналами синхронизации СИА, которые поступают через приемники 3 и 5 на входы синхронизации С счетчиков 10,17соответ- ственно, и производят запись кодов адресов в счетчики Младшие разряды кодов адреса 63, 64 поступают на информационные входы D триггеров 11, 16 и по сигналу СИА их значения устанавливаются на выхо- де этих триггеров, устанавливая выходы элементов И 21, низкое состояние. При этом на выходах Q триггеров 26, 27 будут находиться высокие уровни сигналов, разрешающие работу элементов И 29 и 32 (от действия сигналов сброс на входы R триггеров 26,27). Коды адреса с выходов счетчиков 10, 17 поступают на входы элементов сравнения 19, 20 и при равенстве старших разрядов кодам, установленным на входах 61, 62, на их выходах формируется сигнал высокого уровня, поступающий на входы D триггеров 24, 28, соответственно. Триггеры 24 и 28 перейдут в единичное состояние по приходу тактового импульса на вход С с раз- ницей в полпериода. Частота генератора 25 устанавливается такой, чтобы ее полупериод был в несколько раз больше длительности переходных процессов при переключении элементов устройства. Одно- временное срабатывание триггеров 24, 28 исключено, так как на их синхровходах сигналы от генератора 25 инверсны. Таким образом обеспечивается исключение критических ситуаций во время переходных про- цессов в моменты переключения.

В момент срабатывания триггера на выходе элемента ИЛИ 36 появится высокий уровень сигнала, обеспечивающий формирование управляющих сигналов на входах блока памяти 48. Далее ЭВМ снимают с шин 50, 59 адреса и помещают на шины 53, 56 данные и на линии 49,60 сигналы ВЫВОД. Эти сигналы проходят через приемники 1 и 8 и высоким уровнем поступают на входы

элементов И 29. 32 соответственно. При этом на выходах этих элементов появятся сигналы высокого уровня,разрешающие прохождение адреса через коммутаторы 40, 45 и данных с шин 53, 56 через коммутаторы 13. 14 на входы А1, А2 и D1, D2 блока памяти 48, Одновременно сигналы высокого уровня с выходов элементов 29, 32 поступают через элементы ИЛИ 35, 37, соответственно, на входы элементов И-НЕ 41, 44.формируя на их выходах низкие уровни сигналов выборки CS1 и CS2.

На входах W/R1 и VV/R2 блока памяти в это время находятся низкие уровни сигнала, обеспечивающие запись (ввод) информации в ячейку памяти по адресу, помещенному в счетчик адреса. Высокие уровни сигналов с выходов элементов 29, 32 поступят через элементы ИЛИ 33, 34 на входы элементов задержки 38, 39 (с Дтзадержки Atcpa6a- тывания элементов устройства) и на входы элементов И-НЕ 46, 47.

На выходах элементов И-НЕ 46, 47 сформируются низкие уровни сигналов окончания обращения к памяти. Задние фронты сигналов высокого уровня с выходов элементов 29, 32, поступая через элементы НЕ на входы автоувеличения +1 счетчиков 10, 17, увеличат на единицу их содержимое.

Таким образом запись в память следующего слова из передаваемого массива дан- ных можно будет производить без установки следующего адреса ячейки памяти

Перед началом передачи последнего слова из передаваемого массива информации ЭВМ помещают на магистралях нечетные адреса зоны (например 1110 ХХХХХХХХХХ12 и 1111 ХХХХХХХХХХ12). При этом триггеры 11 и 16 по сигналу СИА перейдут в единичное состояние и разрешат работу элементов И 21, 22. Тогда задние фронты сигналов ВЫВОД, сопровождающие последнее слово данных, пройдут через элементы И 21, 22 и переведут триггеры 26, 27 в единичное состояние, при котором на выходах Q появятся высокие уровни сигна- лов; разрешающие прохождение управляющих сигналов ВВОД в режиме чтения информации, т.е. подготавливающие устройство к режиму чтения.

Одновременный вывод (чтение) массивов информации из блока памяти на обе магистрали. В программном режиме вывода (чтения) информации ЭВМ, подключенные к магистралям, выполняют по отношению друг к другу стандартную операцию ВВОД за два цикла. Адресный цикл выполняется аналогично операции ВЫВОД с занесением

в младший разряд кода: 0 - при чтении массивов информации. 1 - при чтении информации пословно.

После выполнения адресного цикла ЭВМ снимают с шин 50, 59 адреса и помещают на линии 52, 57 сигналы ВВОД. Эти сигналы переходят через приемники 4, 5 и, имея высокий уровень сигнала, поступают на входы элементов И 30, 31, на остальных входах которых присутствуют высокие уровни сигналов (с выходов триггеров 24,26 и 27, 28).

На выходе элементов И 30, 31 появляются высокие уровни сигналов, которые поступают на следующие элементы и производят следующие действия: на входы элементов 40, 45 - разрешают передачу кодов адреса с выходов счетчиков 10, 17 на адресные входы А2, А1 соответственно зон 482, 48ц

на входы элементов ИЛИ 35, 37 - формируют, совместно с сигналом высокого уровня с выхода элемента 36, сигналы выборки CSi, CS2 низкого уровня на выходах элементов И-НЕ41.44:

на входы элементов И 42, 43. формируя сигналы чтения W/R1, W/R2 высокого уровня; на входы направления обмена коммутаторов 13, 14, разрешая передачу информации с выходов D1, D2 зон 48i. 482 на выходы 55, 54;

на входы элементов ИЛИ 33, 34 для формирования сигналов ОТВЕТ на линии 65, 66 по окончании операции.

Задние фронты сигналов ВВОД, поступая через элементы НЕ 12, 15 на входы автоуменьшения -1 счетчиков 10, 17, уменьшат на единицу их содержимое, что позволит производить чтение следующего слова из считываемого массива данных без установки следующего адреса ячейки памяти.

По окончании чтения массива информации из блока памяти ЭВМ, формируют сигналы СБРОС, вырабатываемые программно по команде RESET. Эти сигналы, поступая на входы R триггеров 11, 16, 26, 27. установят их в нулевое состояние и подготовят устройство, к выполнению новых операций,

Одновременный ввод/вывод информационных слов в/из блока памяти на обе магистрали. В этом режиме ЭВМ в адресных циклах выставляют нечетные адреса зон памяти. При этом на выходах триггеров 11,16 устанавливаются высокие уровни сигналов, которые разрешают прохождение сигналов через элементы И 21, 22..

После выполнения адресного цикла ЭВМ выставляют сигналы ВЫВОД, которые увеличивают (аналогично вышеописанным операциям) содержимое счетчиков адреса и, проходя через элементы И 21, 22, изменяют нулевое состояние триггеров 26,

27 на единичное, разрешая считывание информации из ячейки зоны памяти на другую магистраль. ЭВМ, осуществляющая чтение информации, после адресного цикла, выставляют сигнал ВВОД, которые уменьшают содержимое счетчиков адреса и изменяют единичное состояние триггеров 26, 27 на нулевое, разрешая запись информации в ячейку памяти. Для обмена информацией через другие ячейки памяти в

адресном цикле заносятся их соответствующие адреса.

Формула изобретения Устройство для сопряжения двух магистралей, содержащее блок памяти, генератор тактовых импульсов, первый и второй триггеры, первый элемент НЕ, шесть элементов И, два коммутатора магистрали, причем выход генератора тактовых импульсов

соединен с синхровходом первого триггера и через первый элемент НЕ с синхровходом второго триггера, группа информационных входов-выходов блока памяти соединена с группой информационных входов-выходов

первого коммутатора магистрали, первые входы первого и второго элементов И соединены с первыми входами направления обмена первого и второго коммутаторов магистрали, первые входы третьего и четвертого элементов И соединены с выходом первого триггера, первые входы пятого и шестого элементов И соединены с выходом второго триггера, отличающееся тем, что, с целью повышения быстродействия, в

него введены шесть приемников, две группы приемников, четыре элемента НЕ, два счетчика адреса, два элемента сравнения зоны, четыре триггера, два коммутатора адреса, пять элементов ИЛИ. два элемента И,

два элемента задержки, четыре элемента И-НЕ, блок памяти содержит две зоны адресов, причем входы первого, второго и третьего приемников соединены соответственно с линиями вывода, синхронизации и

ввода первой магистрали, группа входов приемников первой группы соединена с линиями адреса первой магистрали, группа линий данных которой соединена с группой входов и группой выходов первого и второго

коммутаторов магистрали соответственно, входы четвертого, пятого и шестого приемников соединены соответственно с линиями ввода, синхронизации и вывода второй магистрали, группа входов приемников второй группы соединена с линиями адреса второй

магистрали, группа линий данных которой соединена с группой выходов и группой входов первого и второго коммутаторов магист- рали соответственно, выход первого приемника соединен с вторым входом третьего элемента И, третий вход которого соединен с инверсным выходом третьего триггера, первый вход седьмого элемента И соединен с выходом четвертого триггера, информационный вход которого соединен с младшим разрядом группы выходов приемников первой группы, соединенных- группой входов данных первого счетчика адреса, группа выходов которого соединена с первыми группами входом первого и вто- рого коммутаторов адреса и с первой группой входов элемента сравнения первой зоны, вторая группа входов которого является входом установки адреса первой зоны устройства, выход элемента сравнения пер- вой зоны соединен с информационным входом первого триггера, выход третьего элемента И соединен с входом второго элемента НЕ, с первыми входами первого и второго элементов ИЛИ, с вторым входом направления обмена первого коммутатора магистрали, с первым входом разрешения передачи первого коммутатора адреса, группа выходов которого соединена с группой входов адреса первой зоны блока памя- ти, вход выборки которой соединен с выходом первого элемента И-НЕ. первый вход которого соединен с выходом .второго элемента ИЛИ, второй вход которого соединен с вторым входом второго элемента И и с вторым входом разрешения передачи первого коммутатора адреса, вторая группа входов которого соединена с второй группой входов второго коммутатора адреса, с группой выходов второго счетчика адреса и с первой группой входов элемента сравнения второй зоны, вторая группа входов которого является входом установки адреса второй зоны устройства, выход элемента сравнения второй зоны соединен с инфор- мационным. входом второго триггера, выход шестого приемника соединен с вторым вхо- дом пятого элемента И. третий вход которого соединен с инверсным выходом пятого триггера, первый вход восьмого элемента И соединен с выходом шестого триггера, информационный вход которого соединен с младшим разрядом группы выходов приемников второй группы, соединенных с группой входов второго счетчика адреса, вход синхронизации которого соединен с входом синхронизации шестого триггера и с выходом пятого приемника, выход четвертого приемника соединен с-вторым входом шестого элемента И, третий вход которого соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом первого триггера, второй вход четвертого элемента И соединен с выходом третьего приемника, выход четвертого элемента И соединен с вторым входом первого элемента ИЛИ, с входом третьего элемента НЕ и с вторым входом первого элемента И, выход первого элемента ИЛИ соединен с входом первого элемента задержки и с первым входом второго элемента И-НЕ, второй вход которого соединен с выходом первого элемента задержки, выход второго элемента И-НЕ соединен с линией ответа первой магистрали, выход второго элемента НЕ соединен с входом +1 счетчика адреса и с вторым входом седьмого элемента И, выход которого соединен с входом синхронизации третьего триггера, прямой выход и информационный вход которого соединены с третьим входом шестого элемента И выход которого соединен с первым входом четвертого элемента ИЛИ, с входом четвертого элемента НЕ и с вторым входом второго элемента И, выход которого соединен с входом записи-чтения первой зоны блока памяти, вход записи-чтения второй зоны которого соединен с выходом первого элемента И, второй вход которого соединен с вторым входом первого элемента И-НЕ, с вторым входом второго элемента И, с аыхо- дом третьего элемента ИЛИ и с первым входом третьего элемента И-НЕ, выход которого соединен с входом выборки второй зоны блока памяти, группа информационных входов-выходов которого соединена с группой ВХОДОВ-РЫХОДОВ второго коммутатора магистрали, второй вход направления обмена которого соединен с первым входом пятого элемента ИЛИ, с первым входом разрешения передачи второго коммутатора адреса, с выходом пятого элемента И, с входом пятого элемента НЕ и с вторым входом четвертого элемента ИЛИ, выход которого соединен с входом второго элемента задержки и с первым входом четвертого элемента И- НЕ, второй вход которого соединен с выходом второго элемента задержки, выход четвертого элемента И-НЕ соединен с линией ответа второй магистрали, выход пятого элемента НЕ соединен с вторым входом восьмого элемента И и с входом +1 второго счетчика адреса, вход -1 которого соединен с выходом четвертого элемента НЕ и с третьим входом седьмого элемента И, выход восьмого элемента И соединен с входом синхронизации пятого триггера, прямой выход и информационный вход которого соединены с третьим входом четвертого элемента И, третий вход восьмого элемента

И соединен с выходом третьего элемента НЕ и с входом -1 первого счетчика адреса вход синхронизации которого соединен с входом синхронизации пятого триггера и с выходом второго приемника, группа адрес- ных входов второй зоны блока памяти соединена с группой выходов второго

коммутатора адреса, второй вход разрешения передачи которого соединен с первым входом первого элемента И и с вторым входом пятого элемента ИЛИ, выход которого соединен с вторым входом третьего элемента И-НЕ

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство для сопряжения двух вычислительных машин | 1986 |

|

SU1405064A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1524061A1 |

| Устройство для сопряжения вычислительной машины с магистралью обмена | 1986 |

|

SU1381519A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1545225A1 |

| Устройство для обмена информацией | 1979 |

|

SU842773A1 |

| Устройство сопряжения между процессором верхнего уровня и группой процессоров нижнего уровня иерархической мультипроцессорной системы | 1990 |

|

SU1789988A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1705832A1 |

| Устройство для сопряжения двух ЭВМ | 1990 |

|

SU1751771A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

Изобретение относится к вычислительной технике, и может быть использовано при создании многомашинных и многопроцессорных систем. Целью изобретения является повышение быстродействия. Устройство для сопряжения двух магистралей содержит блок памяти, генератор тактовых импульсов, первый и второй триггеры, элемент НЕ, шесть элементов И, два коммутатора магистрали. Введение шести приемников, двух групп приемников, четырех элементов НЕ, двух счетчиков адреса, двух элементов сравнения зоны, четырех триггеров, двух коммутаторов адреса, двух элементов И, пяти элементов ИЛИ, двух элементов задержки, четырех элементов Й- НЕ, разделение блока памяти на две зоны адресов, а также новая организация связей позволяют повысить быстродействие устройства за счет совмещения во времени операций записи/чтения информации в/из блока памяти в обе магистрали и исключения множества операций занесения адреса ячейки памяти при обмене массивами информации между магистралями. 3 ил, сл с

Составитель В.Потапенко

Редактор Г.КолядаТехред М.МоргенталКорректор1 Т.Палий

Фиг.З

| Устройство для обмена данными | 1981 |

|

SU1012235A1 |

| Устройство для сопряжения двух процессоров через общую память | 1987 |

|

SU1515172A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения двух магистралей | 1985 |

|

SU1283781A1 |

Авторы

Даты

1992-11-30—Публикация

1990-07-03—Подача