(S4) ЦИФРОВОЙ РЕГУЛЯТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегро-дифференциальный вычислитель | 1983 |

|

SU1108445A2 |

| Интегро-дифференциальный вычислитель | 1980 |

|

SU955051A1 |

| Интегро-дифференциальный вычислитель | 1981 |

|

SU1020823A1 |

| Интегродифференциальный вычислитель | 1981 |

|

SU1007105A1 |

| Интегро-дифференциальный вычислитель | 1980 |

|

SU960813A1 |

| Цифровой регулятор | 1982 |

|

SU1056130A2 |

| Интегро-дифференциальный вычис-лиТЕль | 1979 |

|

SU798902A1 |

| Цифровой регулятор | 1979 |

|

SU938253A1 |

| Квадратор | 1985 |

|

SU1258826A2 |

| Цифровой регулятор | 1981 |

|

SU974336A1 |

1

Изобретение относится к автоматике и может быть использовано в системах управления различными динамическими объектами, например в системах автоматического регулирования технологическими процессами на электростанциях.

Известен цифровой регулятор, содержащий три регистра, соединенные с сумматором, блок настройки, соединенный с одним из регистров, .блок знака, соед№ненный первым входом с первой входной шиной устройства и выходом - с входом сумматора, зейоминаюшее устройство, подключенное к одному из.регистров, блок команд, соединенный со всеми блоками устройства 1 .

Недостатками такого цифрового регулятора являются его относительная сложность, низкое быстродействие и ограниченные функциональные возможности.

Наиболее близким к изобретению по технической сущности является цифровой регулятор, содержащий первый, второй, третий и четвертый регистры, сумматор.

выход которого подключен к входу nejv вого регистра, блок настройки, блок знака, первый вход которого подключен к первому входу регулятора, блок синхронизащш, первый выход которого подключен к второму входу блока знака, третий вход которого соединен с выходом сумматора, первый блок дополнительного кода, выход и первый вход которого подключены соответственно к первому входу сумма10тора и к первому выходу блока знака, второй блок дополнительного кода, первый вход которого подключен к второму выходу блока знака,. триггер, первый вход которого подключен к второму выходу

15 блока синхронизации, первый элемент И, выход и первый вход которого подключены соответственно к второму входу первого блока дополнительного кода и к прямому выходу триггера, второй элемент И,

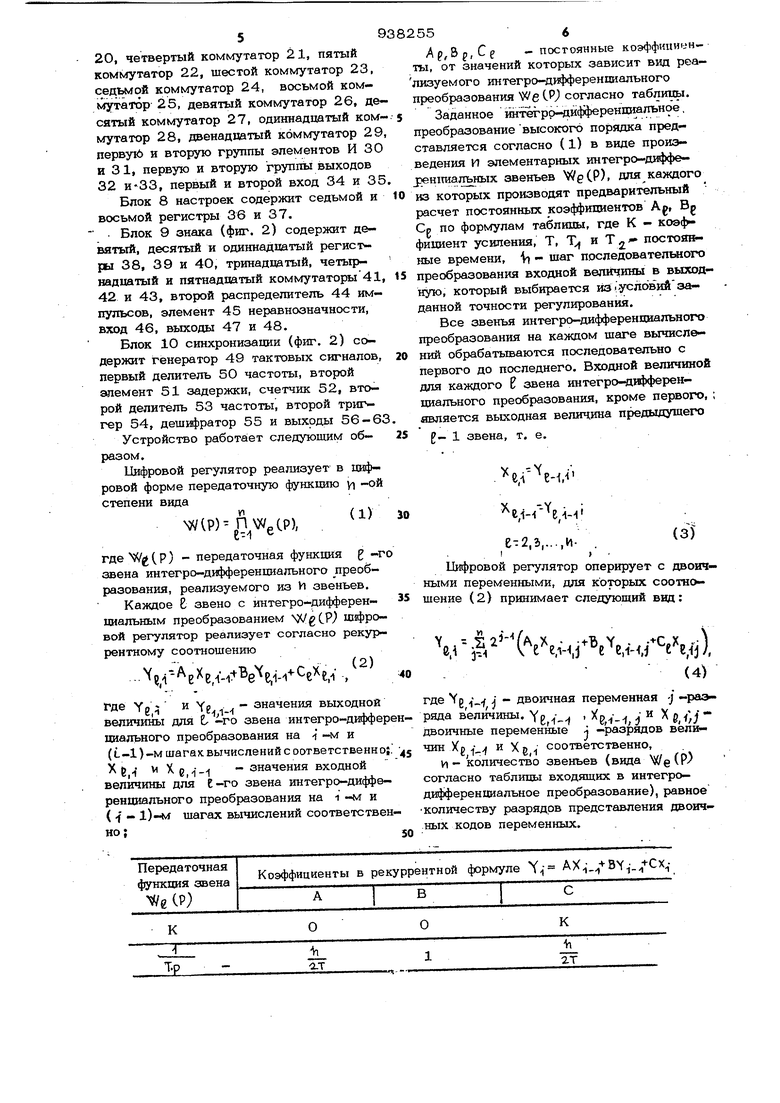

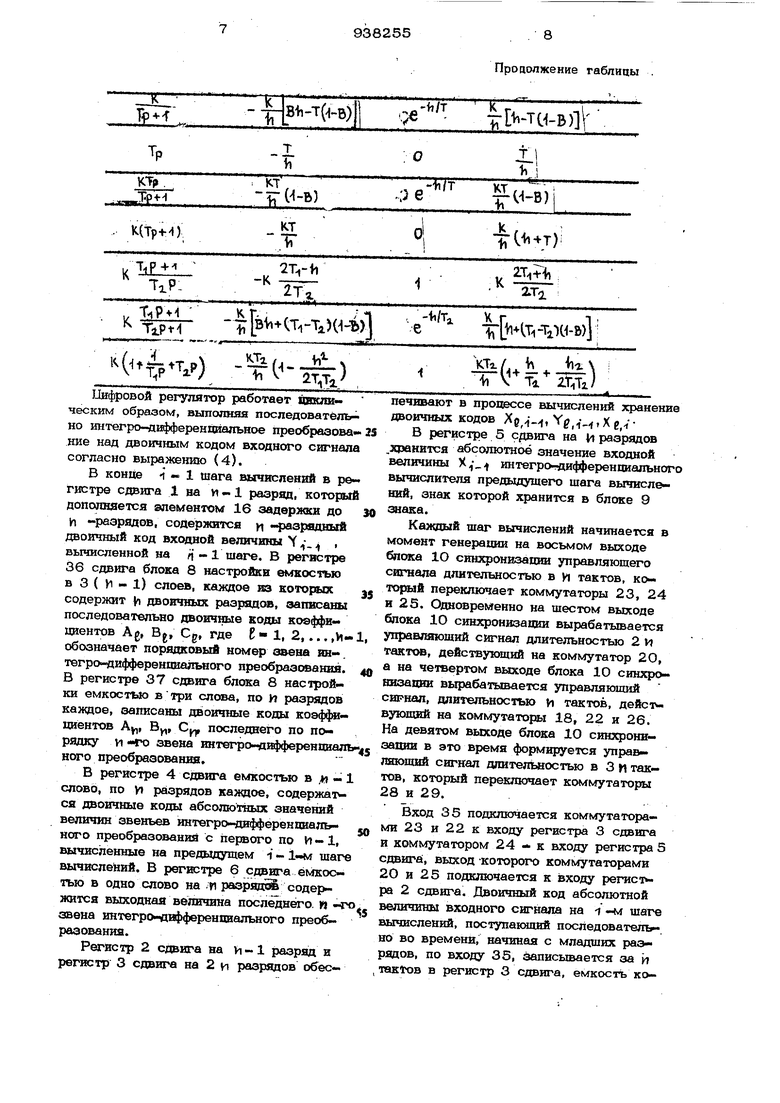

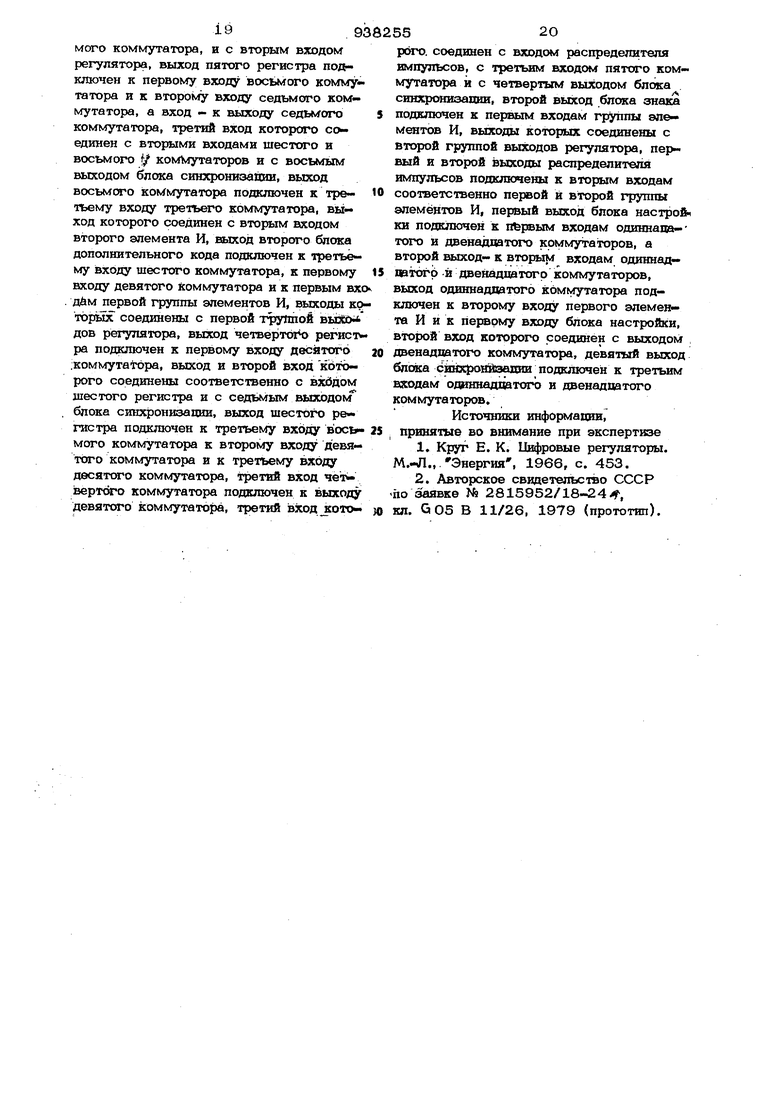

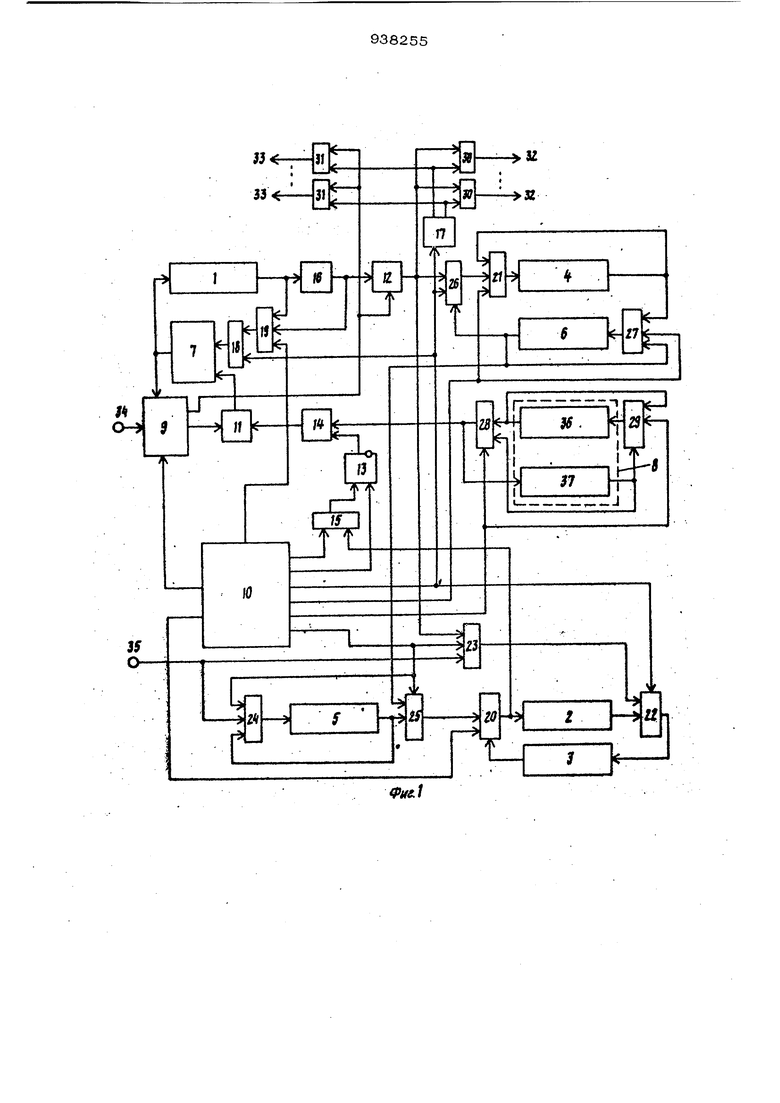

го выход и первый вход которого подключены соответственно к второму входу триггера и к третьему выходу блока синхронизации, элемент задержки, вход и выход которого подключены соответственно к выходу первого регистра и к STOpoN y входу второго блока дополнительного кода, первый коммутатор, выход и первый вход которого подключены соответственн к второму входу сумматора и к четвертому выходу блока сннхронизашга, второй коммутатор, выход, первый, второй в третий входы которого подключены соот ветственно к второму входу первого ком мутатора, к выходу первого регистра, к выходу элемента задержки и к пятому выходу блока синхронизации, третий коммутатор, выход, первый и второй входы которого подключены соответственно к входу второго регистра, к выходу третЬего регистра и к шестому выходу блока синхронизации, и четвертый коммутатор, выход, первый и второй входы которого подключены соответственно к входу четвертого регистра, к выходу четвертог регистра и к седьмому выходу блока син хронизадии f 2 . Недостаток известного регулятора заключается в ограниченных функпиональ ных возможностях, поскольку он реализует интегродифференциальные законы регулирования первого порядка. Цель изобретения - расширение функииональных возможностей цифрового регу лятора, заключакяцихся в реализации интегро-дифференциальных законов регулирования более высокого порядка. Постевленная иель достигается тем, что в него введены пятый и шестой регистры, пятый, шестой, седьмой, восьмой девятый, десятый, одиннадцатый и двенадцатый коммутаторы, распределитель импульсов, пе1юая и вторая группы элементов И, причем выход второго регис-рра соединен с первым входом пятого коммутатора, выход и второй вход которого подключены соответственно к входу т тъего регистра и к выходу шестого коммутатора, первый вход которого соединен с первым входом седьмого коммутатора и с вторым входом регулятора, выход пягоро регистра подключен к первому входу восьмого коммутатора и к второму входу седьм1зтю коммутатора, а вход - к выходу седьмого коммутатора, третий вход которого соединен с вторым входами шестого и восьмого коммутаторов и с восьмым выходом блока синхронизации, выход восьмого коммутатора подключен к третьему входу третьего коммутатора, выход которого соединен с вторым входом вто|юго элемента И, выхрд второго блока Гдополнительногсг кода подключен к третьему входу шестого коммутатора, к первому входу девятого коммутатора и к первым входам первой группы элементов И, выходы которых соединены с первой группой выходов рюгулятора, выход четвертого регистра подключен к перюому входу десятого коммутатора, выход и второй вход которого соединены соответственно с выходом шестого регистра и с седьмым выходом блока синхронизации, выход шестого регистра подключен к третьему входу восьмого коммутатора, к второму входу девятого коммутатора и к третьему входу . десятого коммутатора, третий вход четвертого коммутатора подключен к выходу девятого коммутатора, третий вход которого соединен с входом распределителя импульсов, с третьим входом пятого коммутатора и с четвертым выходом блока синхронизации, второй выход блока знака подключен к первым входам второй группы элементов И, выходы которых соединены с второй группой выходов регулятора, первый и второй выходы распределителя импульсов подключены к вторым входам соответственно первой и второй группы элементов И, первый выход блока настройки подключен к первым входам одиннадцатого и двенадцатого коммутаторов, а второй выход - к вторым входам одиннадцатого и двенадцатого коммутаторов, выход одиннадцатого коммутатора подклк чен к второму входу первого элемента И и к первому входу блока настройки, второй вход которого соединен с выходом двенадцатого коммутатора, девятый выход блока синхронизации подключен к третьим входам одиннадцатого и двенадцатого коммутаторов. Такое техническое решение цифрового регулятора позволяет реализовать множество интегро-дифференциальных законов регулирования от первого до h -го порядка. На фиг. 1 изображена блок-схема цифрового регулятора; на фиг. 2 - блок-схема блока знака и блока синхронизации. 11и)зровой регулятор содержит первый, второй, третий, четвертый, пятый и шестой регистры 1-6, сумматор 7, блок 8 настройки, блок 9 знака, блок 10 синхро1иизадии, первый 11 и второй 12 блоки дополнителы ого кода, триггер 13, и второй элементы И 14 и 15, элемент 16 задержки,распределитель 17 импульсов, первый коммутатор 18, второй коммутатор 19, третий коммутатор 20, четвертый коммутатор 21, пятый коммутатор 22, шестой коммутатор 23, седьмой коммутатор 24, восьмой коммутатор 25, девятый коммутатор 26, де сятый коммутатор 27, одиннадцатый ком мутатор 28, двенадцатый коммутатор 29 первукЬ и вторую группы элементов И 30 и 31, первую и вторую выходов 32 , первый и второй вход 34 и 3 Бпок 8 настроек содержит седьмой и восьмой регистры 36 и 37. Бпок 9 знака (фиг. 2) содержит девятый, десятый и одиннадцатый регистры 38, 39 и 40, тринадцатый, четырнадцатый и пятнадцатый коммутаторы 41 42 и 43, второй распределитель 44 импульсов, элемент 45 неравнозначности, вход 46, выходы 47 и 48. Блок 10 синхронизации (фиг. 2) содержит генератор 49 тактовых сигналов, первый делитель 50 частоты, второй элемент 51 задержки, счетчик 52, второй делитель 53 частоты, второй триггер 54, дешифратор 55 и выходы 56-6 Устройство работает следующим об- разом. Цифровой регулятор реализует в цифровой форме передаточную функцию у -ой степени вида NJV(P)-nWeCP), где V ( р) - передаточная функция g -г звена интегро-дифференциального преобразования, реализуемого из И звеньев. Каждое 6 звено с интегро-дифференодальным преобразованием (9) цифровой регулятор реализует согласно рекуррентному соотношению ,,,1 , Где и Yg . - значения выходной величины для L -го звена интегро-диффер циального преобразования на -i -м и (L-1) -м шагах вычислений с оответственн о; 6,1 Ci-i-l значения входной величины для С-го звена интегро-диффе- ренциального преобразования на 1-ми (( - 1)-м шагах вычислений соответствен °5 А р, В р, С е - постоянные коэффициенты, от значений которых зависит вид pea- лизуемого интегро-дифференциального преобразования We (.) согласно таблиць. Заданное йнтегрр- йфференшшльное, преобразование высокого порядка представляется согласно (1) в виде произведения И элементарных интегро-диффе рен1гаапъных звеньев Х/рСР), для каждого из которых производят предварительный расчет постоянных коэффициентов Ag, Bg Ср по формулам таблицы, где К - коэ4 фициент усиления. Т, Xf и Тл постоянные времени, Vi - шаг последовательного преобразования входной величины в выходную, который выбирается из/условийза данной точности регулирования. Все звенья интегро-дифференциального преобразования на каждом шаге вычислений обрабатываются последовательно с первого до последнего. Входной величиной для каждого 6 звена интегрогдифференциального преобразования, кроме первого, ; является выходная величина предыдущего Р- 1 звена, т. е. .e,i E-i-l M-l E,iH ,5,...,и. Цифровой регулятор оперирует с двоичными переменными, для которых соотношение (2) принимает следующий вид: ,(,), где Vg j - двоичная переменная -J -раэ яда вел,ины. Ye,Y 4i-, г)« S. воичные переменные Д -разрядов вели- ™и Xg е 1 соответственно, И - количество звеньев (вида (/е(Р) огласно таблицы входящих в интегро- ифференциальное преобразование), равное оличеству разрядов представления двоичых кодов переменных. у-Т, V 2T,V Цифровой регулятор работает JOBom- ческим образом, выполняя последователь но интегро-дифференвдалъное преобрвзова кие над двоичным кодом входного сигнал согласно выражению (4). В конце -1-1 шага шдчислений в ре гистре сдвига 1 на и-1 разряд, которы дополняется элементом 16 аадеряасн до И -разрядов, содержится н - зазрндный двоичный код входной величины X , вычисленной на rt - 1 шаге. В регж:тре 36 сдвига блока 8 настройки емкостью в 3 ( Я - 1) слоев, каждое из которых содержит Vi двоичных разрядов, эапшганы последовательно двоичные коды коэффициентов Ag, Eg, Cg, где Е- 1, 2, .,.,Vi« обозначает порящсовый номер звена ян-. тегро-дифференшгального преобразсташш. В регистре 37 сдвига блока 8 насчройки емкостью в три слова, по И разрядов каждое, записаны двоичные коды коэффициентов А, By,, С| последнего по порядку ц -го звена ш{твгро -д11фферен1шал ного преобразования. В регистре 4 сдвига емкостью в , слово, по У разрядов каждое, содержался двоичные коды абсолют1имх значений величин звеньев интегро-гдифференциального преобразования с первого по И - 1, вычисленные на предыдущем 1 1-м шаг вычислений. В регистре 6 сдвига ё 4кocтью в одно слово на .ц разряг содержится выходная ве личина последнего, ц н звена интегро-авфференциального преобразования. Регистр 2 сдвига на Vi- 1 разряд и регистр 3 сдвига на 2 и разрядов обесПродолжение таблицы Ti Зуь/ печивают в процессе вычислений хранение двоичных кодов Xc,-f-(. Yg,,,Xe, B регистре 5 сдвига на Vt разрядов .хранится абсолютаоё значение входной величины Х, интегрогдифференциального вычислителя предыдущего щага вычислений, знак которой хранится в блоке 9 знака. Кахшый шаг вы:числений начинается в момент генерации на восьмом выходе бпсжа 1О синхронизации управляющего сигнала длительностью в и тактов, который переключает коммутаторы 23, 24 и 25. Одновременно на шестом выходе блока 10 синхронизации вырабатывается управляющий сигнал длительностью 2 и т«ст{Ж, действующий на коммутатор 2О, а на четвертом выходе блока 10 синхронизации вырабатывается управляющий сигнал, длительностью и тактов, дейс1 вующйй на коммутаторы 18, 22 и 26. На девятом выходе блока 1О синхронизации в это время формируется управляющий сигнал дпителтыаостью в 3 и тактов, который переключает коммутаторы 28 и 29. Вход 35 подключается коммутаторами 23 и 22 к входу регистра 3 сдвига и коммутатором 24 - к входу регистра 5 сдвиги, выход -которого коммутаторами 20 и 25 подключается к входу регистра 2 сдвига. Двоичный код абсолютной величины входного сигнала на i -м шаге вычислений, поступакшшй поспедователтьно во времени, начиная с младших разрядов, по входу 35, записывается за и тактов в регистр 3 сдвига, емкость которого составляет 2 Vi разрядов. Одновременно с этим двоичный код абсопюрной. величины входного сигнала на предыдушем шаге -j - 1 вычислений, кото рый хранился в регистре 5 сдвига, пере писывается с выхода регист эа 5 сдвига через коммутаторы 25 и 20 в регистр 2 сдвига, имеющий емкость в у - 1 раз рад. По мере освобождения старших разряиов регистра 5 сдвига в них зап№сьгоается через коммутатор 24 двоичный код входного сигнала на -i -м шаге, дей ствующий на входе 35. Сигнал знака входного сигнала, поступающего по входу 34, записывается в блок 9 знака. Коммутатор 18 разрывает на и тактов цепь циркуляции двоичного кода регистра 1 сдвига через сумматор 7. Комму татор 21 и 26 подключают выход блока дополнительного кода к входу регистра 4 сдвига, выход которого подключается коммутатором 27 к входу регистра 6 сдвига емкоетыо в W разрядов. Прямой или допопнитвлыоай код выходной величию. цифрового регулятора на -i - 1-м шаге сдвигается с выхода регистра 1 через элемент 16 задержки, блок 12 дополнительного кода и коммутаторы 26 и 21 в регистр 4 сдвига, с выхода которого в это время сдвигается даоичный код абсолютного значения выходной величины первого звена интегроднфференциального преобразования на i - 1-м шаге вычислений. Блсж 12 допопнительного кода по сигналам второго блока 9 :жака преобразует дополнительный кбд регистра 1 сдвига в прямой код и прямой код регистр 1 1 сдвига пропускает без изменения. Таким образом, в регистр 4 сдвига записывает ся прямой код абсолютного значения выходной величины цифрового регулятора. Если с выхода регистра 5 сдвигается в младшем разр51де входной величины на 4 - 1-м шаге единичный сигнал, который через коммутаторы 25 и 20 поступает на вход-элемента И 15, сигнал третьего выхода блока 10 синхронизации поступит через элемент И 15 на в торой вход триг .гера 13, который перейдет из нулевого состояния в единичное. В этом случае на прямом выходе триггера 13 сформируется сигнал, который открывает элемент И 14. В это время с выхода регистра 3 сдвигается, начиная с младших разрядов, ДВО1ГЧНЫЙ код коэффициента А, который записывается через коммутатор 28 в регистр 37 сдвига и через элемент И 1 блок 11 дополнительного кода и сумматор 7 записьгеается в регистр 1 сдвига. Блок 11 дополнительного кода управляется сигналом первого выхода блока 9 знака так, что при положительном знаке произведения A.X-jJ. двоичный код коэффициента А проходит без изменения, а при от рицательном знаке - преобразуется в дополнительный код. Спустя и тактов после начала вычис- . лений на i -м шаге на четвертом и восьмом выходах блока 10 синхронизации начинают действовать сигналы .управления, которые переводят коммутаторы 18, 22, 26 и 23, 24, 25 соответственно в исход-, ное положение. В этом случае коммутатор 18 подключает выход коммутатора 19 к входу сумматора 7, коммутатор 22 подключает выход регистра 2 сдвига к входу регист ра 3 сдвига, коммутатор 26 подключает выход регистра 6 сдвига к третьему входу коммутатора 21, коммутатор 23 подключает выход блока 12 дополнительного кода к второму входу коммутатора 22, коммутатор 24 подключает ВЫХ.ОР. регистра 5 сдвига к его входу, коммутатор 25 подключает выход регистра 6 сдвига к третьему входу коммутатора 20. После этого выходной сигнал первого звена на -1 - 1-м шаге сдвигается с выхода регистра 6 через коммутаторы 25 и 2О в регистр 2 сдвига, с выхода которого через коммутатор 22 сдвигается в регистр 3 ( VI- 1) разряд двоичного кода входной величины на -i - 1-м шаге. ЕСЛИ в младшем разряде двоичного кода Y содержится единичный код, единичный сигнал с выхода регистра 6 сдвига через коммутатоуям 25 и 2О поступает Ка второй вход элемента И 15, на первом входе которого действует сигнал третьего выхода блока 1О синхрони- заш1и. В этом случае триггер 13 установится в единичное состояние выходным сигналом элемента И 15. Если в младшем разряде величины f .,. содержится нулевой код, триггер 13 установится в нулевое состояние сигналом второго выхода блока 10 синхронизации. При единичном состоянии триггера 13 сигнал его прямого выхода открывает элемент И 14. Двоичный код коэффициента В. сдвигается с выхода регистра 36 через коммутатор 28 в регистр 37 сдвига, а также через элемент И 14 и блок 11 дополнительного кода на первый вход сумматора 7, на второй вход которого в это 119 время с выхода регистра 1 через элемент 16 задержки и коммутаторы 18 и 19 сдвигается вторичный код коэффипиен- та Ау, Результат суммирования коэффициентов А и В записывается с выхода сумматора 7 в регистр 1 сдвига. Блок 11 дополнительного кода в это время управляется сигналом знака произведения ч- действующим на первом выхоп де блока 9 знака. Спустя 2 J тактов после начала вычислений на и- шаге на шестом выходе блока 10 синхронизации формируется управляющий сигнал, который возвращает коммутатор 2О в исходное состояние. Koм тyтaтop 20 под1шючает выход регистр:а 3 сдвига к входу регистра 2 сдвига, . выход icoTOporo подключен коммутатором 22 к входу регистра 3 сдвига.&1:йэзуль тат-е эаого регистры 2 и 3 объединяются в кольцевой регистр сдвига на 3 Vi -1 разряд. В момент объединения регистров 2 и 3 с выхода регистра 3 сдвигается, начиная с младших разрядов, двоичный код входной величины на I-M шаге. Если в младшем разряде величины содер }кится единичный код, единичный сигнал с выхода регистра 3 сдвига через коммуч татор 2О поступает на второй вход эле- мента И 15, открьюая его. Сигнал третъего выхода блока 10 . синхр01ШзаШП1 проходит через элемент И 15, устанав ливая триггер 13 в единичное состояние. Цели в младшем разряде величины Х содержится нулевой код, триггер 13 сбросится в нулевое сос.-сояиие сигналом второго выхода блока ID синхронизации , В случае единичного состояния триггера 13 сигнал егопрямого выхода отзфывает элемент И 14. В это время с выхода регистра 36 через коммутатор 28 сдвигается двоичный код коэффипиента С, который записывается в регистр 37 сдвига и через элемент И 14, блок 11 дополнительного кода поступает на первый вход сумматора 7. Блок 11 дополнитеяьного кода в это время управляется сиг- налом знака произведения D, , дейс вующим на первом выходе блока 9 знака, Одновременно на второй вход сумматора 7 с выхода регистра 1 сдвигается через элемент 16 за;хержки и коммутаторы 18 и 19 двоичный КОД1 суммы коэффициентов А и . Результат суммирования (А /1 + В + С) записывается с выхода сул гмтч;рра 7 в регистр 1 сдвига. Таким образом, спусг-я 3 И тактов по ле начала вычислений в рещстре 1 сдвии 5512 га сформировался двоичный код суммы произведений первых разрядов величин . YI- и v; йа двоичные коды коэффициентов А;., В и С,, соо.тветственно. Двоичные коды коэффициентов А, В, С последовательно переписывались с вы хода регистра 36 сдвига; через коммутатор 28 в регистр 37 сдвига, с выхода которого двоичные коды коэффициентов А ,Cj переписывались через коммутатор 29 в ;регистр 36 сдвига. В кольцевом регистре сдвига, образе- ванном, объединением регистров 2 и 3, емкостью в 3 Ji - 1 разрад за 3 И тактсяа произошел сдвиг на один разряд так, что с сигналами третьего выхода блока 10 синхронизации, действующим на nepBoivi входе элемента И 15, совпадают сигналы вторых разрядов величин X , У „ i . Спустя 3м тактов после начала вычислений на пятом и девятом выходах блока 10 синхронизации формируются сигналы управления, которые приводят к переключению коммутаторов 19, 28 и 29 соответственно. Коммутатор 19 подключает выход регистра 1 сдвига через коммутатор 18 к второму входу сумматора 7, Этим обеспечивается сдвиг в регистре 1 Двоичного кода накопленной суммы ко- йффициентов А, В и С на один разряд или умножение этой суммы на два. Коммутатор 29 подключает выход репястра 36 сдвига к его входу, а коммутатор 28 подключает выход регистра 37 сдвига к своему входу. В результате этого в регистре 37 сдвига запоминаются двоичные коды коэффициентов А,, В и С, а в регистре 36 сдвига - двоичные коды коэффициентов Ар, В, С,,, где 2, 3, ....И. к ( Спустя 3 И тактов после переключения коммутатора 19 на пятом выходе блока 10 синхронизации формируется сигнал управления, который возвращает коммутатор 19 в исходное состояние,. Цепь циркуляции кодов в регистре 1 сдвига вновь замыкается через элемент 16 задержки коммутаторы 18, 19 и сумматор 7. В течение Зи тактов после начала вычислений цифровой регулятор работает так же, как и на первых 3 И тактах работы. В регистре 1 сдвига накапливают ся И старших разрядов суммы произведений величин У-1, ,Y-),v- и на двоичные коды коэффициентов Д, В и С соответственно. Согласно соотнсш1ению(4) этот результат соответствует выходной величине . первого звена интегро-ди4 ференциального -лреобразования на -( -м шаге вычислений. Спустя 2 И тактов после начала вычислений на седьмом выходе- блока 10 синхронизашга формируется на время И( И- 1) тактов сигнал управления, который приводит к переключению коммутаторов 21 и 27. Если до переключения коммутаторы 21 и 27 объединяли регистры 4 и 6 в кольцевой регистр на И слов по И разрядов в каждом, после переключения коммутаторов 21 и 27 выход регистра 4 сдвига соединяется с его входом через коммутатор 21, а выход регистра 6 сдвига подключается к своему входу через коммутатор 27. После этого в регистре 4 сдвига емкостью в (Ц- 1) слов, по и разрядов каждое, осуществляется хранение последовательности величин Yg ,/ , где G 1, 2, .... И -1, а в регист зе 6 сдвига запоминается величина Y TJil-- Спустя ( м- l) и тактов после переключения коммутаторов 21 к 27 на седь мом выходе блока 10 синхронизации формируется сигнал управления, возвращающ коммутаторы 21 и 27 в исходное состоя ние. В этом случае выход регистра 6 сдв;ига подключается через коммутаторы 26 и 21 к входу регистра 4 сдвига, выход которого соединяется через комму татор 27 к входу регистра 6 сдвига. Ре гистры 4 и 6 вновь объединяются в колцевой регистр сдвига на у слов по И разрядов в каждом. Таким образом, осуществляется сдвиг последовательности величин Y -у) В 1, 2, ..., м на одно слово в кольцевом регистре сдвига, образованном регистрами 4 и 6. Спустя Зм после начала вычислений на -i - 1-м щаге или к моменту начала вычислений (Р)для второго звена интегро-дифференциального преобразования в регистре 4 сдвига содержится последовательность величин I Y --«г ..., Чу), 1--1 регистре 6 сдвига величина У,Во время первых Vi тактов вычислений для второго звена интегро-дифференциального преобразования на i -м шаге на четвертом и щестом выходах блока 10 синхронизации формируются сигналы упра ления, которые переключают коммутаторы 18, 22, 26 и 20 соответственно. Импульсный сигнал четвертого выхода блока 10 синхронизации поступает на вход распределителя 17, на первом вы5514ходе которого начинает действовать импульс, отпирающий первые элементы И 30 и 31. Двоичный код абсолютного значения /Yj-f/выходной величины закона регулирования первого порядка сдвигается с выхода регистра 1 через элемент 16 задержки, блок 12 дополнительного кода и первый элемент И 30 на первую группу выходов 32 цифрового регулятора. Знак выходной величины закона регулирования первого порядка поступает с второго выхода блока 9 знака через первый элемент И 31 на вторую группу выходов знака 33 цифрового регулятора. Двоичный код выходной величины Y-i, i первого звена интегро-дифференшиального преобразования сдвигается также с выхода регистра 1 через элемент 16 задержки, блок 12 дополнительного, кода, коммутаторы 26 и 21 в регистр 4 сдвига, с выхода которого последовательность величин . Y3,-i-f YH,- сдвигается в регистр 6. Кроме этого, величина Y f сдвигается с выхода регистра 1 через элемент 16 задержки, блок 12 дополнительного кода, коммутаторы 23 и 22 в регистр 3 в качестве входного сигнала Х - для второго звена интегро-дифференшиального преобразования. ВеличинаY i-l время сдвигает ся с выхода регистра 6 через коммутаторы 25 и 20 в регистр 2 в качестве входного сигнала j-i-f Дпя второго звена интегро-дифференциального преобразования. В последующие И тактов с выхода регистра 6 сдвинется двоичный код величины 21-1 который через коммутаторы 25 и 2О записьтается в регистр 2 сдвига. Таким образом, в кольпевой регистр сдвига, образованный объединением; регистров 2 и 3, записьшаются начальные условия Хд I-i Ya i--t 2-( необходимые для вьшолнения вычислений для второго звена интегро-диффереициального пр& образования. В первые 3 Vi тактов вычислений для второго звена интегро- ифференциального преобразования на девятом выходе блока 10 синхронизации формируется сигнал управления, который переключает коммутаторы 28 и 29. В этом случае с выхода регистра 36 через коммутатор 28 сдвигаются в регистр 37 двоичные коды коэффициентов А2 В-, и С для второго звена интегро-дифференциального преобразования, а двоичные коды коэффициентов А, В, Cxf с выхода регистра 37 сдви- гаются через коммутатор 29 на вход , регистра 36. Спустя 3h тактов коммутаторы 28 и 29 возвращаются в исходное состояние. Поэтому во время вычислений дам вто рого звена интегро-дифференииальнсяго преобразования в регистре 37 сдвига хранятся коэффшшенты Aj, В. С, а в регистре 36 сдвига - коэффициеН1« AJ, В, С, Ау B.J, С, А, В, С, ..., И И Таким образом, в регистры 2, 3 и 37 сдвига записываются двоичные коды начальных условий и коэффициектст, необходимые для выполнения вычислений 2 (р)второго звена интегро-дифференциального преобразования, которые выполняются аналогично вычислениям W (Р/ для первого звена интегро-дифференвиалъного преобразсмванкя. После ,. окончания вычислений закона регулирования второго порядка на четвер том выходе блока 1О синхронизации вырабатьюается ш пупъс, который проходит на второй выход распределителя 17 и на вторые входы вторых элементов И 30 и И 31. С выхода регистра 1 черюз элемент 16 задержки, блок 12 дополнитель ного кода я второй элемент И ЗО на вт рую выходов 32 цифрового регулятора сдвигается двоичный код абсолют рого значения lY2,-i / выходной величины згшона регулирования второго порядка. Одновременно с второго выхода блока 9 знака через второй элемент И 31 на вторую группу выходов знака 33 поступает знак выходной величины закона регулироваюш второго порядка. Вычисления для всех последующих V (р) h We(p) ннтегро-дифференаиальных закон Ь регулирования до и порядка вклю чительно выполняются аналогично. Вычисления на VI + 1-м шаг« вычислений и всех последующих для всех Н звеньев ннтегро-дифференкиалъных законов регулирования осущесШЛЯЮТСЯ аналогично. Блок 9 знака и блок 10 синхронизапии работают в пхюцессе вычислений сле дующим образом. Знак входной величины XV-i содержится в первом разряде двухразрядного регистра 38 сдвига блока 9 знака. Знак выходных величин звеньев интегро-дифференниального преобразования с первого по VI-и содержится в регистре 39 сдвига на И+ 1 разряд блока 9 знака. Знаки коэффициентов Aj , В 1, 2, ... И содержатся в регистре 40 сдвига блока 9 знака. Унаки коэффияиентов Bf и Сё, 6 1, , .... л всегда положительны и не требуют предварительной установки. Генератор 49 тактовых сигналов блока 1О синхронизации вырабатывает последовательность импульсов частоты J, которая делится делителем 50 частоты в И раз и затем задерживается элементом 51 задержки на один период тактовой частоты. Последовательность импульсов частоты f / и на вькоде делителя 50 частоты определяет И-ые такты работы ци }чхэвого peiryjutTiypa a последоватетН ность импульсовчас тоти f/и на выходе элемента 51 задержки задает первые такты работы. Счетчик 52 вьтолняет деление на 3Vt. частоты выходной последовательности импульсов элемента 51 задержки. Выходная последовательность импульсов счетчика 52 частоты f/3 и делится в У) раз делителем 53 частоты, на выходе которого формируется последовательность импульсов частоты f/ЗИ период следования которых определяет один шаг вычислений. С помощью дешифратора 55, выходы которого подключены к выходам триггеров счетчика 52, формируются пять последовательностей импульсов заданной длительности и периода следования, которые необходимы для управления работой цифрового регулятора. Каждый шаг вычислений в цифровом регуляторе начинается в момент генерации импульса на выходе делителя 53 частоты блока 1О синхронизации, который устанавливает триггер 54 в единичное состояние и сдвигает на один разряд информацию о знаке входной величины в регистре 38 сдвига блока 9 знака В результате сдвига в пе|жый разряд регистра 38 записывается знак входной величины на текущем 4 -м щаге, сигнал которого действует на входе 34, а знак входной величины на предыдущем i - 1-м шаге сдвигается из первого разряда во второй разряд регистра 38. На прямом выходе триггера 54 блока 10 синхронизации формируется сигнал, который с помощью коммутаторов 41 и 42подключает выходаг регистра 38 или репйстра 39 сдвига к входам элемента 45 неравнозначности и коммутатора 43 соответственно. Коммутатор 43по сигналам трехканального распределителя 44 импульсов опрашивает последователъно через И тактов выходы элемента 45 неравнозначности, регистра 39 сдвига и коммутатора 42. На выходе элемента 45 неравнозначности, входы которого подключены к выходу регистра 4О сдвига и через коммутатор 41 к выходам регистров 38 н 39 сдвига, формтхруется сигнал знака произведения .f или AgXg.MeYe.i.i- 2, з,.. .и На выходе У разряда регистра 39 сдвига формируется сигнал знака произведения Б , 6 1, 2, ..., W, а на выходе коммутатора 42 формируется сиг нал знака произведения С )(J или Се X g. - е 2, 3,.... и. Таким образом, на выходе коммутатора 43 каждые И тактов последователь но во времени действуют сигналы знаков произведений ,i-( , BpYp,,-( и Ce,Xe,i, е 1, 2, ......m На выходе 48 блока 9 знака действу ет сигнал выхода первого разряда регистра 39 сдвига, в который с выхода сумматора 7 по входу 46 записывается и -Ь1й знаковый разряд выходных величин Yg - , где Р 1, 2, ..., и, всех звеньев интегро-дифференшального преобразования. Технико-экономические преимущества предлагаемого цифрового регулятора по сравнению с известными заключаются в расширении функциональных возможноетей Предлагаемый дифровой регулятор позволяет реализовать интегро-дифференииальные законы регулирования высокого порядка, в то время, как известный реализует интегро-дифференциальный закон регулирования только первого порядка, Например, при представлении двоичных переменных в шфровом регуляторе на шестнадцати разрядах предлагаемое устройство реализует шестнадцать законов регулирования с первого по шестнадцатый порядок включительно. На шестнадцати выходах 32 и 33 цифрового регулятора шлрабатъшается на каждом шаге управления шестнадцать законов регулирования с первого по шестнадцатый порядок включительно. Это позволяет гибко выбирать требуемый закон регулирования в зависимости от режима работы системы управле ния объектом. Формула изобретения Цифровой регулятор, содержащий первый, второй, третий и четвертый регистры, сумматор, выход которого подключен 5518 к входу первого регистра, блок настройси, блок знака, первый вход которого подключен к первому входу регулятора, блок синхронизации, первый выход которого подключен к второму входу блока знака, третий вход которого соединен с выходом сумматора, первый блок дополнительного кода, выход и первый вход которого подключены соответственно к первому входу сумматора и к первому выходу блока знака, второй блок дополнительного кода, первый вход которого подключен к второму выводу блока знака, триггер, пераый вход которого подключен к второму выходу блока синхронизации, первый элемент И, выход и первый вход которого подключены соответстгаенно к второму входу первого блока дополнительного кода и к прямому выходу триггера, второй элемент И, выход и первый вход которого подклк чены соответственно к второму входу триггера и к третьему выходу блока син:фонизащш, элемент задержки, вход и выход которого подключены соответственно к выходу первого регистра и к второму входу второго блока дополнительного кода, первый коммутатор, выход и первый вход которого подключены соответственно к второму входу сумматора и к четвертому выходу блока синхронизашш, второй коммутатор, выход, первый, второй н третий входы которого подключены соответственно к BTOpoNfy входу первого коммутатора, к выходу первого регистра, к выходу элемента задерлжи и к пятому выходу блока синхронизации, третий коммутатор, выход, первый и второй входы которого подключены соответственно к входу второго регистра, к выходу iperbero регис-рра и к шестому выходу блока синхронизации, и четвертый коммутатор, выход, первый и второй входы которого подклк чены соответственно к входу четвертого регистра, к выходу четвертого регистра и к седьмому выходу блока синхронизации, отличающийся тем, чтоТ с целью расширения функциональных возможностей регулятора, в него введены пятый и шестой регистры, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый и двенадцатый коммутаторы, распределитель и тульсов, первая и вторая группы элементов И, причем выход второго регистра соединен с первым входом пятого коммутатора, выход и второй вход которого подключены соответственно к входу третьего регистра и к выходу шестого кoм fyтaтopa, первый вход которого соед1тен с первым входом седъ

мого коммутатора, в с вторым входом рех лятора, выход пятого регистра подключен к первому входу восьмого комму;татора и к второму входу седьмого коммутатора, а вход - к выходу седьмого коммутатора, третий вход которого со единен с вторыми входами шестого и восьмого f/ KOMViyTaTopOB и с восьмьш выходом блока синхронизации, выход восьмсяо коммутатора подключен к третьему входу третьего коммутатора, выход которого соединен с вторым входом второго элемента И, выход второго блока дополнительного кода подключен к третьему входу шестого коммутатора, к первому входу девятого коммутатора и к первым вхо ДИМ первой группы элементов И, выходы крторых соединены с первой труппой выХ(А дов регулятора, выход четвертого регист ра подключен к первому входу десятого :коммутатора, выход и второй вход которого соединены соответственно с вхбдом шестого регистра и с седьмым выходом блока синх|ронизации, выход шестогх регистра подключен к третьему входу soct мого коммутатора к второму входу девятого коммутатора и к третьему входу десятого коммутатора, третий вход чет)вертсяго коммутатора подключен к выходу девятого коммутатора, третий 1вход отх)рого. соединен с входом распределителя импульсов, с третьим входом пятого коммутатора и с четвертым выходом блока синхронизашга, второй выход блока знака подключен к первым входам группы элементов И, вьсЕоды которых соединены с второй группой выходов регулятора, первый и второй выходы распределителя импульсов подключены к вторым входам соответственно первой и второй группы элементов И, первый выход блока настрой кн подключен к пЬрвым входам одиннапатого и двенадцатого коммутаторов, а второй выход- к вторым входам одшшадттогр и двенадцатого коммутаторов, выход одиннадцатого коммутатора подключен к второму входу первого элемента И и к первому входу блока настройки, второй вход которого соединен с выходом двенадцатого коммутатора, девятый выход блока сйих{х кй эв1ши подключен к третьим входам одиннадцатого и двенадцатого коммутаторов.

Источники информации, принятые во внимание при экспертизе

кл. G05 В 11/26, 1979 (прототип).

Авторы

Даты

1982-06-23—Публикация

1980-06-19—Подача