(54) УСТРОЙСТВО ДЛЯ ИНТЕГРИРОВАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегратор | 1980 |

|

SU928351A1 |

| Цифровой интегратор | 1988 |

|

SU1580359A1 |

| Устройство для вычисления кратного интеграла | 1989 |

|

SU1647559A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1985 |

|

SU1265810A1 |

| Цифровое устройство для воспроизведения функций | 1988 |

|

SU1532945A1 |

| САМОНАСТРАИВАЮЩАЯСЯ СИСТЕМА УПРАВЛЕНИЯ ДЛЯ АСТАТИЧЕСКИХ ОБЪЕКТОВ С ЗАПАЗДЫВАНИЕМ ПО УПРАВЛЕНИЮ | 2010 |

|

RU2437137C2 |

| САМОНАСТРАИВАЮЩАЯСЯ СИСТЕМА УПРАВЛЕНИЯ ДЛЯ ОБЪЕКТОВ С ЗАПАЗДЫВАНИЕМ ПО УПРАВЛЕНИЮ | 2010 |

|

RU2437136C2 |

| СУММАТОР-ИНТЕГРАТОР | 1973 |

|

SU406207A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для решения линейных дифференциальных уравнений | 1987 |

|

SU1476486A1 |

1

Изобретение относится к области вычислительной техники и может быть использовано при построении специализированных вычислителей для решения различных зсщач, связанных с решением обыкновенных дифференциальных уравнений с начальными условия

Известен интегратор 1, содержащий усилитель постоянного тока, резисторы, переключающие элементы и конденсаторы. Данный интегратор выполнен .jia аналого,вых элементах и точность его ограничена.

Из известных устройств наиболее близким по технической сущности к изобретению является интегратор {2J, который состоит из двух блоков комбинационных сумматоров, матрицы комбинационньгх умножителей и матрицы комбинационных функциональных преобразователей, горизонтальные шины матрицы комбинационных умножителей соединены соответственно с входами - интегратора и входами первого блока комбинационных сумматрров, аналогичные шины комбинационных функциональных преобразователей соответственно соединены сг входами интегратора и с входами второго блока комбинационных сумматоров, вертикальные шины обеих матриц соединены с выходами интегратора. Это устройство предназначе«о для интегрирования решетчатых функций

с учетом граничных условий. Процесс решения задачи на таком устройстве неизбежно происходит по итерациям,, . организацию которых одним из методов осуществляет блок управления.

к 1|едостаткам данного устройства для интегрирования следует, отнести сравнительно невысокое быстродействие из-за итераций и низкую точность получаемого результата.

Целью изобретения является повышение быстродействия и точности устройства.

Поставленная цель достигается тем, что в устройство для интегрирования, содержащее блок суммирования и блок умножения значений функции на коэффициенты матриц, входы первой группы которых соединены соответственно с информационными

входами устройства, введен блок умножения значений интегральной функции в точках на табличные коэффициенты входы которого соединены соответственно с входами Зсшания интерполяционных коэффициентов, задания предшествующих значений интегрируемой функции и входом задания величины шага интегрирования устройства, а выходы подключены соответственно к входам второй группы блока суммирования, выходы которого являются выходами устройства, входы третьей группы блока суммирования соединены соответственно с выходами блока умнжения значений функции на коэффициенты матриц, входы второйi группы которого подключены соответственно к входам коэффициентов устройства, вход начальных значений интеграла и вход задания величины шага интегрирования устройства подключены к соответствующим входам блока суммирования.

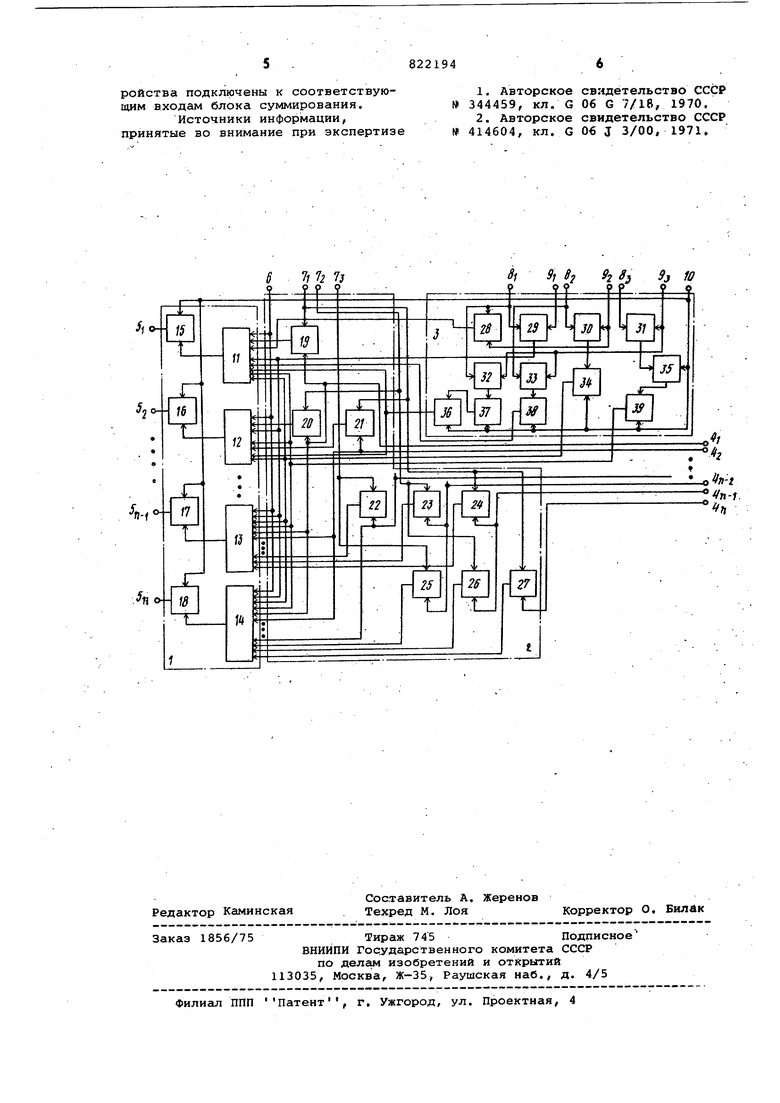

Схема устройства для случая кубической интерполяции представлен на чертеже, где обозначено: блок 1 суммирования, блок 2 умножения значений функции на коэффициенты матри блок 3 умножения значений интегральной функции в точках на табличные коэффициенты, входы 4 - 4, значений интегральной функиии устройства, выходы 5.Ц - 5 устройства, вход 6 начальных значений интеграла устройства, входы 7 - 7, коэффициентов, входы 8,( - 8 задания предшествующих значений интегральной функции, входы 9 задания интерполяционных коэффициентов, вход 10 задания величины шага интегрировани сумматоры 11-14, умножители 15-39.

Блок 1 состоит из сумматоров 1114, способных осуществлять алгебраическое суммирование (число сумматоров равно числу входов в устройство Число входов у каждого сумматора увеличивается на единицу с ростом его номера. Результат каждого суммирования до выхода из устройства умножается на величину шага интегрирования, так что блок 1 суммирования содержит и умножители 15-18.

Блок 2 содержит умножители, сгруппированные в строки, число умножителей в строке не больше степени выбраннрго интерполяционного полинома.Блок 2 предназначен для образования произведений значений вхоной функции на отличные от единицы коэффициенты матриц. Значения этих коэффициентов s каждой строке повторяются.

Блок 3 представляет собой набор умножителей, на .которых в блоке суммирования формируются выражения как произведения некоторого числа заданных предшествующих значений интегрируемой функции (число это равно степени интерполяционного полинома) на сомножители в виде различных степеней значений шага интегрирования.

Устройство работает следующим образом.

В зависимости от необходимой точности выбирают удовлетворяющую степень интерполяционного полинома К.. , Предварительно рассчитанные по формулам Грегори значения коэффициентов задают через входы 7 -j в блок 2 умножения. В блок 3 на входы 9 1 задают известные коэффициенты из таблиц. Подавая на вход

б начальное значение интеграла, на входы заданные значения интегрируемой функции в точках,предшествующих интервалу интегрирования, на вход 10 значение величины шага

5 интегрирования и на входы 4 ( - 4 п значения интегрируемой функции, на выходах получают значения интеграла от входной функции.

0 Данное устройство в отличие от известного интегратора дает возможность обеспечить любую наперед заданную точность интегрирования как предварительным выбором

5 степени интерполяционного полинома, так и выбором шага интегрирования. Кроме того, значения интеграла в каждой точке вычисляются без итераций параллельно, т.е. значение. интеграла от входной функции определяется за один такт, равный времени вычисления интеграла в последней точке.

Формула изобретения

Устройство для интегрирования, содержащее блок суммирования и блок умножения значений функции на коэффициенты матриц, входы первой группы которых соединены соответственно с информационными входами устройства, отличающееся тем, что, с Целью повышения быстродействия

, и точности, в него введен блок умножения значений интегральной функции, в точках на табличные коэффициенты,-входы которого соединены соответственно с входгши задания

интерполяционных коэффициентов, задания предшествующих значений интегрируемой функции и входом задания величины шага интегрирования устройства, а выходы подключены соответственно к входам второй группы блока, суммирования,, выходы которого являются выходами устройства, входы третьей группы блока суммирования соединены соответственно с выходами блока умножения значений

0 функции на коэффициенты матриц,

входы второй группы которого подключены соответственно к входам коэффициентов устройства,вход начальных значений интеграла и вход задания величины шага инте1 ирования устройства подключены к соответствующим входам блока суммирования.

Источники информации, принятые во внимание при экспертизе

В 7; 72 7з

8i Sf 8j $2 95 J fO

Авторы

Даты

1981-04-15—Публикация

1979-02-02—Подача