1

Изобретение относится к области вычислительной техники, может использоваться в цифровой интегрирующей машине или цифровой однородной интегрирующей структуре, которые предназначены для многократного последовательного решения систем линейных алгебраических уравнений и систем нелинейных дифференциальных уравнений, например, при решении на цифровых интегрирующих машинах или в однородных интегрирующих структурах дифференциальных уравнений с краевыми условиями, решаемых методом сведения их к носледовательности задач Коши. В этом случае рен1ение систем алгебраических уравнени 1 .может осуществляться в два раза быстрее за счет отключения канала интерполяции, а решение дифференциальных уравнений уточняется путем включения этого канала.

Известны цифровые интеграторы, а также цифровые интегрирующие и однородные цифровые интегрирующие структуры, выполненные с применением интеграторов.

1Дель изобретеиия - упрощение вычислений на начальном участке и сокращение оборудования цифрового интегратора.

Это достигается тем, что в цифровой интегратор введены ключи и схема «ИЛИ, причем первый вход второго сумматора соединен с первым входом первого ключа, второй вход первого к.тюча - с третьи.м входом интегратора, а выход первого ключа - с вторы.м входом третьего сумматора. Выход последнего подключен к первому входу второго ключа, второй вход второго ключа - к четвертому

входу интегратора, выход второго ключа - к первому входу схемы «ИЛИ. С вторым входом схемы «ИЛИ связан выход третьего ключа, первый вход третьего ключа - с выходом второго сумматора, а второй вход

третьего ключа - с пятым входом интегратора. Выход схемы «ИЛИ соединен с вторым входом блока умнон ения.

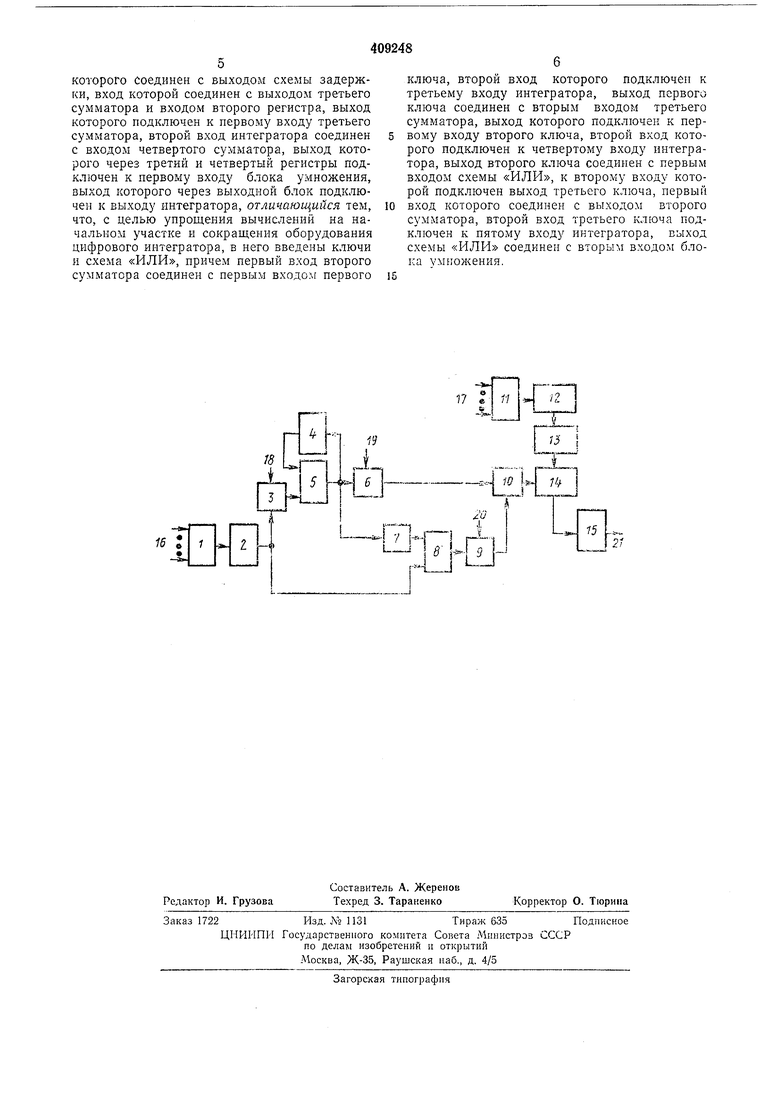

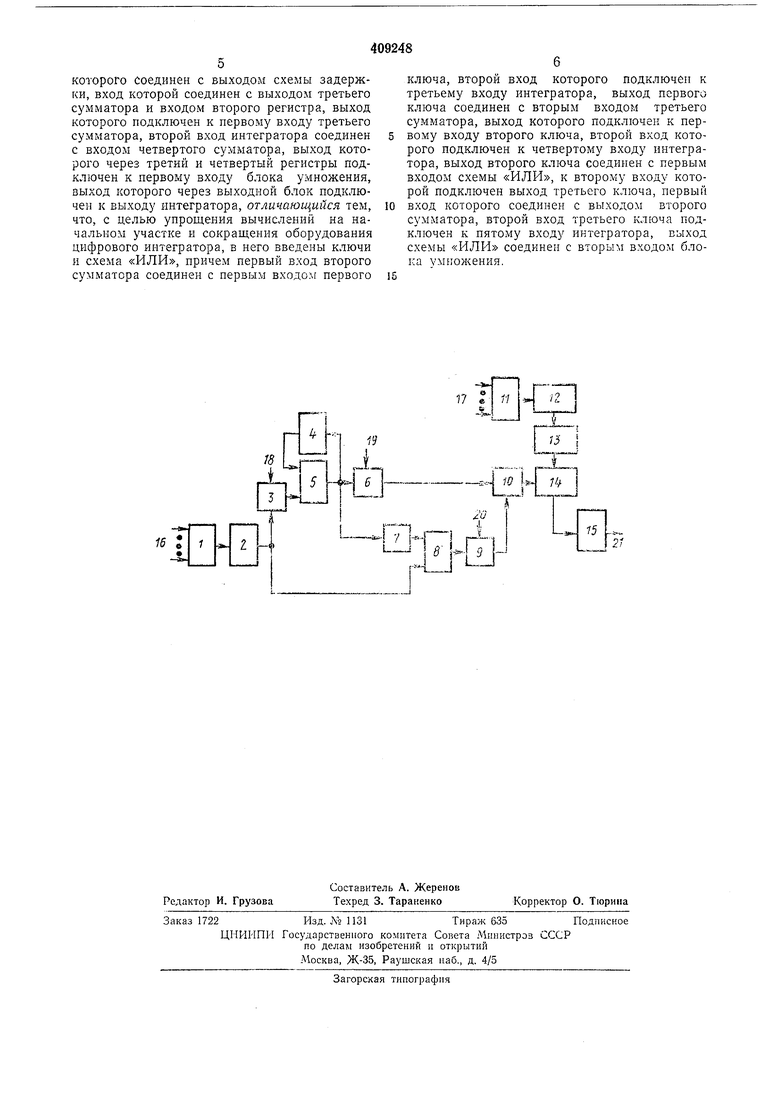

Схема цифрового интегратора показана на чертеже.

В ее состав входят: сумматор / ripnpauteннй подынтегральной функции, регистр 2 приращения подынтегральной фупкцни, ключ 3, регистр 4 подынтегральной функции, сумматор 5, ключ 6, схема 7 задержки, сумматор 8,

ключ 9, схема «ИЛИ 10, сумматор Л приращений независимой переменной, буферный регистр 12, регистр 13 нрнращения независимой переменной, блок 14 умножения, выходной блок 15. Интегратор имеет входы 16-20 и выход 21.

В интеграторе элементарный шаг нроцесса интегрирования разделяется на два этапа. Иа первом этапе вычисление осуществляется в соответствии с простейшей экстраполяционной

формулой численного интегрирования по

Стилтьесу, а на втором этапе вычисления - в соответствии с интерполяционной формулой численного интегрирования по Стилтьесу.

Ниже приводится алгоритм работы интегратора

N

и

/.1

л

и

У-1

У рк1- у рк()- V Урк1 ,

7Z д-,г+1) ф{урк1 Vf/ K +O/V- A-i)) О, yz;,,.,, 0(7./ V у 0,(V,)j

л

EVZ;,

лни

У-1

Л -

у Л- (/+)„ (l.:l)

J 1) Ф{1 У;;/.-; +-2- v7/«((-M

jZ-Kd

-1)1

0,,(vZ.O) ;

(-i-i) 1 ,lVZ.,,,,l ,,

fi:(l+l}

.v7,,;r,i)-fO,(vz,,}

у p:: () г/р™

/с 2, 3, . . . , Л .

е

y/w/.,.-,- квантованное значение ирирашений подынтегральной функции и переменной интегрирования;

vZy/ - квантованное приращение интеграла в /-М интеграторе на I-M Hiare интегрирования, получае мое по формуле трапеций;

урк1 - квантованное значение подынте гралыюй функции;

(/+и- квантованное экстраполированное значение приращений интеграла в к-м интеграторе на (t+4)-M щаге интегрирования, получаемое но формуле прямоугольников;

{...) - оператор квантования;

Ф

О

|...j - оператор выделения остатка;

„

. . . - остаток от предыдущего niara интегрирования; квантованные экстраполироваирл-(--1)

ные значения приращении подИSK( ынтегральной функции и переменной интегрирования; вектор начальных условий.

Переменные и приращения, отмеченные сверху чертой, представляют собой квантованные значения соответствующих величин.

На первом этапе вычисление осуществляется в соответствии с простейшей экстраполяционной формулой численного интегрирования по Стилтьесу. Формируется новое значение подынтегральной функции путем сложения на сумматоре 5 приращения, постунивщего из регистра 2 через ключ 5, открытый потенциалом, попадающим на вход 1&, на вход сумматора 5, и старое значение функции, снимаемое с регистра 4 подынтегральной функции, которое проходит на второй вход сумматора 5. Полученное значение подынтегральной функции с выхода сумматора 5 через ключ б, открытый потенциалом, поступающим на вход 19, через схему «ИЛИ 10 подается па блок 14 умножения. На второй вход блока 14 поступает значение независимой переменной из регистра 13. Полученное произведение направляется в выходной блок 15, где формируется остаток и квантованное приращение. Квантованное приращение используется как экстраполированное значение приращения подынтегральной функции и переменной и 1тегрирования во втором этапе элементарного шага интегрирования, в котором интегрирование осуществляется по интерполяционной формуле

трапеций в соответствии с численным интегрированием по С-гилтьесу.

Перед началом второго этапа И1ггегрирования закрываются ключи 3 п 6 и открывается ключ 9. В это время на вход 16 сумматора /

приходят приращения, полученные в результате первого этапа элементарного шага интегрирования и представляюнц е собой экстраполированные значения приращения подынтегральной функции и переменной иптегрироваиия. С выхода сумматора / результат поступает па один из входов сумматора 5 через регистр 2. На другой вход сумматора 8 попадает значение подынтегральной функции из регистра 4, которое проходит через сумматор 5 и

схему 7 задержки.

Полученное значение проходит схему 10 и перемножается в блоке /-/ умножения на скорректированное в результате первого этапа интегрирования приращение переменной интегрирования, сформированное в сумматоре // и переписанное из буферного регистра 12 в регистр 13, из которого оно и поступает па вход блока 14. С выхода блока 14 полученное произведение подается в выходной блок /5, где

квантуется и выдается в виде кваитовашюго значения приращения интеграла.

Предмет изобретения

Цифровой интегратор, содержащий сумматоры, регистры, блок умножения и выходной блок, причем первый вход интегратора соединен с входом первого сумматора, выход которого через первый регистр подключен к первому входу второго сумматора, второй вход

которого соединен с выходом схемы задержки, вход которой соединен с выходом третьего сумматора и входом второго регистра, выход которого подключен к первому входу третьего сумматора, второй вход интегратора соединен с входом четвертого сумматора, выход которого через третий и четвертый регистры подключен к первому входу блока умножения, выход которого через выходной блок подключен к выходу интегратора, отличающийся тем, что, с целью упрощения вычислений на начальном участке и сокращения оборудования цифрового интегратора, в него введены ключи и схема «ИЛИ, причем первый вход второго сумматора соединен с первым входом первого

ключа, второй вход которого подключен к третьему входу интегратора, выход первого ключа соединен с вторым входом третьего сумматора, выход которого подключен к первому входу второго ключа, второй вход которого подключен к четвертому входу интегратора, выход второго ключа соединен с первым входом схемы «ИЛИ, к второму входу которой подключен выход третьего ключа, первый вход которого соединен с выхОлЧом второго сумматора, второй вход третьего ключа подключен к пятому входу интегратора, выход схемы «ИЛИ соединен с вторым входом блока умножения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Детерминированно-вероятностныйиНТЕгРАТОР | 1979 |

|

SU840859A1 |

| Интегрирующее устройство интегрирующей машины последовательного типа | 1974 |

|

SU526927A1 |

| Цифровой интегратор для решения краевых задач | 1988 |

|

SU1501054A1 |

| Цифровой интегратор | 1977 |

|

SU732920A1 |

| Цифровой интегратор | 1979 |

|

SU903875A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Цифровой интегратор | 1974 |

|

SU519735A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU960842A1 |

| Интегро-арифметическое устройство | 1979 |

|

SU783813A1 |

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

15 г

17

У 74 I

15

Даты

1973-01-01—Публикация