ел

00

падения количества переходов белое - черное, черное - белое, равенства адресов и совпадения признаков перехода при равенстве адресов. При этом учитывается допуск на отклонение от эталона. 5 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

| АДАПТЕР КАНАЛ - КАНАЛ | 1991 |

|

RU2024050C1 |

| Устройство для обработки изображений | 1991 |

|

SU1836693A3 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Устройство для контроля печатных плат | 1986 |

|

SU1472929A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

| Устройство для вычисления положения транспортного средства | 1987 |

|

SU1495819A1 |

| Устройство обмена данными | 1988 |

|

SU1649556A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

Изобретение относится к вычислительной технике и может использоваться для контроля печатных плат. Цель изобретения - повышение производительности работы устройства. Устройство содержит блок сканирования изображения и блок синхронизации, первый и второй входы запуска, первый выход и с первого по третий входы управления синхронизацией которого соединены с первым и вторым входами режима устройства, с входом тактирования, с выходами текущего приращения, признака окончания сканирования и признака готовности блока сканирования изображения соответственно. В устройство введены блок пороговых элементов, группа блоков запоминания и сравнения элементов изображения. Каждый блок запоминания и сравнения элементов изображения содержит элемент ИЛИ, элемент задержки, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, счетчик адреса координат сканирования, первый и второй мультиплексоры управляющих сигналов, первый и второй счетчики адресов, узлы памяти адресов переходов первого и второго изображений, мультиплексор адреса переходов, узел памяти адресов ошибок, схему сравнения, узел микропрограммного управления и счетчик строк развертки. 2 ил.

Изобретение относится к вычислительной технике и может найти приме- нение, например, в системах контроля качества печатных плат.

Цель изобретения - повышение производительности работы.

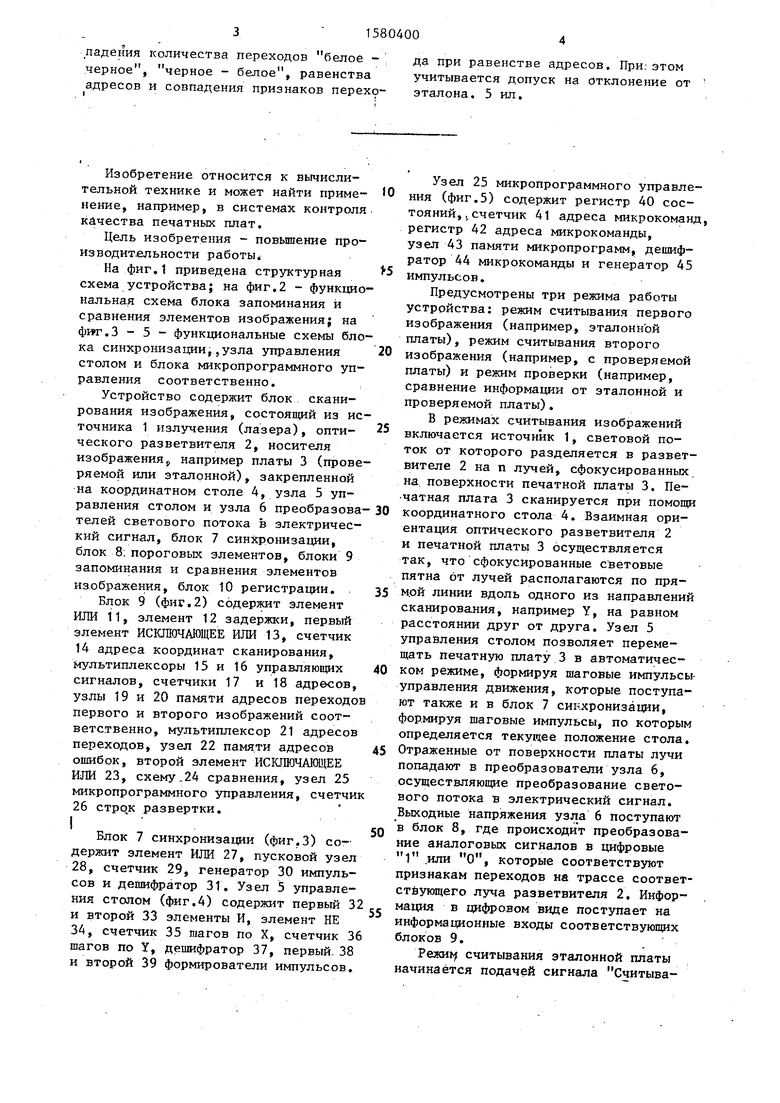

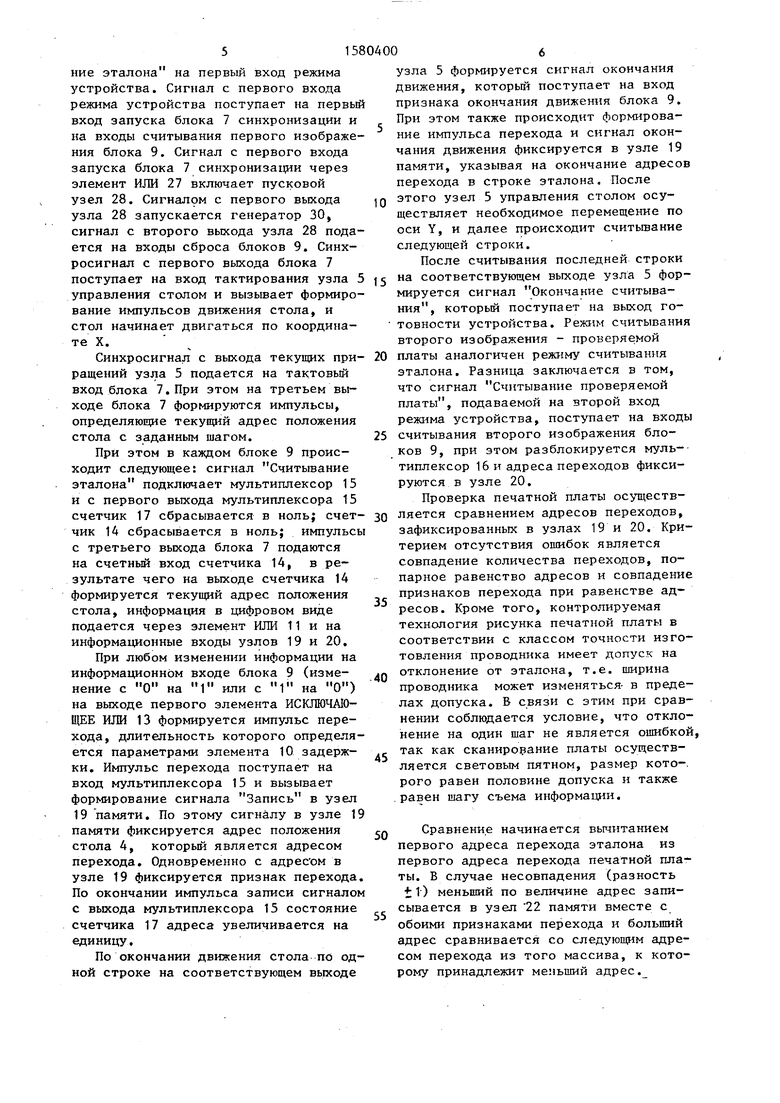

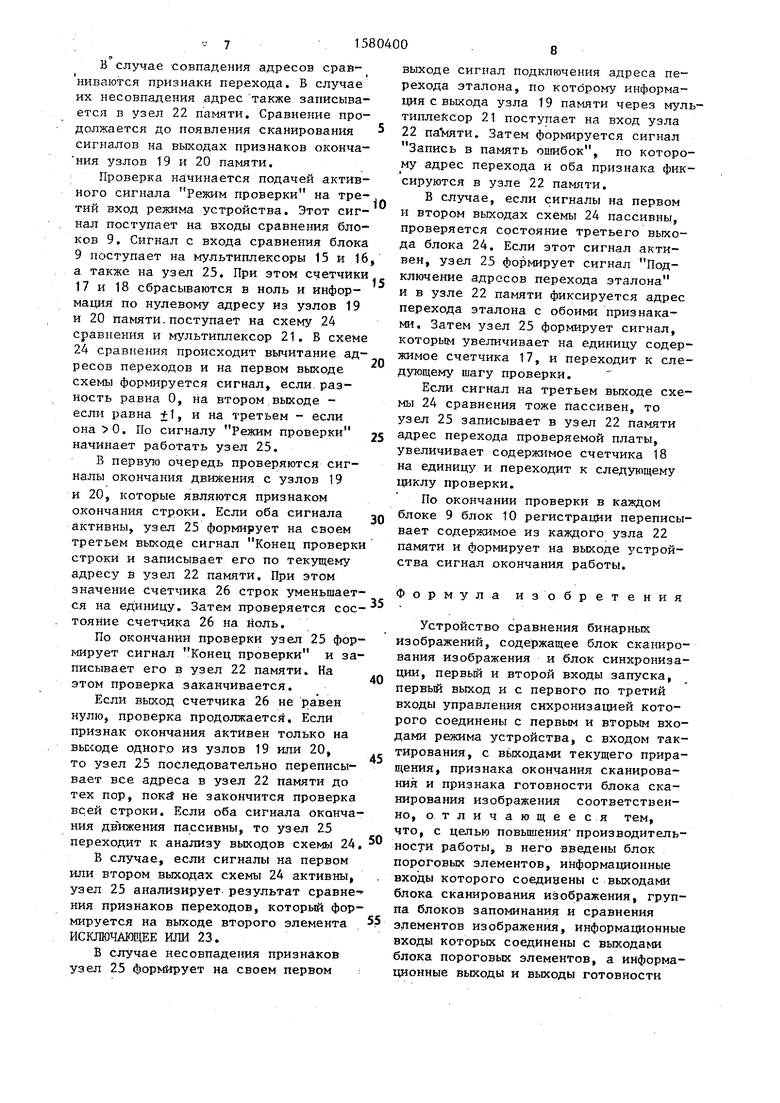

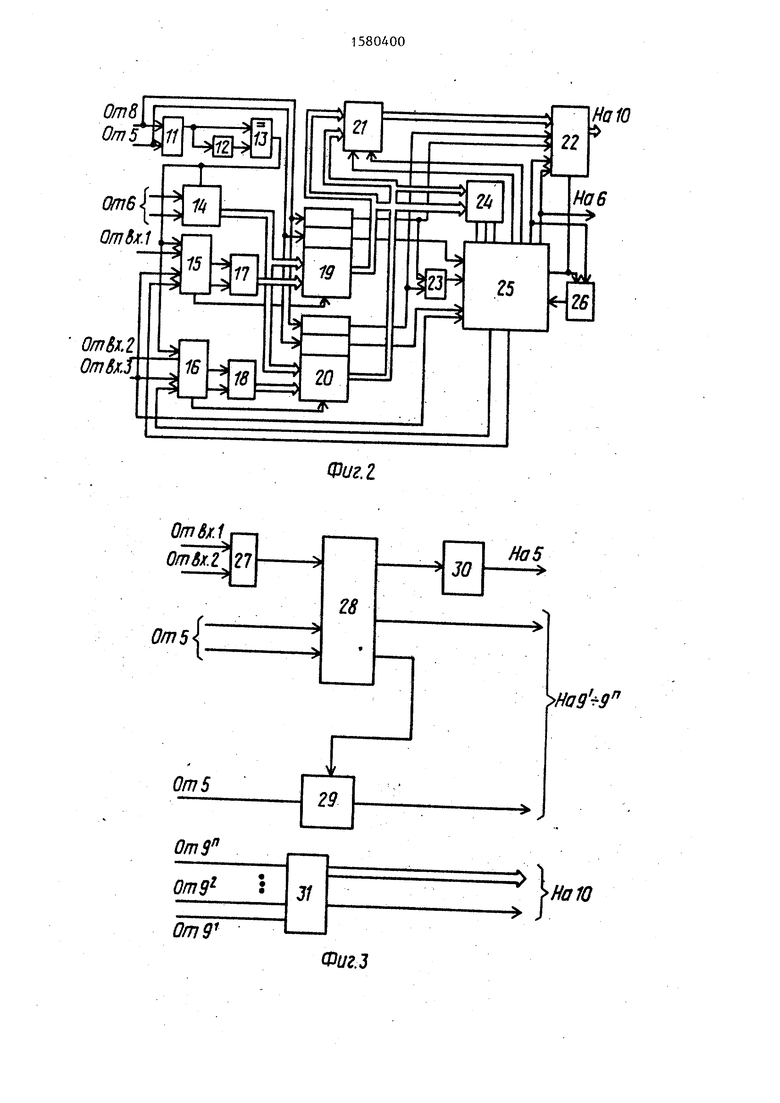

На фиг.1 приведена структурная схема устройства; на фиг.2 - функциональная схема блока запоминания и сравнения элементов изображения; на фичг.З - 5 - функциональные схемы блока синхронизации,,узла управления столом и блока микропрограммного управления соответственно.

Устройство содержит блок сканирования изображения, состоящий из источника 1 излучения (лазера), опти- ческого разветвителя 2, носителя изображения, например платы 3 (проверяемой или эталонной), закрепленной на координатном столе 4, узла 5 управления столом и узла 6 преобразова телей светового потока в электрический сигнал, блок 7 синхронизации, блок 8 пороговых элементов, блоки 9 запоминания и сравнения элементов изображения, блок 10 регистрации.

Блок 9 (фиг.2) содержит элемент ИЛИ 11, элемент 12 задержки, первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 13, счетчик 14 адреса координат сканирования, мультиплексоры 15 и 16 управляющих сигналов, счетчики 17 и 18 адресов, узлы 19 и 20 памяти адресов переходо первого и второго изображений соответственно, мультиплексор 21 адресов переходов, узел 22 памяти адресов ошибок, второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 23, схему„24 сравнения, узел 25 микропрограммного управления, счетчи 26 строк развертки.

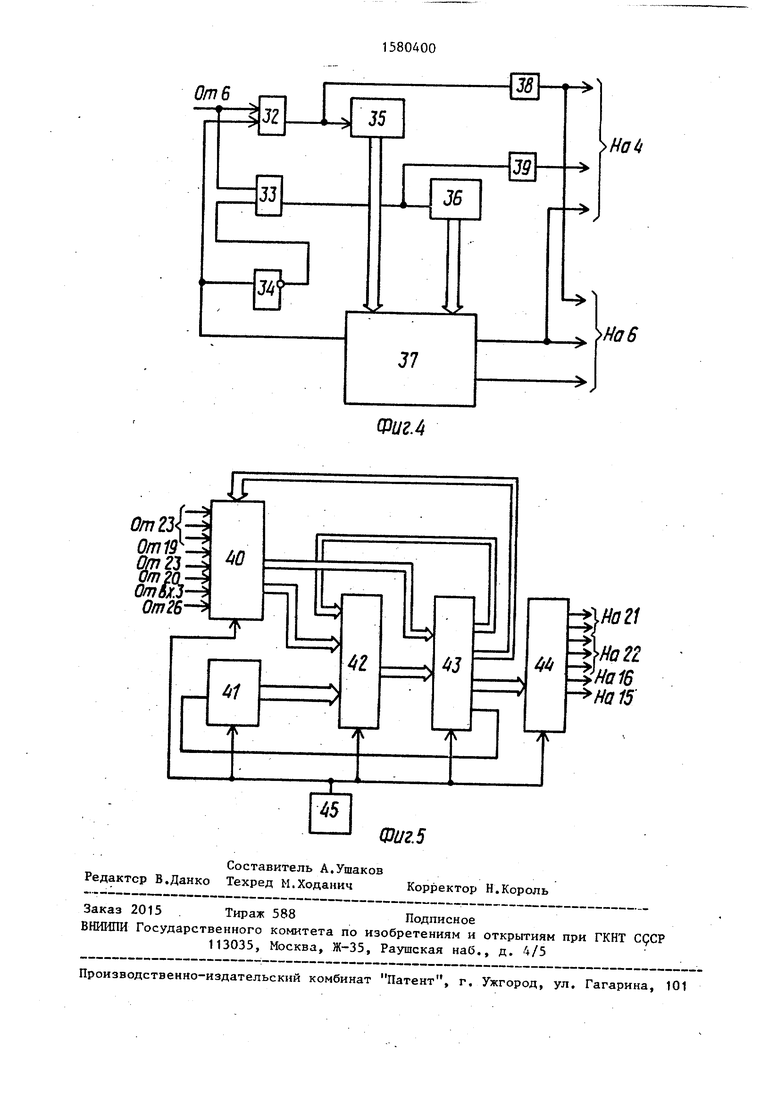

Блок 7 синхронизации (фиг.З) содержит элемент ИЛИ 27, пусковой узел 28, счетчик 29, генератор 30 импульсов и дешифратор 31. Узел 5 управления столом (фиг.4) содержит первый 3 и второй 33 элементы И, элемент НЕ 34, счетчик 35 шагов по X, счетчик 3 шагов по Y, дешифратор 37, первый 38 и второй 39 формирователи импульсов.

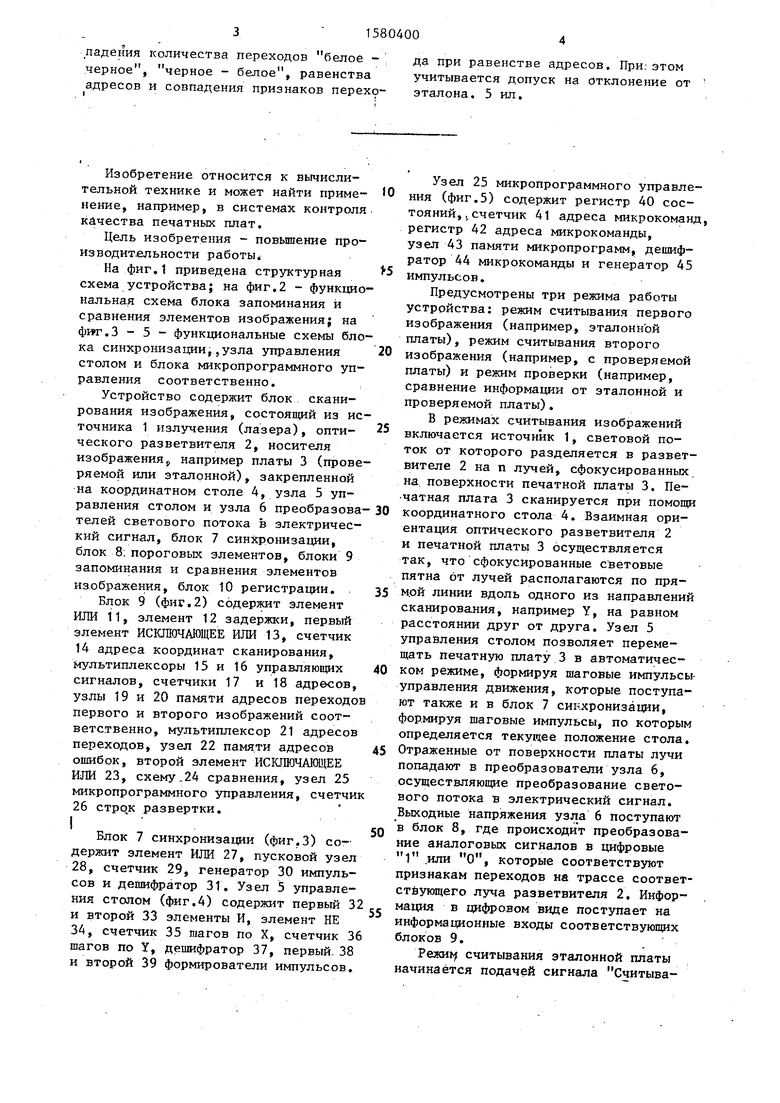

Узел 25 микропрограммного управления (фиг.5) содержит регистр 40 состояний, jсчетчик 41 адреса микрокоманд регистр 42 адреса микрокоманды, узел 43 памяти микропрограмм, дешифратор 44 микрокоманды и генератор 45 импульсов.

Предусмотрены три режима работы устройства: режим считывания первого изображения (например, эталонной платы), режим считывания второго изображения (например, с проверяемой платы) и режим проверки (например, сравнение информации от эталонной и проверяемой платы).

В режимах считывания изображений включается источник 1, световой поток от которого разделяется в развет- вителе 2 на п лучей, сфокусированных на поверхности печатной платы 3. Печатная плата 3 сканируется при помощи координатного стола 4. Взаимная ориентация оптического разветвителя 2 и печатной платы 3 осуществляется так, что сфокусированные световые пятна от лучей располагаются по прямой линии вдоль одного из направлений сканирования, например Y, на равном расстоянии друг от друга. Узел 5 управления столом позволяет перемещать печатную плату 3 в автоматическом режиме, формируя шаговые импульсы управления движения, которые поступают также и в блок 7 синхронизации, формируя шаговые импульсы, по которым определяется текущее положение стола. Отраженные от поверхности платы лучи попадают в преобразователи узла 6, осуществляющие преобразование светового потока в электрический сигнал. Выходные напряжения узла 6 поступают в блок 8, где происходит преобразование аналоговых сигналов в цифровые 1 или О, которые соответствуют признакам переходов на трассе соответствующего луча разветвителя 2. Информация в цифровом виде поступает на информационные входы соответствующих блоков 9.

Режим считывания эталонной платы начинается подачей сигнала Считывание эталона на первый вход режима устройства. Сигнал с первого входа режима устройства поступает на первый вход запуска блока 7 синхронизации и на входы считывания первого изображения блока 9. Сигнал с первого входа запуска блока 7 синхронизации через элемент ИЛИ 27 включает пусковой узел 28. Сигналом с первого выхода узла 28 запускается генератор 30, сигнал с второго выхода узла 28 подается на входы сброса блоков 9. Синхросигнал с первого выхода блока 7 поступает на вход тактирования узла 5 управления столом и вызывает формирование импульсов движения стола, и стол начинает двигаться по координате X.

Синхросигнал с выхода текущих приращений узла 5 подается на тактовый вход блока 7. При этом на третьем выходе блока 7 формируются импульсы, определяющие текущий адрес положения стола с заданным шагом.

При этом в каждом блоке 9 происходит следующее: сигнал Считывание эталона подключает мультиплексор 15 и с первого выхода мультиплексора 15 счетчик 17 сбрасывается в ноль; счетчик 14 сбрасывается в ноль; импульсы с третьего выхода блока 7 подаются на счетный вход счетчика 14, в результате чего на выходе счетчика 14 формируется текущий адрес положения стола, информация в цифровом виде подается через элемент ИЛИ 11 и на информационные входы узлов 19 и 20.

При любом изменении информации на информационном входе блока 9 (изменение с О на 1 или с 1 на О) на выходе первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13 формируется импульс перехода, длительность которого определяется параметрами элемента 10 задержки. Импульс перехода поступает на вход мультиплексора 15 и вызывает формирование сигнала Запись в узел 19 памяти. По этому сигналу в узле 19 памяти фиксируется адрес положения стола 4, который является адресом перехода. Одновременно с адресом в узле 19 фиксируется признак перехода. По окончании импульса записи сигналом с выхода мультиплексора 15 состояние счетчика 17 адреса увеличивается на единицу.

По окончании движения стола по одной строке на соответствующем выходе

0

5

0

5

0

5

0

5

0

5

узла 5 формируется сигнал окончания движения, который поступает на вход признака окончания движения блока 9. При этом также происходит формирование импульса перехода и сигнал окончания движения фиксируется в узле 19 памяти, указывая на окончание адресов перехода в строке эталона. После этого узел 5 управления столом осуществляет необходимое перемещение по оси Y, и далее происходит считывание следующей строки.

После считывания последней строки на соответствующем выходе узла 5 формируется сигнал Окончание считывания, который поступает на выход готовности устройства. Режим считывания второго изображения - проверяемой платы аналогичен режиму считывания эталона. Разница заключается в том, что сигнал Считывание проверяемой платы, подаваемой на второй вход режима устройства, поступает на входы считывания второго изображения блоков 9, при этом разблокируется мультиплексор 16 и адреса переходов фиксируются в узле 20.

Проверка печатной платы осуществляется сравнением адресов переходов, зафиксированных в узлах 19 и 20. Критерием отсутствия ошибок является совпадение количества переходов, попарное равенство адресов и совпадение признаков перехода при равенстве адресов. Кроме того, контролируемая технология рисунка печатной платы в соответствии с классом точности изготовления проводника имеет допуск на отклонение от эталона, т.е. ширина проводника может изменяться- в пределах допуска. В связи с этим при сравнении соблюдается условие, что отклонение на один шаг не является ошибкой, так как сканирование платы осуществляется световым пятном, размер кото-, рого равен половине допуска и также равен шагу съема информации.

Сравнение начинается вычитанием первого адреса перехода эталона из первого адреса перехода печатной платы. В случае несовпадения (разность 11) меньший по величине адрес записывается в узел 22 памяти вместе с обоими признаками перехода и больший адрес сравнивается со следующим адресом перехода из того массива, к которому принадлежит меньший адрес.

В случае совпадения адресов срав- ниваются признаки перехода. В случае их несовпадения адрес также записывается в узел 22 памяти. Сравнение продолжается до появления сканирования сигналов на выходах признаков оконча- ния узлов 19 и 20 памяти.

Проверка начинается подачей активного сигнала Режим проверки на третий вход режима устройства. Этот сигнал поступает на входы сравнения блоков 9. Сигнал с входа сравнения блока 9 поступает на мультиплексоры 15 и 16 а также на узел 25. При этом счетчики 17 и 18 сбрасываются в ноль и информация по нулевому адресу из узлов 19 и 20 памяти.поступает на схему 24 сравнения и мультиплексор 21. В схеме 24 сравнения происходит вычитание адресов переходов и на первом выходе схемы формируется сигнал, если разность равна 0, на втором выходе - если равна +1, и на третьем - если . По сигналу Режим проверки начинает работать узел 25.

В первую очередь проверяются сигналы окончания движения с узлов 19 и 20, которые являются признаком окончания строки. Если оба сигнала активны, узел 25 формирует на своем третьем выходе сигнал Конец проверки строки и записывает его по текущему адресу в узел 22 памяти. При этом значение счетчика 26 строк уменьшается на единицу. Затем проверяется сое- тояние счетчика 26 на ноль.

По окончании проверки узел 25 формирует сигнал Конец проверки и записывает его в узел 22 памяти. На этом проверка заканчивается.

Если выход счетчика 26 не равен нулю, проверка продолжается. Если признак окончания активен только на выходе одного из узлов 19 или 20, то узел 25 последовательно переписывает все адреса в узел 22 памяти до тех пор, пока не закончится проверка всей строки. Если оба сигнала окончания движения пассивны, то узел 25 переходит к анализу выходов схемы 24.

В случае, если сигналы на первом или втором выходах схемы 24 активны, узел 25 анализирует результат сравне- ния признаков переходов, который формируется на выходе второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 23.

В случае несовпадения признаков узел 25 формирует на своем первом

0

5

0

5

50

30

40

45

55

выходе сигнал подключения адреса перехода эталона, по которому информация с выхода узла 19 памяти через мультиплексор 21 поступает на вход узла 22 памяти. Затем формируется сигнал Запись в память ошибок, по которому адрес перехода и оба признака фиксируются в узле 22 памяти.

В случае, если сигналы на первом и втором выходах схемы 24 пассивны, проверяется состояние третьего выхода блока 24. Если этот сигнал активен, узел 25 формирует сигнал Подключение адресов перехода эталона и в узле 22 памяти фиксируется адрес перехода эталона с обоими признаками. Затем узел 25 формирует сигнал, которым увеличивает на единицу содержимое счетчика 17, и переходит к следующему шагу проверки.

Если сигнал на третьем выходе схемы 24 сравнения тоже пассивен, то узел 25 записывает в узел 22 памяти адрес перехода проверяемой платы, увеличивает содержимое счетчика 18 на единицу и переходит к следующему циклу проверки.

По окончании проверки в каждом блоке 9 блок 10 регистрации переписывает содержимое из каждого узла 22 памяти и формирует на выходе з строй- ства сигнал окончания работы.

Формула изобретения

Устройство сравнения бинарных изображений, содержащее блок сканирования изображения и блок синхронизации, первый и второй входы запуска, первый выход и с первого по третий входы управления снхронизацией которого соединены с первым и вторым входами режима устройства, с входом тактирования, с выходами текущего приращения, признака окончания сканирования и признака готовности блока сканирования изображения соответственно, отличающееся тем, что, с целью повышения производительности работы, в него введены блок пороговых элементов, информационные входы которого соединены с выходами блока сканирования изображения, группа блоков запоминания и сравнения элементов изображения, информационные входы которых соединены с выходами блока пороговых элементов, а информационные выходы и выходы готовности

} 1

информации являются одноименными выходами устройства, с первого по третий входы режима которого соединены с входами считывания первого изображения, входами считывания первого изображения и входами сравнения блоков запоминания и сравнения элементо изображения группы, входы начальной установки, адреса координат и признака окончания сканирования которых соединены с вторым и третьим выходами блока синхронизации и с выходом признака окончания сканирования блок сканирования изображения, а каждый блок запоминания и сравнения элементов изображения содержит элемент ИЛИ элемент задержки, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, счетчик

адреса координат сканирования, первый 2Q с первым и вторым входами второго

15

и второй мультиплексоры управляющих сигналов, первый и второй счетчики адресов, узлы памяти адресов переходов первого и второго изображений, мультиплексор адресов переходовт узел памяти адресов ошибок, схему сравнения, узел микропрограммного управления и счетчик строк развертки, причем в каждом блоке запоминания и сравнения элементов изображения информационный JQ вход и вход признака окончания сканирования соединены соответственно с первым и вторым входами элемента ИЛИ, с разрядами признака перехода и признака окончания сканирования информационных входов узлов памяти адресов переходов первого и второго изображений, выход элемента ИЛИ соединен с первым входом и через элемент задержки с вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с входом блокировки счетчика адреса координат сканирования и с первыми информационными входами первого и второго мультиплексоров управ- ., ляющих сигналов, первые управляющие входы которых соединены с входами считывания первого и второго изображения блока запоминания и сравнения элементов изображения, вторые управляющие входы соединены с входом сравнения блока запоминания и сравнения элементов изображения, входы начальной установки и адреса координат которого соединены с входом сброса и счетным входом счетчика адреса координат сканирования, выходы которого соединены с разрядами адреса коорди35

40

50

55

элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с соотве ствующими входами условий узла мик программного управления и с соотве ствующими информационными входами узла памяти адресов ошибок, выходы признака окончания сканирования со динены с соответствующими входами условий узла микропрограммного упр ления, выходы адреса координат ска рования соединены с первыми и втор информационными входами мультиплексора адресов переходов и схемы сра нения, выходы которой, выход второ элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и выход признака нулевого состояния счетчи строк развертки соединены с соотве ствующими входами условий узла мик ропрограммноного управления, соотв ствующие выходы которого соединены с соответствующими управляющими вх дами мультиплексора адресов перехо дов, выходы которого соединены с с ответствующими информационными вхо дами узла памяти адресов ошибок, в начальной установки которого соеди с одноименным входом счетчика стро развертки и с соответствующим выхо узла микропрограммного управления, соответствующие выходы которого со динены с соответствующими информац онными входами узла памяти адресов ошибок и с вычитающим входом счетч строк развертки и с- выходом готов сти информации блока запоминания и сравнения элементов изображения } информационный выход которого соед нен с выходом узла памяти адресов ошибок.

Ю

иат сканирования информационных входов узлов памяти адресов переходов первого и второго изображений, адрес- ные входы которых соединены с выходами первого и второго счетчиков адресов соответственно, счетные входы, входы сброса которых и входы записи узлов памяти адресов переходов первого и второго изображений соединены с выходами соответствующих разрядов, первого и второго мультиплексоров управляющих сигналов соответственно, вторые информационные входы которых соединены с соответствующими выходами узла микропрограммного управления, выходы разрядов признака перехода узлов памяти адресов переходов первого и второго изображений соединены

15

JQ .,

5

0

0

5

элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с соответствующими входами условий узла микропрограммного управления и с соответствующими информационными входами узла памяти адресов ошибок, выходы признака окончания сканирования соединены с соответствующими входами условий узла микропрограммного управления, выходы адреса координат сканирования соединены с первыми и вторыми информационными входами мультиплексора адресов переходов и схемы сравнения, выходы которой, выход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и выход признака нулевого состояния счетчика строк развертки соединены с соответствующими входами условий узла мик- ропрограммноного управления, соответствующие выходы которого соединены с соответствующими управляющими входами мультиплексора адресов переходов, выходы которого соединены с соответствующими информационными входами узла памяти адресов ошибок, вход начальной установки которого соединен с одноименным входом счетчика строк развертки и с соответствующим выходом узла микропрограммного управления, соответствующие выходы которого соединены с соответствующими информационными входами узла памяти адресов ошибок и с вычитающим входом счетчика строк развертки и с- выходом готовности информации блока запоминания и сравнения элементов изображения } информационный выход которого соединен с выходом узла памяти адресов ошибок.

Огл8

0/775

отв

0/77 AT/

Омвх.2 OmSt.5

Фиг. I

Фиг.З

Wa9 +9n

НоЮ

От 19 Oi

7/77, 0/Лд

Составитель А.Ушаков Редактор В.Данко Техред М.Ходанич Корректор Н.Король

Заказ 2015 Тираж 588Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Фиг. 4

Но 22

На 1В 15

Фиг. 5

| Устройство для контроля дефектов печатной платы | 1987 |

|

SU1406605A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-07-23—Публикация

1989-01-12—Подача