Изобретение относится к вычислительной технике и может быть использовано в качестве устройства преобразования и буферизации данных в системах контроля, а также для сопряжения ЭВМ с каналами связи.

Цель изобретения - расширенив функциональных возможностей устройства за счет обеспечения фиксации времени поступления информации.

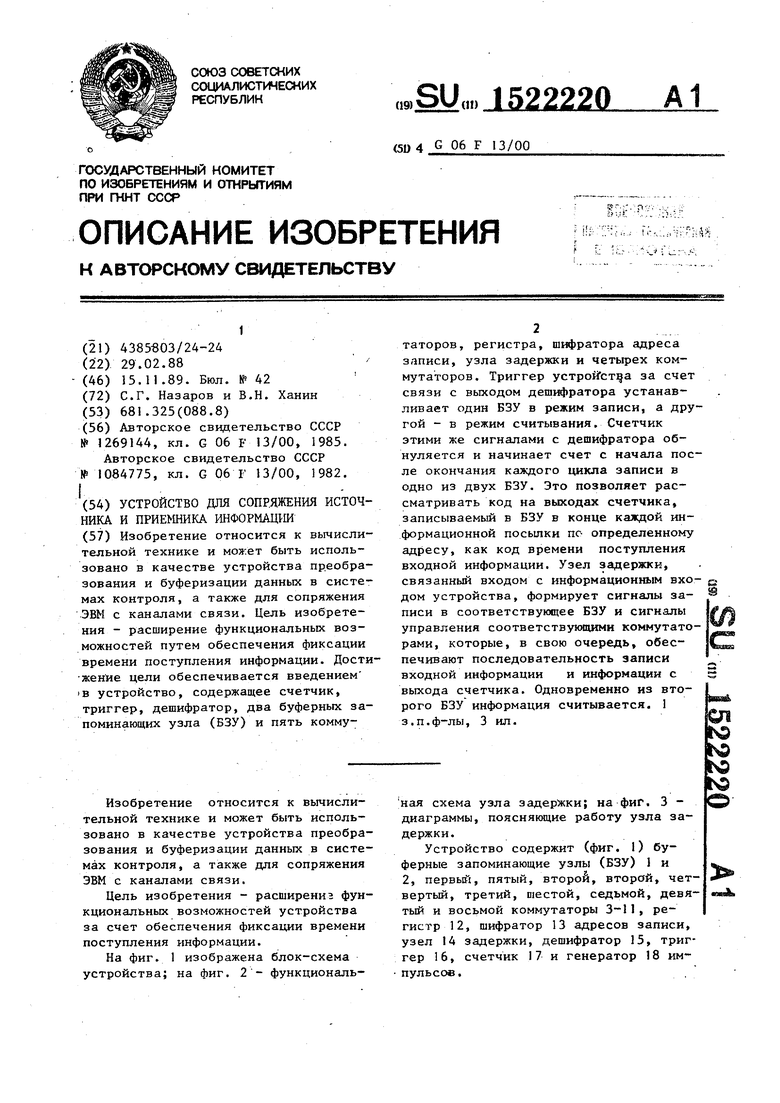

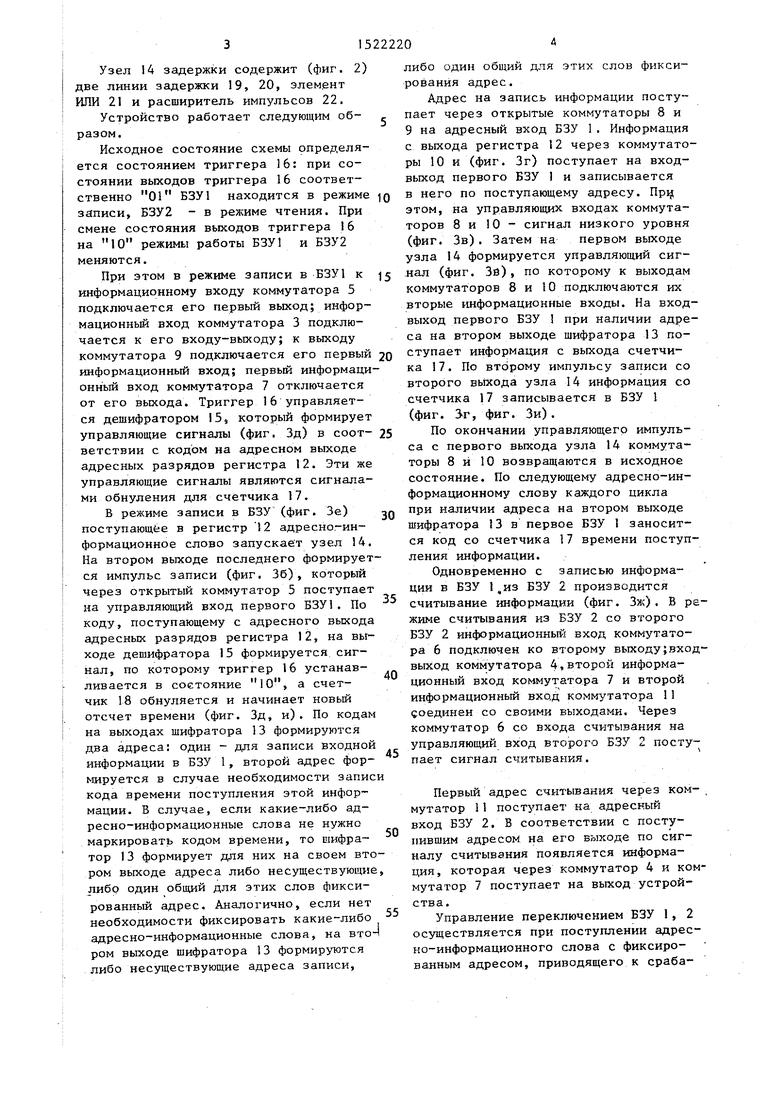

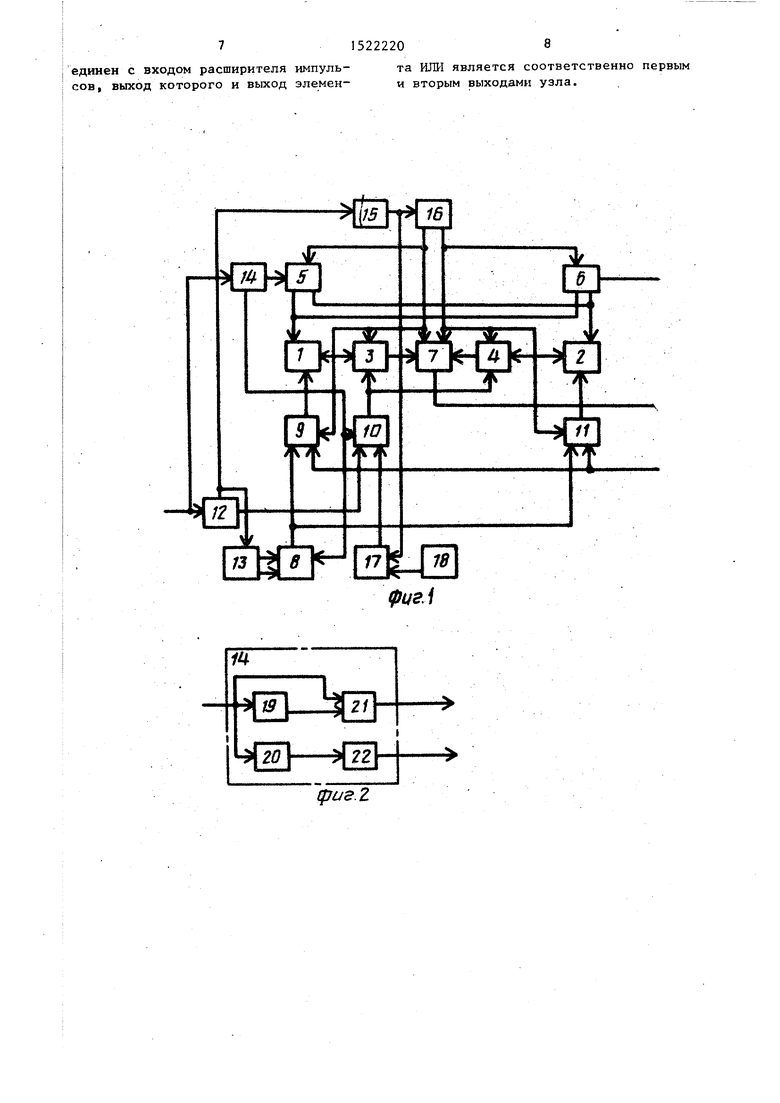

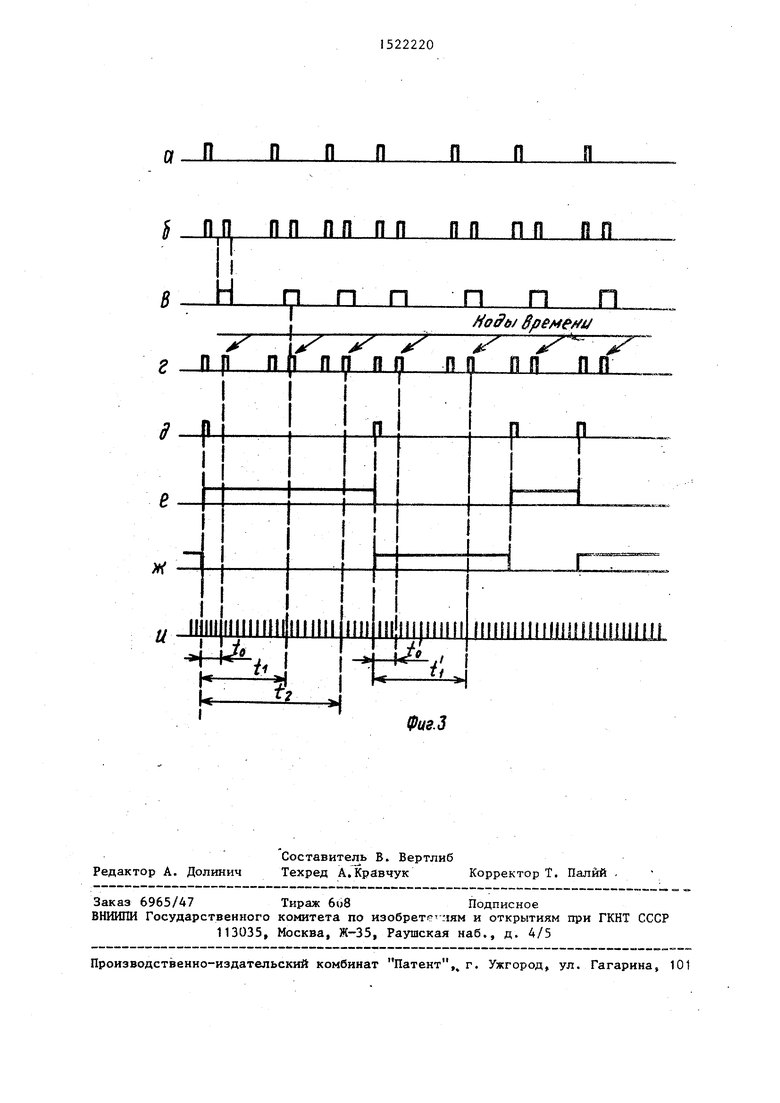

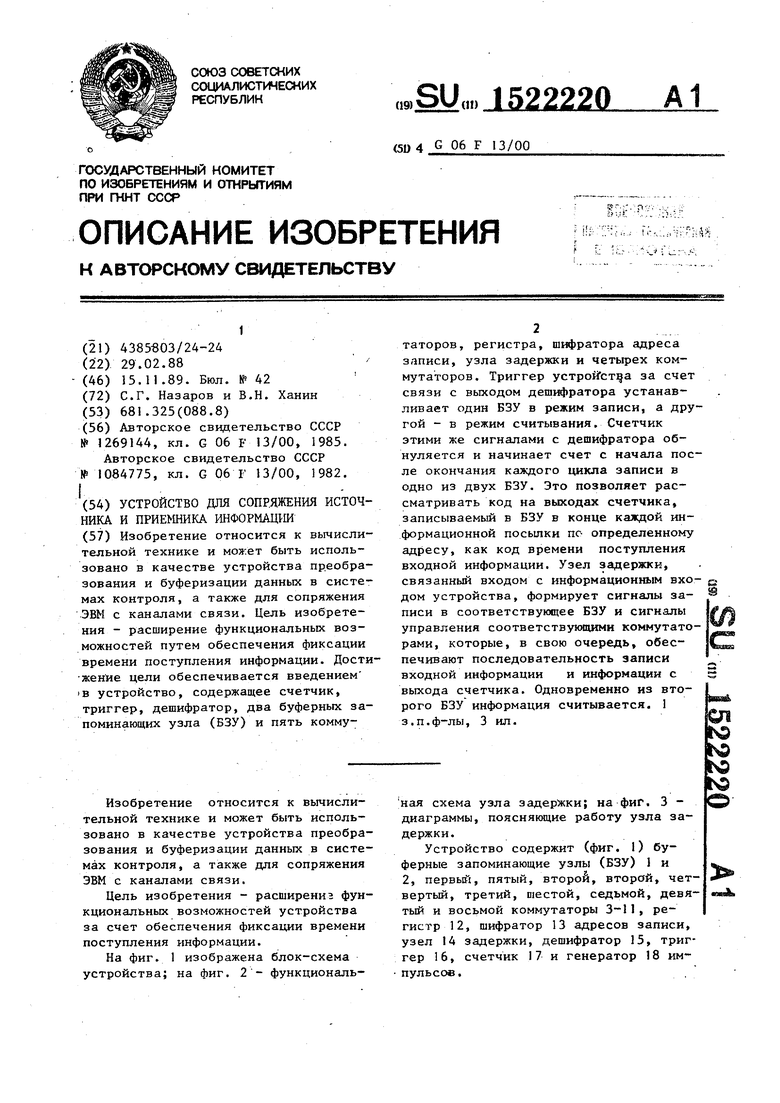

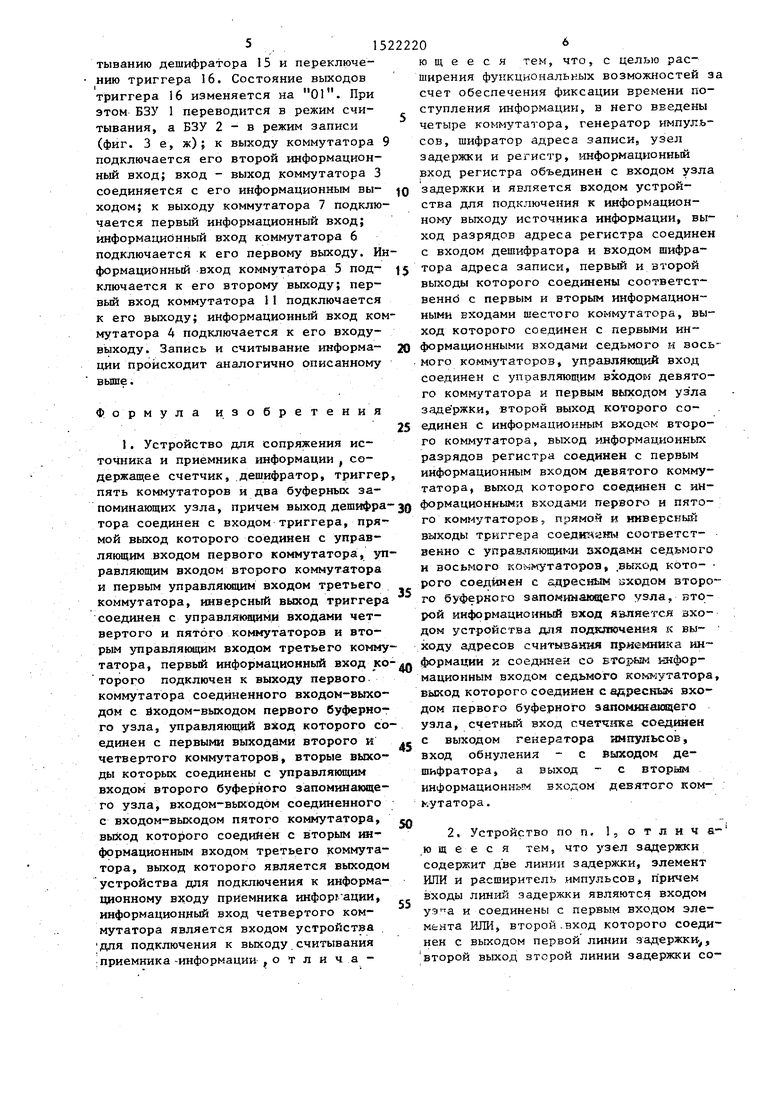

На фиг. 1 изображена блок-схема устройства; на фиг. 2- функциональ ная схема узла задержки; на фиг. 3 - диаграммы, поясняющие работу узла задержки.

Устройство содержит (фиг. 1) буферные запоминающие узлы (БЗУ) 1 и 2, первый, пятый, второй, второй, четвертый, третий, шестой, седьмой, девятый и восьмой коммутаторы 3-11, регистр 12, шифратор 13 адресов записи, узел 14 задержки, дешифратор 15, триггер 16, счетчик 17 и генератор 18 им- пульсов.

Узел 14 задержки содержит (фиг. 2) две линии задержки 19, 20, элемент ИЛИ 21 и расширитель импульсов 22.

Устройство работает следующим об- разом.

Исходное состояние схемы определяется состоянием триггера 16: при состоянии выходов триггера 16 соответственно 01 БЗУ1 находится в режиме записи, БЗУ2 - в режиме чтения. При смене состояния выходов триггера 16 на 10 режимы работы БЗУ1 и БЗУ2 меняются.

При этом в режиме записи в БЗУ1 к информационному входу коммутатора 5 подключается его первый выход; инфор- мационньй вход коммутатора 3 подключается к его входу-выходу; к выходу коммутатора 9 подключается его первый информационный вход; первый информаци онньй вход коммутатора 7 отключается от его выхода. Триггер 16 управляется дешифратором 15, который формирует управляющие сигналы (фиг. Зд) в соот- ветствии с кодом на адресном выходе адресных разрядов регистра 12. Эти же управляющие сигналы являются сигналами обнуления для счетчика 17.

В режиме записи в БЗУ (фиг. Зе) поступающее в регистр 12 адресно-информационное слово запускает узел 14. На втором выходе последнего формируется импульс записи (фиг. 36), который через открытый коммутатор 5 поступает на управляющий вход первого ВЗУ1. По коду, поступающему с адресного выхода адресных разрядов регистра 12, на вьг- ходе дешифратора 15 формируется сигнал, по которому триггер 16 устанавливается в состояние 10, а счетчик 18 обнуляется и начинает новый отсчет времени (фиг. Зд и). По кодам на выходах шифратора 13 формируются два адреса: один - для записи входной информации в БЗУ 1, второй адрес формируется в случае необходимости запис кода времени поступления этой информации. В случае, если какие-либо адресно-информационные слова не нужно маркировать кодом времени, то шифратор 13 формирует для них на своем втором выходе адреса либо несуществующие либр один общий для этих слов фиксированный адрес. Аналогично, если нет необходимости фиксировать какие-либо адресно-информационные слова, на втоН ром выходе шифратора 13 формируются либо несуществующие адреса записи.

0

5

0

5

либо один общий для этих слов фиксирования адрес.

Адрес на запись информации поступает через открытые коммутаторы 8 и 9 на адресный вход БЗУ 1. Информация с выхода регистра 12 через коммутаторы 10 и (фиг. Зг) поступает на вход- выход первого БЗУ 1 и записывается в него по поступающему адресу. Прц этом, на управляющих входах коммутаторов 8 и 10 - сигнал низкого уровня (фиг. Зв). Затем на первом выходе узла 14 формируется управляющий сигнал (фиг. Зв), по которому к выходам коммутаторов 8 и 10 подключаются их вторые 1шформационные входы. На вход- выход первого БЗУ при наличии адреса на втором выходе шифратора 13 поступает информация с выхода счетчика 17. По второму импульсу записи со второго вь1хода узла 14 информация со счетчика 17 записывается в БЗУ 1 (фиг. Зг, фиг. Зи).

По окончании управляющего импульса с первого выхода узла 14 коммутаторы 8 и 10 возвращаются в исходное состояние. По следующему адресно-информационному слову каждого цикла при наличии адреса на втором выходе шифратора 13 в первое БЗУ 1 заносится код со счетчика 17 времени поступления информации.

Одновременно с записью информации в БЗУ 1,из БЗУ 2 производится считывание информации (фиг. Зж). В режиме считывания из ВЗУ 2 со второго БЗУ 2 информационный вход коммутатора 6 подключен ко второму выходу;вход- выход коммутатора 4 второй информационный вход коммутатора 7 и второй информационный вход коммутатора 11 соединен со своими выходами. Через коммутатор 6 со входа считывания на управляющий вход второго ВЗУ 2 поступает сигнал считывания.

Первый адрес считывания через ком- , мутатор 11 поступает на адресный вход БЗУ 2, В соответствии с посту- пившим адресом на его выходе по сигналу считывания появляется информация, которая через коммутатор 4 и коммутатор 7 поступает на выход устройства.

Управление переключением БЗУ 1, 2 осуществляется при поступлении адресно-информационного слова с фиксированным адресом, приводящего к сраба

тыванию дешифратора 15 и переключению триггера 16. Состояние выходов триггера 16 изменяется на 01. При этом БЗУ 1 переводится в режим считывания, а БЗУ 2 - в режим записи (фиг. 3 е, ж); к выходу коммутатора 9 подключается его второй информационный вход; вход - выход коммутатора 3 соединяется с его информационным выходом; к выходу коммутатора 7 подключается первый информационный вход; информационный вход коммутатора 6 подключается к его первому выходу. Информационный вход коммутатора 5 под- ключается к его второму выходу; первый вход коммутатора I1 подключается к его выходу; информационный вход коммутатора 4 подключается к его входу- выходу. Запись и считывание информации происходит аналогично описанному выше.

Формула изобретения

25 единен с информационным входом второго коммутатора, вькод илформационньпс разрядов регистра соединен с первым информационным входом девятого татора, выход которого соединен с ин35

1. Устройство для сопряжения источника и приемника информации , содержащее счетчик, дешифратор, триггер, пять коммутаторов и два буферных запоминающих узла, причем выход дешифра-jg формационными входами первого и пято- тора соединен с входом триггера, пря- го коммутаторов. прямой и ннверсньш мой выход которого соединен с управляющим входом первого коммутатора, управляющим входом второго коммутатора и первьм управлякмцим входом третьего коммутатора, инверсный выход триггера соединен с управлякщими входами четвертого и пятого коммутаторов и вторым управляющим входом третьего коммутатора, первый информационный вход ко-ля формации и соедннен со вторьгм кнфор- торого подключен к выходу первого. мационным входом седьмого кон ;утатора, коммутатора соединенного входом-выходом с йходом-вькодом первого буферного узла, управляющий вход которого соединен с первыми выходами второго к четвертого коммутаторов, вторые выходы которых соединены с управляющим входом второго буферного запоминающего узла, входом-выходом соединенного с входом-выходом пятого коммутатора, выход которого соединен с В1торым Ю1- формационным входом третьего коммутатора, выход которого является выходом

4S

выходы триггера соедкната соответственно с управляющими входамн седьмого и восьмого коммутаторов, .выход кото- рого соединен с адресным аходом второго буферного запоминающего уэла, второй информационный вход является входом устройства для подключен ия к вы- ходу адресов считывания приемника инвыход которого соединен с адресным входом первого буферного запоминающего узла, счетный вход счетчика соединен с выходом генератора импульсов вход обнуления - с шифратора, а выход информационном входом к.утатора.

выходом дес вторым девятого ком50

2. Устройс.тво по п, 1, о т л и ч аю щ ее с я тем, что узел задержки содержит две линии задержки, элемент ШИ и расширитель импульсов, причем входы лин1-1й задержки являются входом уэпа и соединены с первым входом элемента ИЛИ, второй.вход которого соеди иен с выходом первой линии задержки-, второй выход второй линии задержки со-

устройства для подключения к информационному входу приемника инфop aции, информационный вход четвертого коммутатора является входом устройства ДЛЯ подключения к выходу считывания I приемника -информации отлича

ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет обеспечения фиксации времени поступления информации в него введены четыре коммутатора, генератор импуль сов, шифратор адреса записи, узел задержки и регистр, информационный вход регистра объединен с входом узла задержки и является входом устройства для подключения к информационному выходу источника информации, выход разрядов адреса регистра соединен с входом дешифратора и входом шифратора адреса записи, первый и второй выходы которого соединены соответст- веннй с первым и Еторь м информационными входами шестого коммутатора, выход которого соединен с первыми информационными входами седьмого к вось- . МОго коммутаторов, управляющий вход соединен с управляющим входом девятого коммутатора и первым выходом узла задержки, второй выход которого соединен с информационным входом второго коммутатора, вькод илформационньпс разрядов регистра соединен с первым информационным входом девятого татора, выход которого соединен с информационными входами первого и пято- го коммутаторов. прямой и ннверсньш формации и соедннен со вторьгм кнфор- мационным входом седьмого кон ;утатора,

35

jg формационными входами первого и пято- го коммутаторов. прямой и ннверсньш ля формации и соедннен со вторьгм кнфор- мационным входом седьмого кон ;утатора,

выходы триггера соедкната соответственно с управляющими входамн седьмого и восьмого коммутаторов, .выход кото- рого соединен с адресным аходом второго буферного запоминающего уэла, второй информационный вход является входом устройства для подключен ия к вы- ходу адресов считывания приемника инjg формационными входами первого и пято- го коммутаторов. прямой и ннверсньш ля формации и соедннен со вторьгм кнфор- мационным входом седьмого кон ;утатора,

S

выход которого соединен с адресным входом первого буферного запоминающего узла, счетный вход счетчика соединен с выходом генератора импульсов вход обнуления - с шифратора, а выход информационном входом к.утатора.

выходом дес вторым девятого комформационными входами первого и пято- го коммутаторов. прямой и ннверсньш формации и соедннен со вторьгм кнфор- мационным входом седьмого кон ;утатора,

2. Устройс.тво по п, 1, о т л и ч а ю щ ее с я тем, что узел задержки содержит две линии задержки, элемент ШИ и расширитель импульсов, причем входы лин1-1й задержки являются входом уэпа и соединены с первым входом элемента ИЛИ, второй.вход которого соеди иен с выходом первой линии задержки-, второй выход второй линии задержки со-

единен с входом расширителя импуль- та ИЛИ является соответственно первым сов, выход которого и выход элемен- и вторым выходами узла.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1988 |

|

SU1583938A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1096692A1 |

| Устройство для организации очередности приема информации | 1983 |

|

SU1128255A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1019495A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1984 |

|

SU1234843A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1985 |

|

SU1298762A2 |

| Устройство для сопряжения вычислительной машины с телеграфными каналами связи | 1986 |

|

SU1392571A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1783581A1 |

| Микропрограммное вычислительное устройство | 1981 |

|

SU1008741A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве устройства преобразования и буферизации данных в системах контроля, а также для сопряжения ЭВМ с каналами связи. Цель изобретения - расширение функциональных возможностей путем обеспечения фиксации времени поступления информации. Достижение цели обеспечивается введением в устройство, содержащее счетчик, триггер, дешифратор, два буферных запоминающих узла /БЗУ/ и пять коммутаторов, регистра, шифратора адреса записи, узла задержки и четырех коммутаторов. Триггер устройства за счет связи с выходом дешифратора устанавливает один БЗУ в режим записи, а другой - в режим считывания. Счетчик этими же сигналами с дешифратора обнуляется и начинает счет с начала после окончания каждого цикла записи в одно из двух БЗУ. Это позволяет рассматривать код на выходах счетчика, записываемый в БЗУ в конце каждой информационной посылки по определенному адресу, как код времени поступления входной информации. Узел задержки, связанный с информационным входом устройства, формирует сигналы записи в соответствующее БЗУ и сигналы управления соответствующими коммутаторами, которые в свою очередь, обеспечивают последовательность записи входной информации и информации с выхода счетчика. Одновременно из второго БЗУ информация считывается. 1 з.п.ф-лы, 3 ил.

(риг. 2

iTJt-H

фиг,

Of

n

П П П

S n П П П пп П П П П П П П П

в

id

лП П

kн

П

П

По.

Фие.З

| Устройство для ввода информации | 1985 |

|

SU1269144A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для ввода информации | 1982 |

|

SU1084775A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-11-15—Публикация

1988-02-29—Подача