ся оо

Ь

о 41

Юо

Изобретение относится к радиотехнике и может быть использовано в цифровых синтезаторах частоты.

Целью изобретения является повышение быстродействия.

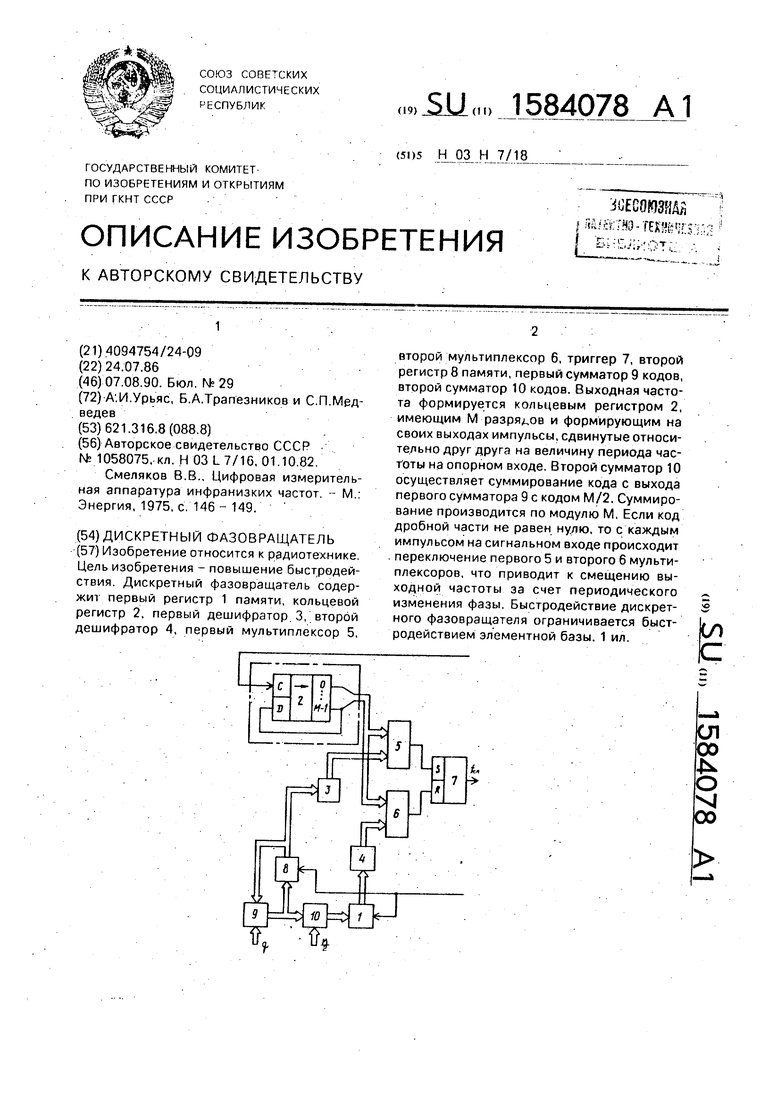

На чертеже представлена структурная электрическая схема дискретного фазовращателя.

Дискретный фазовращатель содержит первый регистр 1 памяти, кольцевой регистр 2, первый 3, второй 4 дешифраторы, первый 5, второй 6 мультиплексоры, триггер 7, второй регистр 8 памяти, первый 9 и второй 10 сумматоры кодов.

Дискретный фазовращатель работает следующим образом.

На опорный и сигнальный входы дискретного фазовраа ателя поступают две импульсные последовательности f0 и Ти, при этом частота fo на опорном входе в К раз выше частоты (и на сигнальном входе. Выходная частота fBbix формируется кольцевым регистром 2, имеющим М разрядов и формирующим на своих выходах импульсы, сдвинутые относительно друг друга на То l/fo, а частота повторения импульсной последовательности на каждом выходе кольцевого регистра 2 равна -- :° .

М Т0 м

Код дробной части q (целочисленность рассматривается относительно частоты Ти) поступает на первый сумматор 9, где суммируется с выходным кодом второго регистра 8, код которого с каждым импульсом ти увеличивается на величину q. Причем суммирование ведется по модулю М, а результат переполнения первого сумматора 9 не используется.

Во втором сумматоре 10 осуществляется суммирование кода с выхода первого сумматора 9 с кодом М/2, поступающим на второй вход второго сумматора 10. Суммирование также производится по модулю М. Код суммы с выхода второго сумматора 10 записывается в первом регистре 1 в виде кода, который по тактовым импульсам через второй дешифратор 4 поступает на управляющие входы второго мультиплексора 6. На управляющие входы первого мультиплексора 5 через первый дешифратор 3 поступает код с выхода второго регистра 8. Следовательно, импульсная последовательность на первом входе триггера 7 всегда сдвинута на Ml/2 относительно импульсной последовательности на втором входе триггера 7 и на его выходе формируется сигнал в форме меандра.

Если код дробной части q равен нулю, то коды на выходе второго регистра 8 и

второго сумматора 10 постоянны во времени и период выходного сигнала триггера 7 равен МТо и частота твых fo/M. Если код q не равен нулю, то с каждым импульсом ти

происходит переключение первого 5 и второго б мультиплексоров, которое приводит к увеличению одного периода сигнала fBux на величину qTo, которая составляет q/M-ю долю периода выходной частоты триггера 7.

0 Эквивалентное смещение частоты (Вых за счет периодического изменения фазы на q/M-ю долю периода каждые /ги секунд равно

Af Ч/М i.f5 л м f Таким образом,частота сигнала

I q , К - q ,

Т Ти - -гг Ги .

МТ0 М

М

Дискрет изменения частоты равен ти/М

Сдвиг фазы происходит один раз за период сигнала частотой ти. Быстродействие дискретного фазовращателя ограничивается быстродействием элементной базы Единственное ограничение К 2М.

Формула изобретения

Дискретный фазовращатель, содержащий первый регистр памяти, кольцевой регистр, триггер, при этом сигнальный вход первого регистра памяти и сигнальный вход

кольцевого регистра являются соответственно сигнальным и опорным входами дискретного фазовращателя, отличаю щи й- с я тем, что, с целью повышения быстродействия, введены последовательно соединенные первый сумматор кодов, второй регистр памяти, первый дешифратор и первый мультиплексор, второй сумматор кодов и последовательно соединенные второй дешифратор и второй мультиплексор, выход которого подключен к R-входу триггера, 5-вход которого соединен с выходом первого мультиплексора, второй вход которого объединен с вторым входом второго мультиплексора и подключен к выходу кольцевого регистра. вход второго дешифратора соединен с выходом первого регистра памяти, первый вход и выход второго сумматора кодов подключены соответственно к выходу первого сумматора кодов и к входу первого регистра

памяти, первый вход первого сумматора кодов соединен с выходом второго регистра памяти, тактовый вход второго регистра памяти подключен к сигнальному входу первого регистра памяти, второй вход первого

5 сумматора кодов и второй вход второго сумматора кодов являются соответственно входом кодового сигнала дробной части и входом кодового сигнала целой части дискретного фазовращателя, а выход триггера

является выходом дискретного фазовращателя

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство поворота изображения на экране телевизионного приемника | 1987 |

|

SU1424028A1 |

| Устройство для решения системы линейных алгебраических уравнений | 1986 |

|

SU1405073A1 |

| СПОСОБ ФОРМИРОВАНИЯ КОГЕРЕНТНОГО ОПТИЧЕСКОГО СИГНАЛА СУММИРОВАНИЕМ ПУЧКОВ ИЗЛУЧЕНИЯ N ЛАЗЕРОВ В ВЕРШИНЕ КОНИЧЕСКОЙ ПОВЕРХНОСТИ И ПЕРЕДАТЧИК КОГЕРЕНТНОГО ОПТИЧЕСКОГО ИЗЛУЧЕНИЯ, РЕАЛИЗУЮЩИЙ ЭТОТ СПОСОБ | 1992 |

|

RU2109384C1 |

| Цифровой синтезатор частот | 1989 |

|

SU1691926A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПСЕВДОСЛУЧАЙНОГО СИГНАЛА | 1989 |

|

SU1692272A1 |

| Измеритель частоты | 1989 |

|

SU1691768A1 |

| Цифровой накопитель с дробной переменной емкостью | 1987 |

|

SU1481756A1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ УГЛА ПОВОРОТА ВАЛА В КОД | 1993 |

|

RU2108663C1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1327267A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

Изобретение относится к радиотехнике. Цель изобретения - повышение быстродействия. Дискретный фазовращатель содержит первый регистр 1 памяти, кольцевой регистр 2, первый дешифратор 3, второй дешифратор 4, первый мультиплексор 5, второй мультиплексор 6, триггер 7, второй регистр 8 памяти, первый сумматор 9 кодов, второй сумматор 10 кодов. Выходная частота формируется кольцевым регистром 2, имеющим M разрядов и формирующим на своих выходах импульсы, сдвинутые относительно друг друга на величину периода частоты на опорном входе. Второй сумматор 10 осуществляет суммирование кода с выхода первого сумматора 9 с кодом M/2. Суммирование производится по модулю M. Если код дробной части не равен нулю, то с каждым импульсом на сигнальном входе происходит переключение первого 5 и второго 6 мультиплексоров, что приводит к смещению выходной частоты за счет периодического изменения фазы. Быстродействие дискретного фазовращателя ограничивается быстродействием элементной базы. 1 ил.

| Цифровой синтезатор частот | 1982 |

|

SU1058075A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление, увеличивающее число оборотов движущихся колес паровоза | 1919 |

|

SU146A1 |

Авторы

Даты

1990-08-07—Публикация

1986-07-24—Подача