СП

Од

00 Од

Изобретение относится к вычисли - тельной технике, в частности к устройствам умножения, и может быть непользовано в арифметических устройствах ЭВМ.

Цель изобретения - увеличение быстродействия устройства,

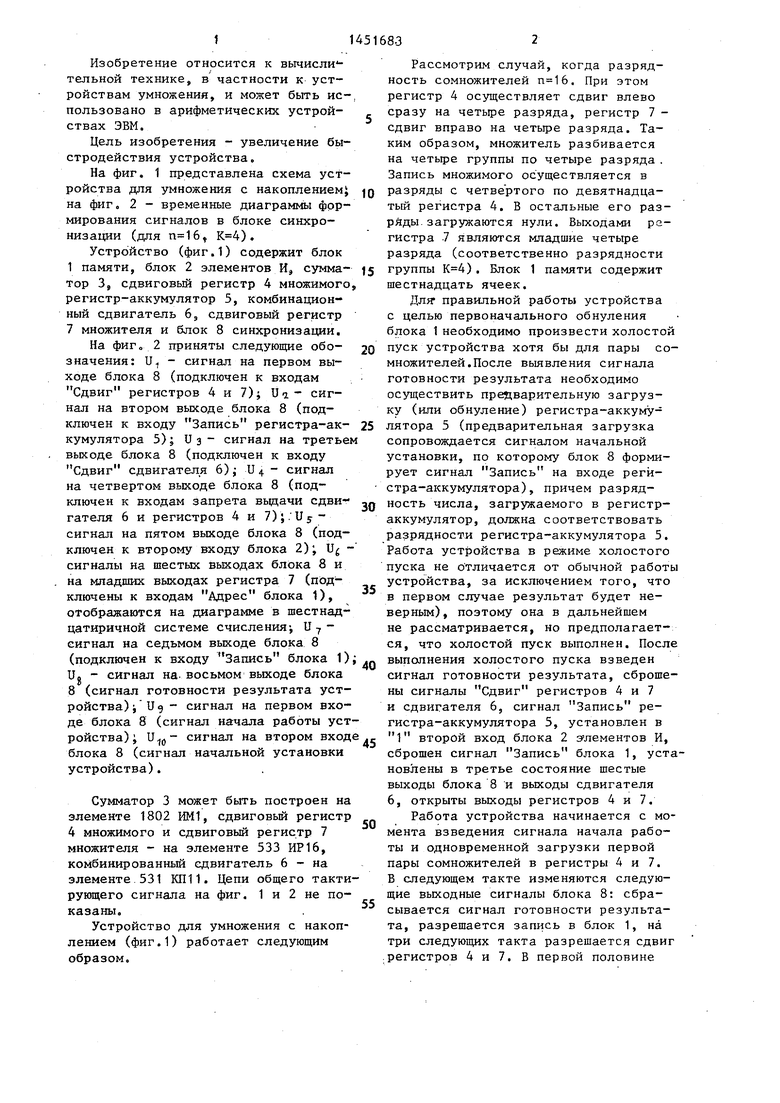

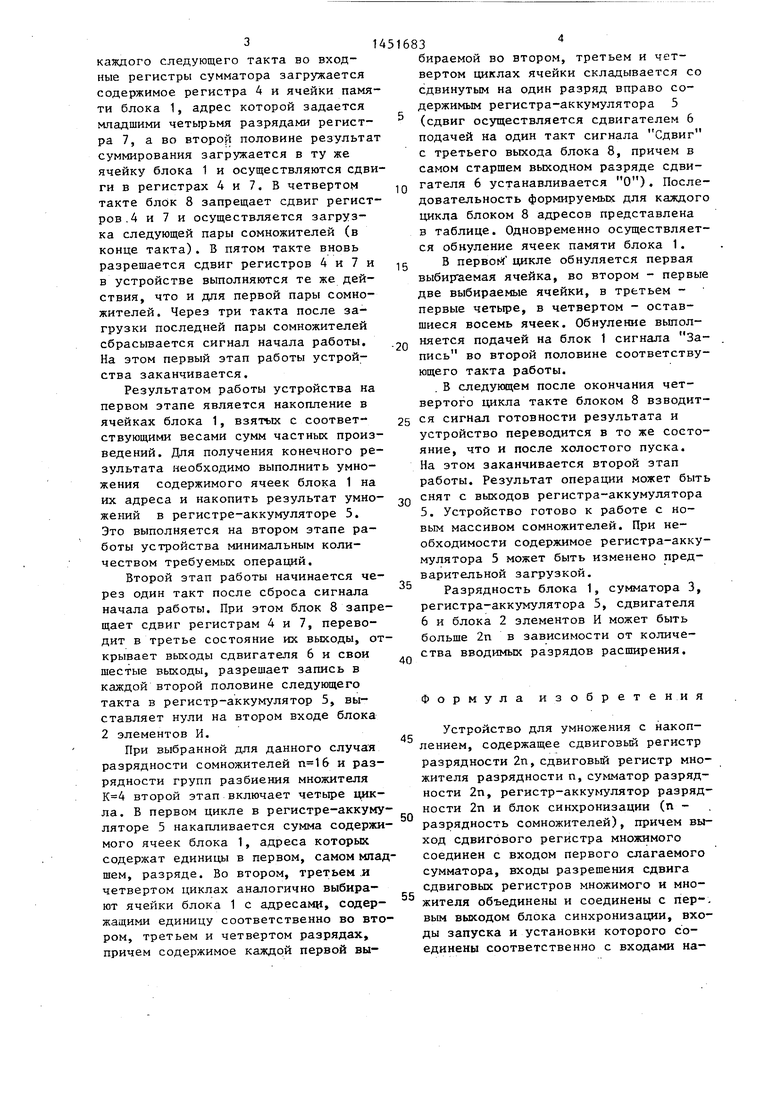

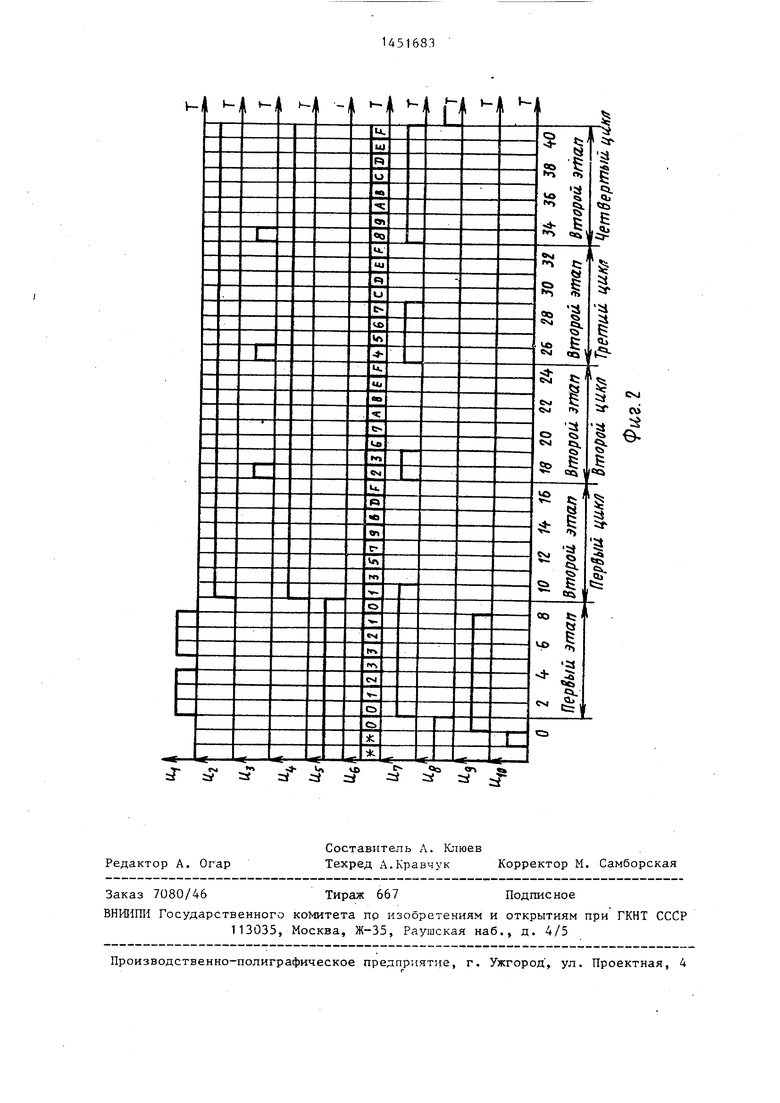

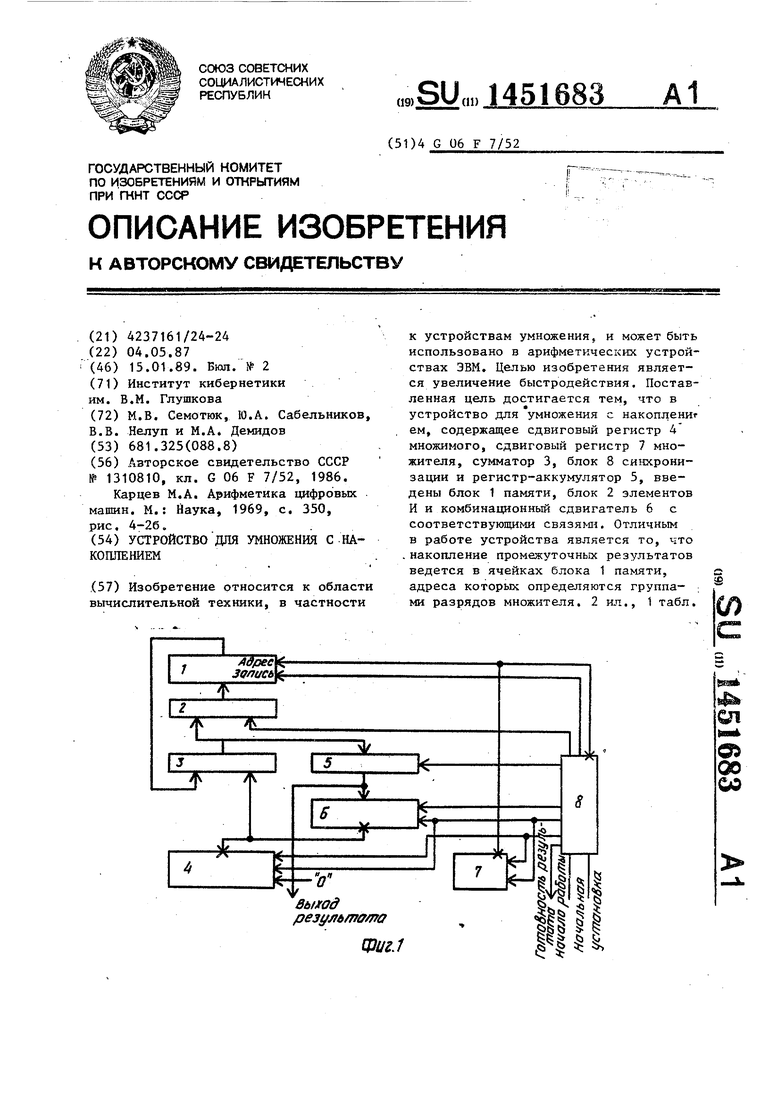

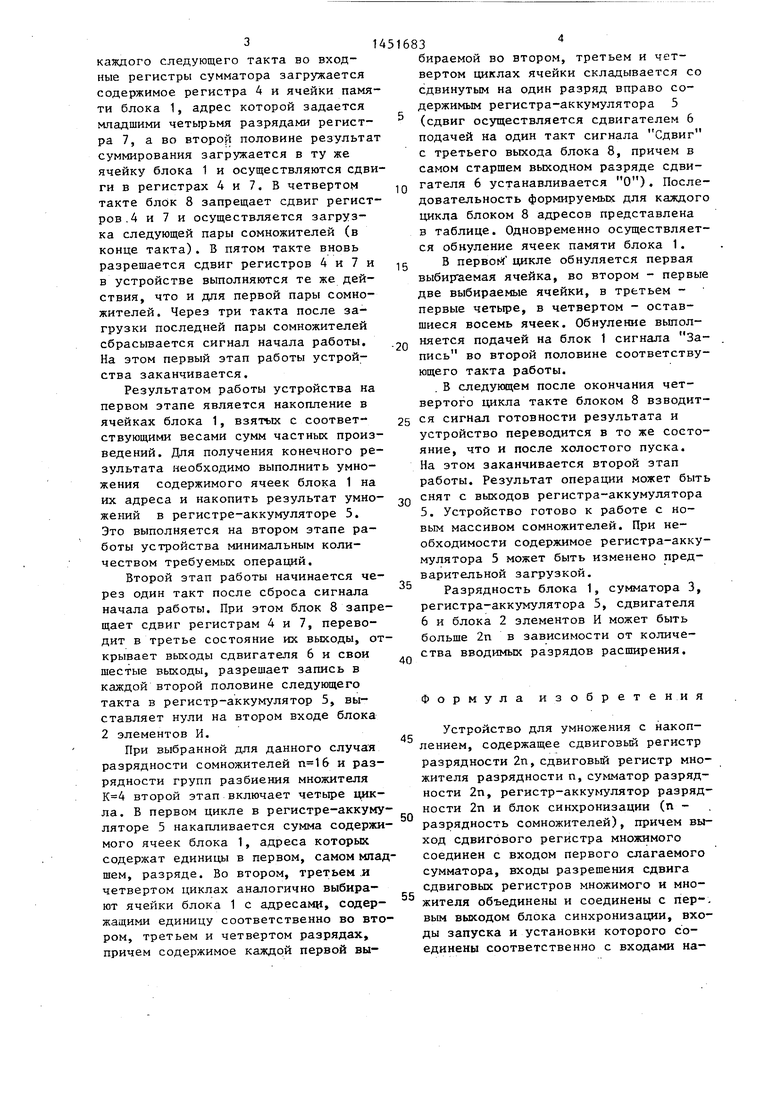

На фиг, 1 представлена схема устройства для умножения с накоплением5 на фиг. 2 - временные диаграмм: формирования сигналов в блоке синхронизации (для ).

Устройство (фиг.1) содержит блок 1 памяти, блок 2 элементов И, сумматор 3j сдвиговый регистр 4 множимого регистр-аккумулятор 5, комбинационный сдвигатель 6, сдвиговый регистр

7множителя и блок 8 синхронизации.

На фиг„2 приняты следующие обозначения: и, - сигнал на первом выходе блока 8 (подключен к входам Сдвиг регистров 4 и 7); Uч сигнал на втором выходе блока 8 (подключен к входу Запись регистра-аккумулятора 5); и 3 сигнал на третье выходе блока 8 (подключен к входу Сдвиг сдвигател я 6); U4 сигнал на четвертом выходе блока 8 (подключен к входам запрета вьщачи сдви- гателя 6 и регистров 4 и 7);. U5 сигнал на пятом выходе блока 8 (подключен к второму входу блока 2); U сигналы на шестых выходах блока 8 и на младших выходах регистра 7 (подключены к входам Адрес блока 1), отображаются на диаграмме в шестнадцатиричной системе счисления-, Vj- сигнал на седьмом выходе блока 8 (подключен к входу Запись блока 1) и - сигнал на. восьмом выходе блока

8(сигнал готовности результата устройства); Ug - сигнал на первом входе блока В (сигнал начала работы устройства) ; сигнал на втором вход блока 8 (сигнал начальной установки устройства).

Сумматор 3 может быть построен на элементе 1802 ИМ1, сдвиговьй регистр

4 множимого и сдвиговый регистр 7 множителя - на элементе 533 ИР 16, комбинированный сдвигатель 6 - на элементе. 531 КПП. Цепи общего тактирующего сигнала на фиг. 1 и 2 не показаны.

Устройство для умножения с накоплением (фиг.1) работает следующим образом.

0

5

0

5

0

5

0

5

0

Рассмотрим случай, когда разрядность сомножителей . При этом регистр 4 осуществляет сдвиг влево сразу на четьфе разряда, регистр 7 - сдвиг вправо на четыре разряда. Таким образом, множитель разбивается на четыре группы по четыре разряда . Запись множимого осуществляется в разряды с четвертого по девятнадцатый регистра 4. В остальные его разряды, загружаются нули. Выходами регистра 7 являются младшие четыре разряда (соответственно разрядности группы ). Блок 1 памяти содержит шестнадцать ячеек.

Дл5Г правильной работы устройства с целью первоначального обнуления блока 1 необходимо произвести холостой пуск устройства хотя бы для пары сомножителей. После выявления сигнала готовности результата необходимо осуществить предварительную загрузку (или обнуление) регистра-аккумулятора 5 (предварительная загрузка сопровождается сигналом начальной установки, по которому блок 8 формирует сигнал Запись на входе регистра-аккумулятора), причем разрядность числа, загружаемого в регистр- аккумулятор, должна соответствовать разрядности регистра-аккумулятора 5. Работа устройства в режиме холостого пуска не о тличается от обычной работы устройства, за исключением того, что в первом случае результат будет неверным), поэтому она в дальнейшем не рассматривается, но предполагается, что холостой пуск выполнен. После выполнения холостого пуска взведен сигнал готовности результата, сброшены сигналы Сдвиг регистров 4 и 7 и сдвигателя 6, сигнал Запись регистра-аккумулятора 5, установлен в 1 второй вход блока 2 э лементов И, сброшен сигнал Запись блока 1, установлены в третье состояние шестые выходы блока 8 и выходы сдвигателя 6, открыты выходы регистров 4 и 7.

Работа устройства начинается с момента взведения сигнала начала работы и одновременной загрузки первой пары сомножителей в регистры 4 и 7. В следующем такте изменяются следующие выходные сигналы блока 8: сбрасывается сигнал готовности результата, разрешается запись в блок 1, на три следующих такта разрешается сдвиг .регистров 4 и 7. В первой половине

каждого следующего такта во входные регистры сумматора загружается содержимое регистра 4 и ячейки памяти блока 1, адрес которой задается младшими четьфьмя разрядами регистра 7, а во второй половине результат суммирования загружается в ту же ячейку блока 1 и осуществляются сдвиги в регистрах 4 и 7. В четвертом такте блок 8 запрещает сдвиг регистров. 4 и 7 и осуществляется загрузка следующей пары сомножителей (в конце такта). В пятом такте вновь разрешается сдвиг регистров 4 и 7 и в устройстве выполняются те же действия, что и для первой пары сомножителей. Через три такта после загрузки последней пары сомножителей сбрасывается сигнал начала работы. На этом первый этап работы устройства заканчивается.

Результатом работы устройства на первом этапе является накопление в ячейках блока 1, взятых с соответствующими весами сумм частных произведений. Для получения конечного результата необходимо выполнить умножения содержимого ячеек блока 1 на их адреса и накопить результат умножений в регистре-аккумуляторе 5. Это выполняется на втором этапе работы устройства минимальным количеством требуемых операций.

Второй этап работы начинается через один такт после сброса сигнала начала работы. При этом блок 8 запрещает сдвиг регистрам 4 и 7, переводит в третье состояние их выходы, открывает выходы сдвигатепя 6 и свои шестые выходы, разрешает запись в каждой второй половине следующего такта в регистр-аккумулятор 5, выставляет нули на втором входе блока 2 элементов И.

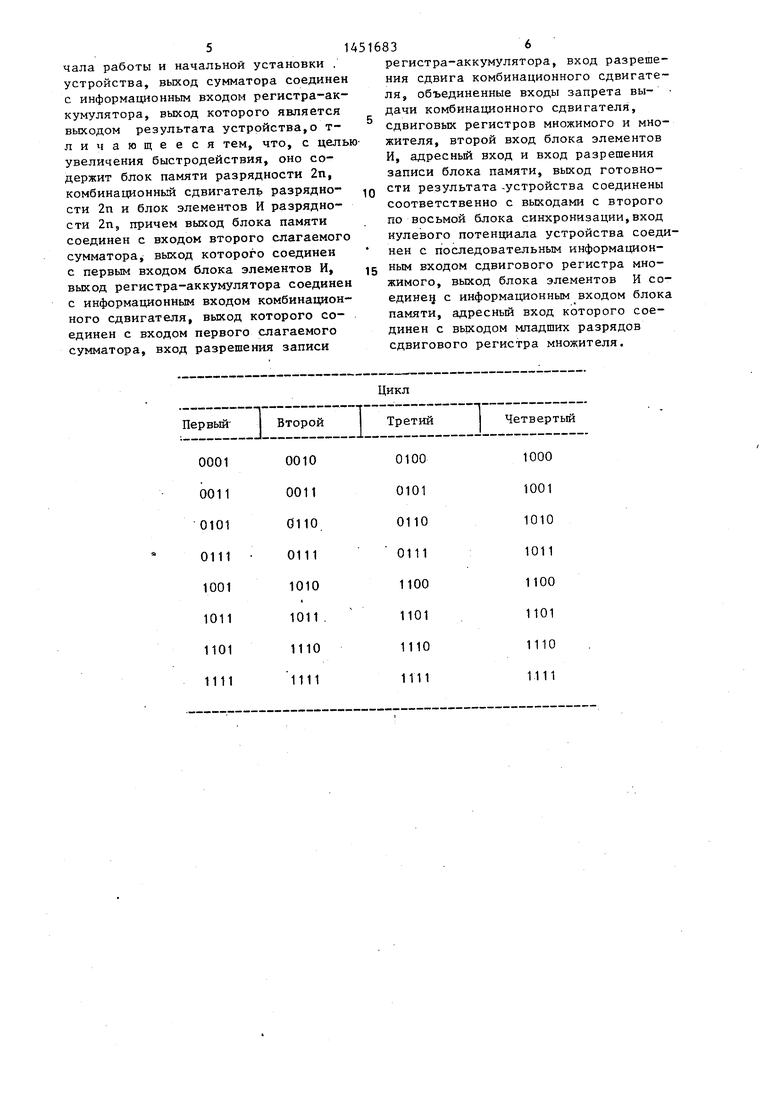

При выбранной для данного случал разрядности сомножителей и разрядности групп разбиения множителя второй этап включает четьфе цикла. В первом цикле в регистре-аккумуляторе 5 накапливается сумма содержимого ячеек блока 1, адреса которых содержат единицы в первом, самом млашем, разряде. Во втором, третьем ,и четвертом циклах аналогично выбирают ячейки блока 1 с адресами, содержащими единицу соответственно во втором, третьем и четвертом разрядах, причем содержимое каждой первой вы451683

бираемой во втором, третьем и четвертом циклах ячейки складывается со сдвинутым на один разряд вправо содержимым регистра-аккумулятора 5 (сдвиг осуществляется сдвигателем 6

10

15

подачей на один такт сигнала Сдвиг с третьего выхода блока 8, причем в самом старшем выходном разряде сдви- гателя 6 устанавливается О). Последовательность формируемых для каждого цикла блоком 8 адресов представлена в таблице. Одновременно осуществляется обнуление ячеек памяти блока 1.

В nepsoNf цикле обнуляется первая выбир аемая ячейка, во втором - первые две выбираемые ячейки, в третьем - первые четыре, в четвертом - оставшиеся восемь ячеек. Обнуление выполняется подачей на блок 1 сигнала Запись во второй половине соответствующего такта работы.

В следующем после окончания четвертого цикла такте блоком 8 взводит- 25 ся сигнал готовности результата и

устройство переводится в то же состояние, что и после холостого пуска. На этом заканчивается второй этап работы. Результат операции может быть снят с выходов регистра-аккумулятора 5. Устройство готово к работе с новым массивом сомножителей. При необходимости содержимое регистра-аккумулятора 5 может быть изменено предварительной загрузкой.

Разрядность блока 1, сумматора 3, регистра-аккумулятора 5, сдвигателя 6 и блока 2 элементов И может быть больше 2п в зависимости от количества вводимых разрядов расширения.

30

35

40

Формула изобретения

Устройство для умножения с накопением, содержащее сдвиговый регистр разрядности 2п, сдвиговьй регистр множителя разрядности п, сумматор разрядности 2п, регистр-аккумулятор разрядности 2п и блок синхронизации (п - разрядность сомножителей), причем выход сдвигового регистра множимого соединен с входом первого слагаемого сумматора, входы разрешения сдвига сдвиговых регистров множимого и множителя объединены и соединены с пер-, вым выходом блока синхронизации, входы запуска и установки которого соединены соответственно с входами на-

чала работы и начальной установки . устройства, выход сумматора соединен с информационным входом регистра-аккумулятора, выход которого является выходом результата устройства,о т- ли чающееся тем, что, с целью увеличения быстродействия, оно содержит блок памяти разрядности 2п, комбинационный сдвигатель разрядности 2п и блок элементов И разрядности 2п, причем выход блока памяти соединен с входом второго слагаемого сумматора выход которого соединен с первьм входом блока элементов И, выход регистра-аккумулятора соединен с информационным входом комбинационного сдвигателя, выход которого соединен с входом первого слагаемого сумматора, вход разрешения записи

5

регистра-аккумулятора, вход разрешения сдвига комбинационного сдвигателя, объединенные входы запрета вы- дачи комбинационного сдвигателя, сдвиговых регистров множимого и множителя, второй вход блока элементов И, адресный вход и вход разрешения записи блока памяти, выход готовности результата -устройства соединены соответственно с выходами с второго по восьмой блока синхронизации,вход нулевого потенциала устройства соединен с последовательным информационным входом сдвигового регистра множимого, выход блока элементов И со- единец с информационным входом блока памяти, адресный вход которого соединен с вькодом младших разрядов сдвигового регистра множителя.

CSJ

cv :i

e.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения с накоплением комплексных чисел | 1987 |

|

SU1478211A1 |

| Устройство для умножения с накоплением | 1988 |

|

SU1509876A1 |

| Устройство для умножения с накоплением комплексных чисел | 1988 |

|

SU1587230A1 |

| Устройство для умножения | 1985 |

|

SU1254473A1 |

| Вычислительная ячейка | 1985 |

|

SU1287145A1 |

| Устройство для умножения @ - разрядных чисел | 1989 |

|

SU1735843A1 |

| Устройство для умножения двоичных чисел | 1989 |

|

SU1784973A1 |

| Устройство для умножения чисел | 1988 |

|

SU1575173A1 |

| Устройство для умножения | 1988 |

|

SU1654814A2 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

Изобретение относится к области вычислительной техники, в частности к устройствам умножения, и может быть использовано в арифметических устройствах ЭВМ. Целью изобретения является увеличение быстродействия. Поставленная цель достигается тем, что в устройство для умножения с накоплениг ем, содержащее сдвиговый регистр 4 множимого, сдвиговый регистр 7 множителя, сумматор 3, блок 8 синхронизации и регистр-аккумулятор 5, введены блок 1 памяти, блок 2 элементов И и комбинационный сдвигатель 6 с соответствующими связями. Отличным в работе устройства является то, что .накопление промежуточных результатов ведется в ячейках блока 1 памяти, адреса которых определяются группа- ; ми разрядов множителя. 2 ил., 1 табл. €

| Устройство для умножения с накоплением | 1986 |

|

SU1310810A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Карцев М.А | |||

| Арифметика цифровых машин | |||

| М.: Наука, 1969, с | |||

| Способ приготовления консистентных мазей | 1912 |

|

SU350A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-01-15—Публикация

1987-05-04—Подача