Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств на основе элементов полупроводниковой динамической памяти..

Цель изобретения - повышение быстродействия устройства.

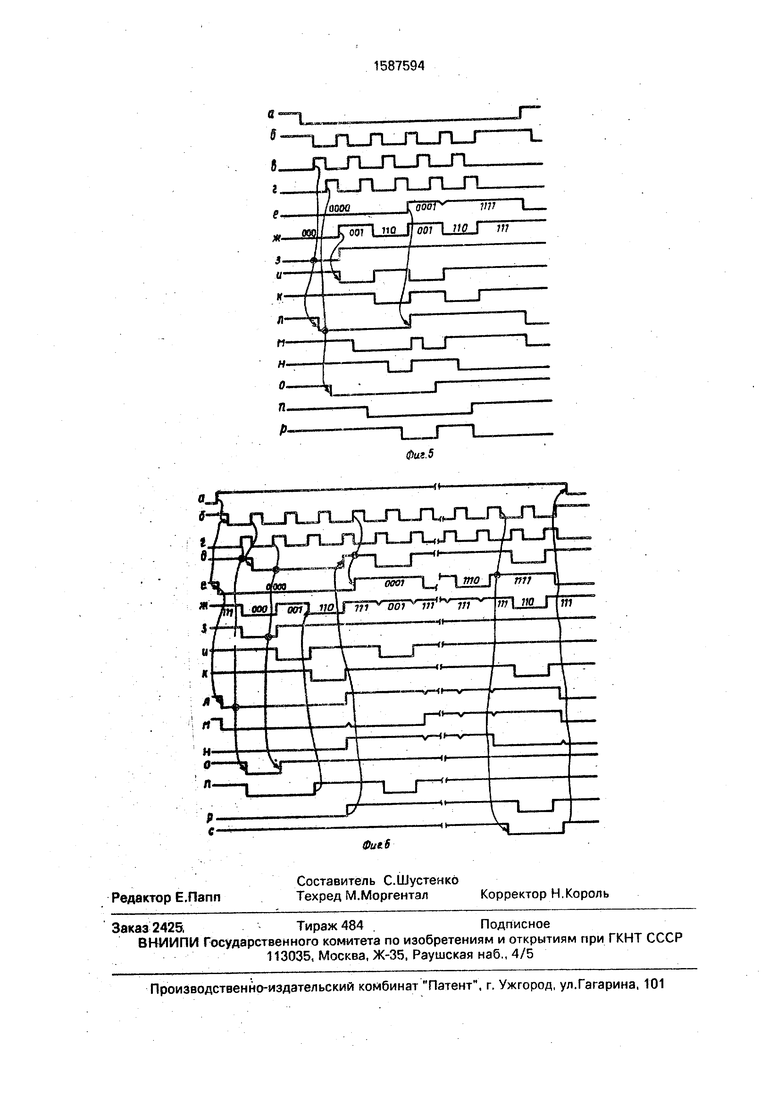

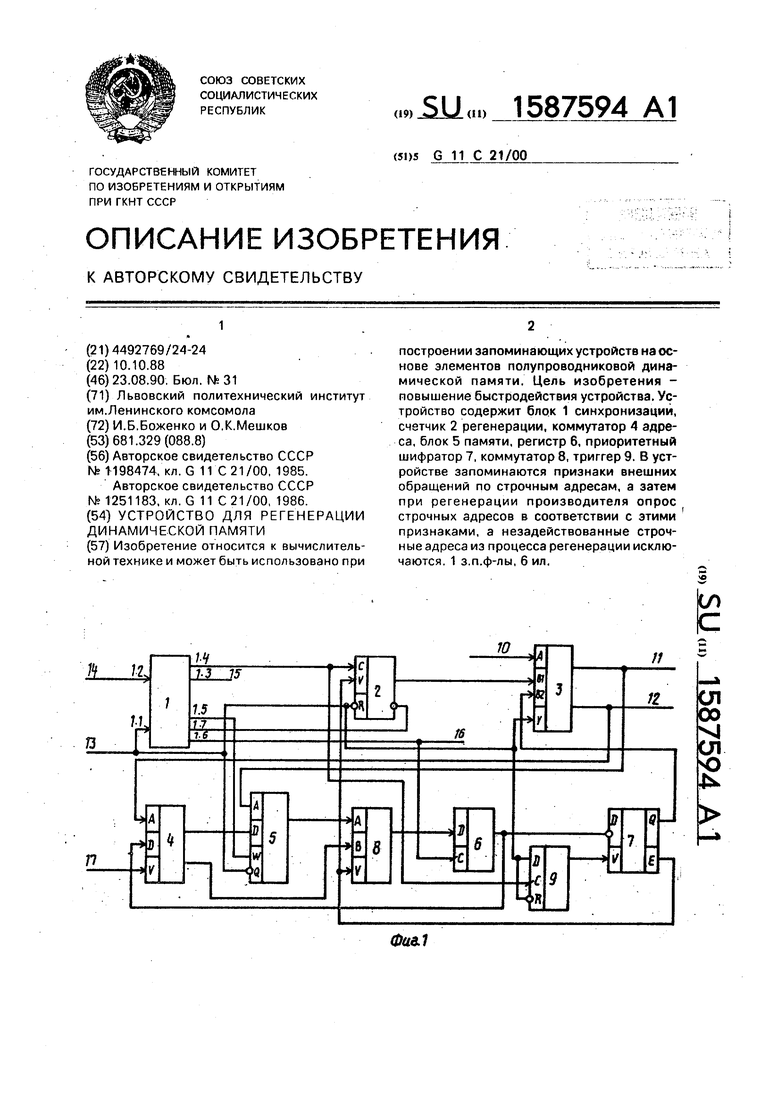

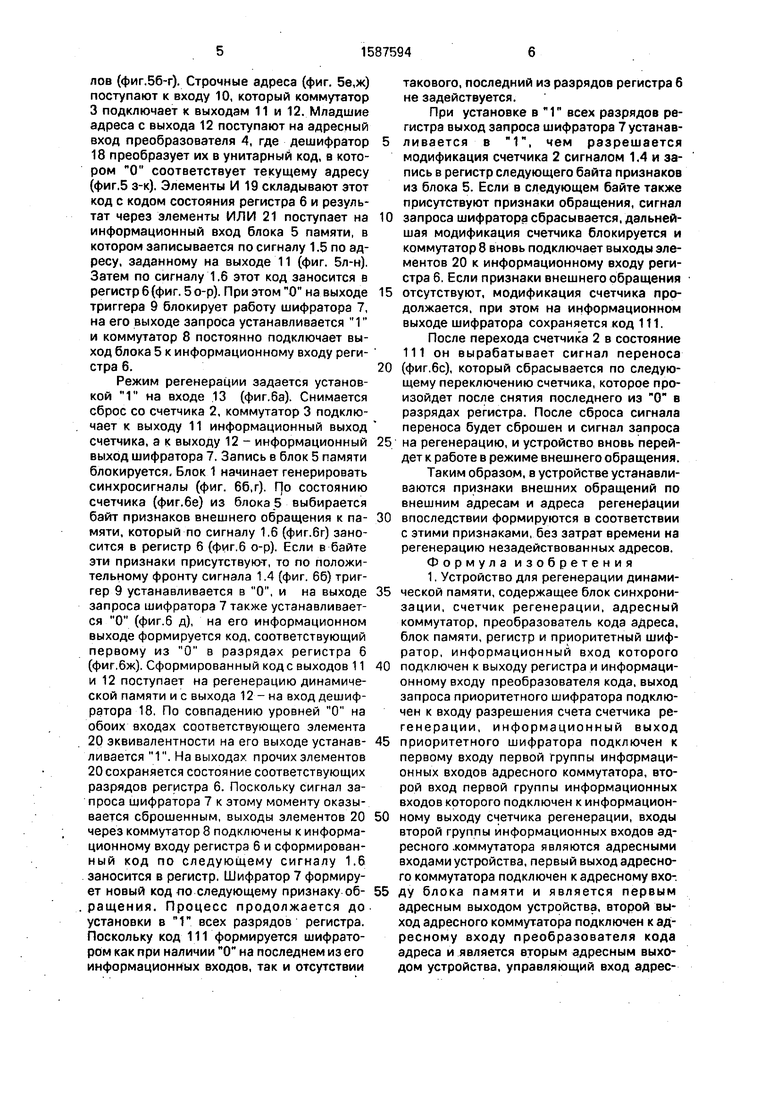

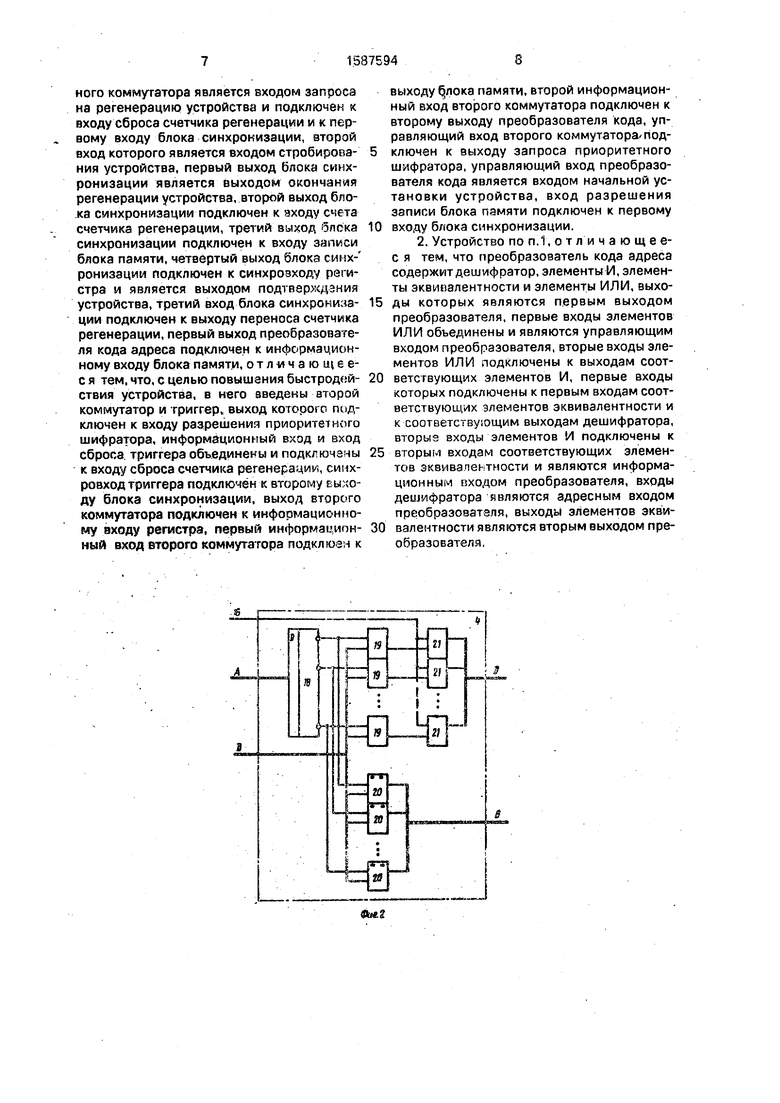

На фиг. 1 представлена функциональная схема устройства: на фиг, 2 - функциональная схема преобразователя кода адреса; на фиг. 3 - функциональная схема блока синхронизации; на фиг. 4 - временная диаграмма работы устройства; на фиг. 5 и 6 - временные диаграммы работы устройства в режимах внешнего обращения и регенерации соответственно.

Устройство (фиг.1) содержит блок 1 синхронизации, счетчик 2 регенерации, адресный коммутатор 3, преобразователь 4 кода адреса, блок 5 памяти, регистр 6, приоритетный шифратор 7, второй коммутатор 8, триггер 9, адресный вход 10, первый 11 и второй 12 адресные выходы, вход 13 запроса на регенерацию, стробирующий вход 14, выход 15 окончания регенерации, выход 16 стробирования и вход 17 начальной установки.

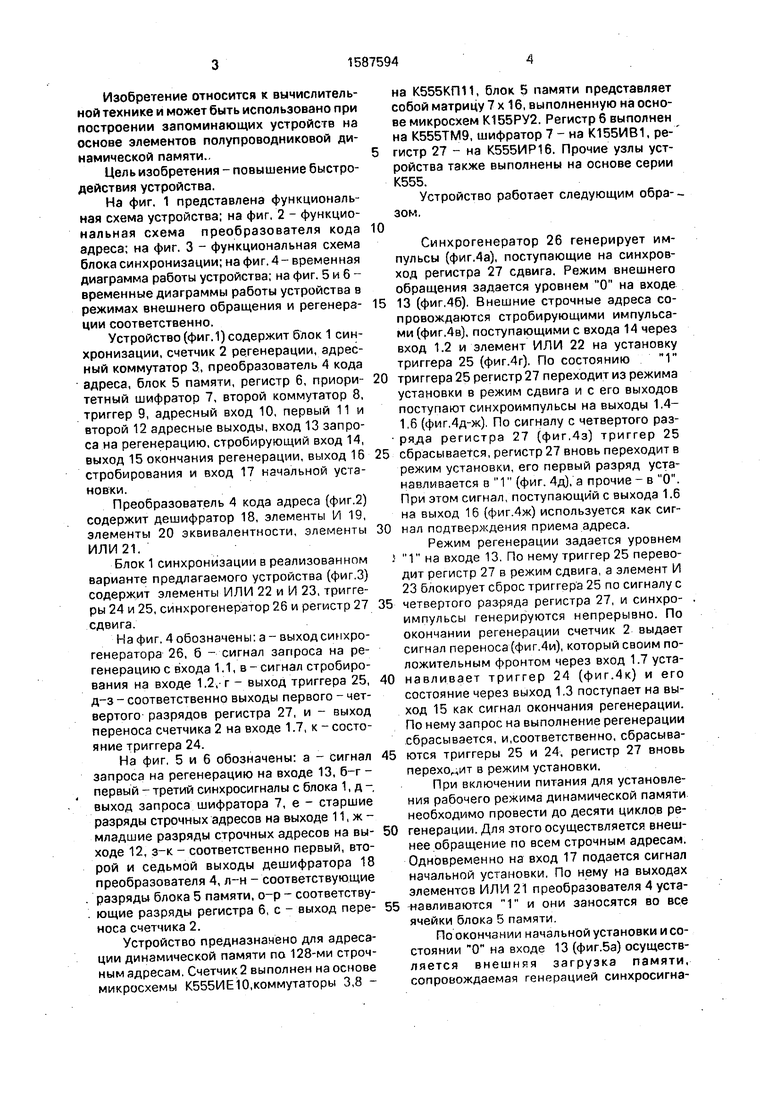

Преобразователь 4 кода адреса (фиг.2) содержит дешифратор 18, элементы И 19, элементы 20 эквивалентности, элементы

ИЛИ 21.

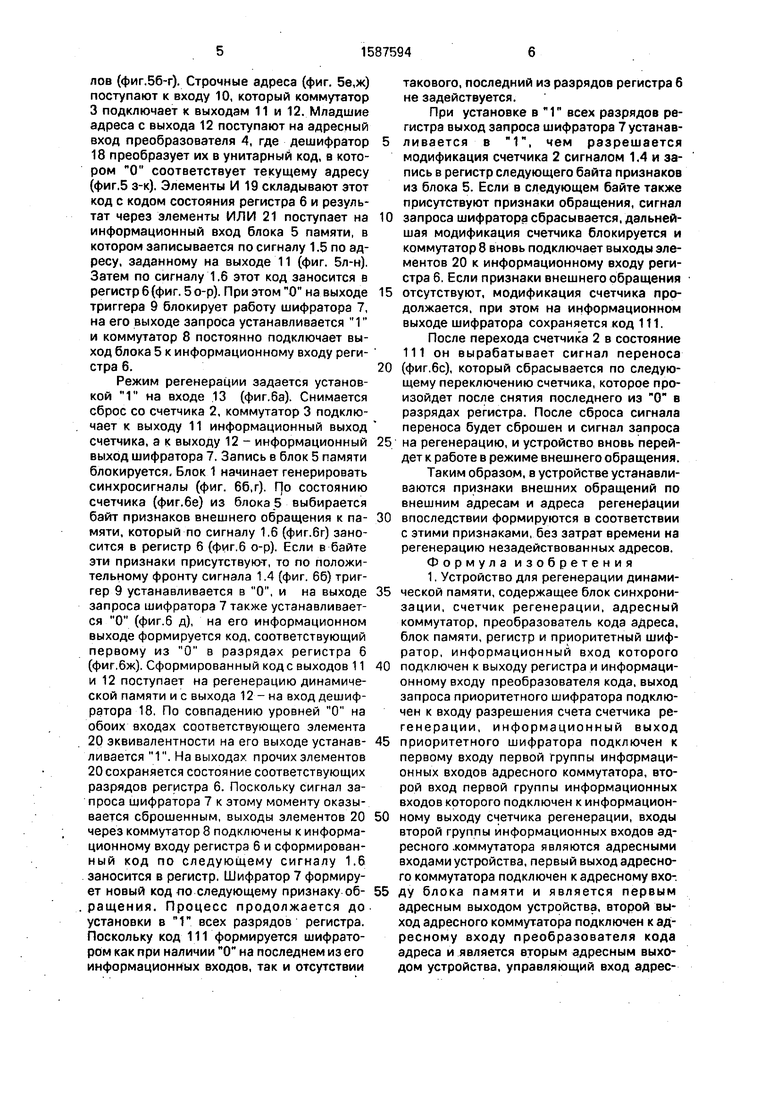

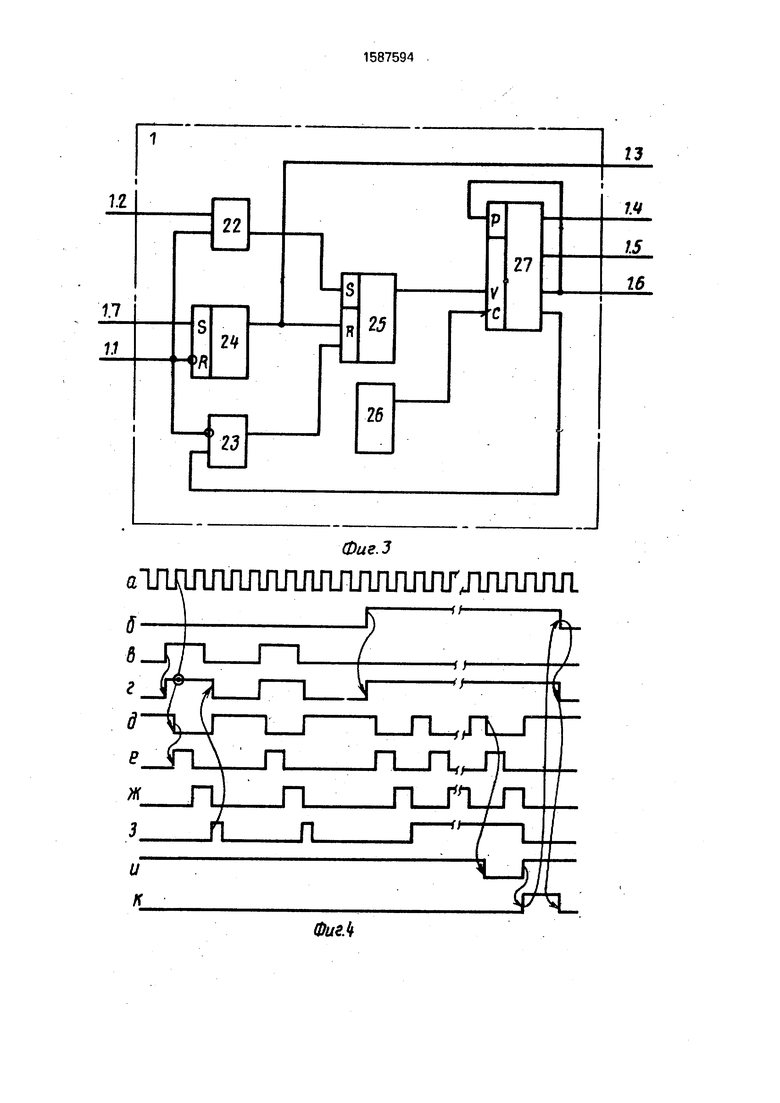

Блок 1 синхронизации в реализованном варианте предлагаемого устройства (фиг.З) содержит элементы ИЛИ 22 и И 23, триггеры 24 и 25, синхрогенератор 26 и регистр 27 сдвига.

На фиг. 4 обозначены; а - выход синхро- генератора 26, б - сигнал запроса на регенерацию с входа 1.1, в - сигнал стробирования на входе 1.2, г - выход триггера 25, д-з - соответственно выходы первого - четвертого разрядов регистра 27, и - выход переноса счетчика 2 на входе 1.7, к - состояние триггера 24.

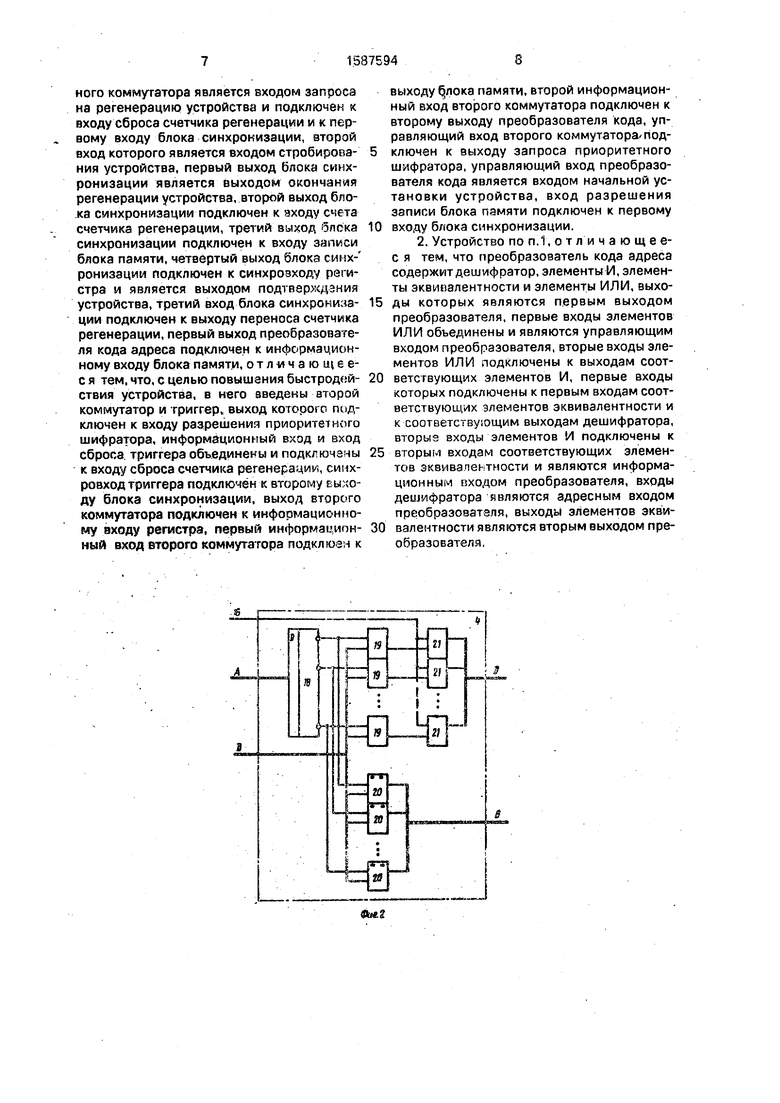

На фиг, 5 и 6 обозначены; а - сигнал запроса на регенерацию на входе 13, б-г - первый - третий синхросигналы с блока 1, д - выход запроса шифратора 7, е - старшие разряды строчных адресов на выходе 11, ж - младшие разряды строчных адресов на выходе 12, з-к - соответственно первый, второй и седьмой выходы дешифратора 18 преобразователя 4, л-н - соответствующие разряды блока 5 памяти, о-р - соответству- . ющие разряды регистра 6, с - выход переноса счетчика 2.

Устройство предназначено для адресации динамической памяти по 128-ми строчным адресам. Счетчик 2 выполнен на основе микросхемы К555ИЕ10,коммутаторы 3,8 на К555КП11, блок 5 памяти представляет собой матрицу 7x16, выполненную на основе микросхем К155РУ2. Регистре выполнен на К555ТМ9, шифратор 7 - на К155ИВ1, ре- гистр 27 - на К555ИР16. Прочие узлы устройства также выполнены на основе серии

К555

Устройство работает следующим обра- зом,

0

Синхрогенератор 26 генерирует импульсы (фиг,4а), поступающие на синхров- ход регистра 27 сдвига. Режим внешнего обращения задается уровнем О на входе 5 13 (фиг,46), Внешние строчные адреса сопровождаются стробирующими импульсами (фиг.4в), поступающими с входа 14 через вход 1.2 и элемент ИЛИ 22 на установку триггера 25 (фиг.4г). По состоянию 1 0 триггера 25 регистр 27 переходит из режима установки в режим сдвига и с его выходов поступают синхроимпульсы на выходы 1,4- 1,6 (фиг,4д-ж). По сигналу с четвертого раз- ряда регистра 27 (фиг,4з) триггер 25 5 сбрасывается, регистр 27 вновь переходит в режим установки, его первый разряд навлмвается в 1 (фиг. 4д), а прочие- в О. При этом сигнал, поступающий с выхода 1.6 на выход 16 (фиг.4ж) используется как сиг- 30 нал подтверждения приема адреса.

Режим регенерации задается уровнем } 1 на входе 13, По нему триггер 25 переводит регистр 27 в режим сдвига, а элемент И 23 блокирует сброс триггера 25 по сигналу с 35 четвертого разряда регистра 27, и синхроимпульсы генерируются непрерывно. По окончании регенерации счетчик 2 выдает сигнал переноса (фиг,4и), который своим положительным фронтом через вход 1.7 уста- 40 навливает триггер 24 (фиг.4к) и его состояние через выход 1,3 поступает на выход 15 как сигнал окончания регенерации. По нему запрос на выполнение регенерации .сбрасывается, и,соответственно, сбрасыва- 45 ются триггеры 25 и 24, регистр 27 вновь переходит в режим установки.

При включении питания для установления рабочего режима динамической памяти необходимо провести до десяти циклов ре- 50 генерации. Для этого осуществляется внешнее обращение по всем строчным адресам. Одновременно на вход 17 подается сигнал начальной установки. По нему на выходах элементов ИЛИ 21 преобразователя 4 уста- 55 разливаются 1 и они заносятся во все

ячейки блока 5 памяти,

По окончании начальной установки и состоянии О на входе 13 (фиг.5а) осуществляется внешняя загрузка памяти, сопровождаемая генерацией синхросигналов (фиг.5б-г). Строчные адреса (фиг, 5е,ж) поступают к входу 10, который коммутатор 3 подключает к выходам 11 и 12. Младшие адреса с выхода 12 поступают на адресный вход преобразователя 4, где дешифратор 18 преобразует их в унитарный код, в котором О соответствует текущему адресу (фиг.5 з-к). Элементы И 19 складывают этот код с кодом состояния регистра 6 и результат через элементы ИЛИ 21 поступает на информационный вход блока 5 памяти, в котором записывается по сигналу 1.5 по адресу, заданному на выходе 11 (фиг. 5л-н). Затем по сигналу 1.6 этот код заносится в регистр 6(фиг. 5 о-р). При этом О на выходе триггера 9 блокирует работу шифратора 7, на его выходе запроса устанавливается 1 и коммутатор 8 постоянно подключает выход блока 5 к информационному входу реги- стра 6.

Режим регенерации задается установкой 1 на входе 13 (фиг.ба). Снимается сброс со счетчика 2, коммутатор 3 подключает к выходу 11 информационный выход счетчика, а к выходу 12 - информационный выход шифратора 7. Запись в блок 5 памяти блокируется. Блок 1 начинает генерировать синхросигналы (фиг. 66,г). По состоянию счетчика (фиг.бе) из блока 5 выбирается байт признаков внешнего обращения к па- мяти, который по сигналу 1.6 (фиг.бг) заносится в регистр 6 (фиг.6 о-р). Если в байте эти признаки присутствуют, то по положительному фронту сигнала 1.4 (фиг. 66) триггер 9 устанавливается в О, и на выходе запроса шифратора 7 также устанавливается О (фиг.6 д), на его информационном выходе формируется код. соответствующий первому из О в разрядах регистра 6 (фиг.бж). Сформированный код с выходов 11 и 12 поступает на регенерацию динамической памяти и с выхода 12- на вход дешифратора 18. По совпадению уровней О на обоих входах соответствующего элемента 20 эквивалентности на его выходе устанав- ливается 1. На выходах прочих элементов 20 сохраняется состояние соответствующих разрядов регистра 6. Поскольку сигнал запроса шифратора 7 к этому моменту оказывается сброшенным, выходы элементов 20 через коммутатор 8 подключены к информационному входу регистра 6 и сформирован- ный код по следующему сигналу 1.6 заносится в регистр. Шифратор 7 формирует новый код по следующему признаку об- ращения. Процесс продолжается до установки в 1 всех разрядов регистра. Поскольку код 111 формируется шифратором как при наличии О на последнем из его информационных входов, так и отсутствии

такового, последний из разрядов регистра 6 не задействуется.

При установке в 1 всех разрядов регистра выход запроса шифратора 7 устанавливается в 1, чем разрешается модификация счетчика 2 сигналом 1.4 и запись в регистр следующего байта признаков из блока 5. Если в следующем байте также присутствуют признаки обращения, сигнал запроса шифратора сбрасывается, дальнейшая модификация счетчика блокируется и коммутатор 8 вновь подключает выходы элементов 20 к информационному входу регистра 6. Если признаки внешнего обращения отсутствуют, модификация счетчика продолжается, при этом на информационном выходе шифратора сохраняется код 111.

После перехода счетчика 2 в состояние 111 он вырабатывает сигнал переноса (фиг.бе), который сбрасывается по следующему переключению счетчика, которое произойдет после снятия последнего иэ О в разрядах регистра. После сброса сигнала переноса будет сброшен и сигнал запроса на регенерацию, и устройство вновь перейдет к работе в режиме внешнего обращения.

Таким образом, в устройстве устанавливаются признаки внешних обращений по внешним адресам и адреса регенерации впоследствии формируются в соответствии с этими признаками, без затрат времени на регенерацию незадействованных адресов.

Формула изобретения

1. Устройство для регенерации динамической памяти, содержащее блок синхронизации, счетчик регенерации, адресный коммутатор, преобразователь кода адреса, блок памяти, регистр и приоритетный шифратор, информационный вход которого подключен к выходу регистра и информационному входу преобразователя кода, выход запроса приоритетного шифратора подключен к входу разрешения счета счетчика регенерации, информационный выход приоритетного шифратора подключен к первому входу первой группы информационных входов адресного коммутатора, второй вход первой группы информационных входов которого подключен к информационному выходу счетчика регенерации, входы второй группы информационных входов адресного .коммутатора являются адресными входами устройства, первый выход адресного коммутатора подключен к адресному вхо-. ду блока памяти и является первым адресным выходом устройства, второй выход адресного коммутатора подключен к адресному входу преобразователя кода адреса и является вторым адресным выходом устройства, управляющий вход адреснот коммутатора является входом запроса на регенерацию устройства и подключен к входу сброса счетчика регенерации и к первому входу блока синхронизации, второй вход которого является входом стробирова- ния устройства, первый выход блока синхронизации является выходом окончания регенерации устройства, второй выход бло- .ка синхронизации подключен к входу счета счетчика регенерации, третий выход бпЬка синхронизации подключен к входу записи блока памяти, четвертый выход блока синх- ронизации подключен к синхрозходу регистра и является выходом подтверждэния устройства, третий вход блока синхронизации подключен к выходу переноса счетчика регенерации, первый выход преобразователя кода адреса подключен к информационному входу блока памяти, отличаю щее- с я тем, что, с целью повышения быстродействия устройства, в него введены второй коммутатор и триггер,, выход которого подключен к входу разрешения приоритетного шифратора, информационный вход и вход сброса, триггера объединены и подключены к входу сброса счетчика регенерации, синх- ровход триггера подключён к второму выходу блока синхронизации, выход второго коммутатора подключен к информационному входу регистра, первый информационный вход второго коммутатора подклюэн к

выходу лока памяти, второй информационный вход вто|эого коммутатора подключен к второму выходу преобразователя кода, управляющий вход второго коммутаторахподключен к выходу запроса приоритетного шифратора, управляющий вход преобразователя кода является входом начальной установки устройства, вход разрешения записи блока памяти подключен к первому

входу блока синхронизации.

2. Устройство по П.1, о т л и ч а ю щ е е- с я тем, что преобразователь кода адреса содержит дешифратор, злементыИ, злемен- ты эквивалентности и злементы ИЛИ, выходы которых являются первым выходом преобразователя, первые входы злементов ИЛИ объединены и являются управляющим входом преобразователя, вторые входы зле- ментов ИЛИ подключены к выходам соответствующих элементов И, первые входы которых подключены к первым входам соот- ветствующ их элементов эквивалентности и к соответствующим выходам дешифратора, вторыэ входы элементов И подключены к

вторым входам соответствующих злементов эквивалентности и являются информационным входом преобразователя, входы дешифратора являются адресным входом преобразоваталя, выходы злементов зквивалентности являются вторым выходом преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования адресов регенерации динамической памяти | 1989 |

|

SU1709394A1 |

| Устройство для управления регенерацией информации в динамической памяти | 1985 |

|

SU1251183A1 |

| Устройство для управления регенерацией информации в динамической памяти | 1986 |

|

SU1388945A1 |

| Устройство для управления регенерацией динамической памяти со свободными зонами | 1990 |

|

SU1739388A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для управления регенерацией динамической памяти со свободными зонами | 1990 |

|

SU1762320A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1986 |

|

SU1403091A1 |

| Устройство для преобразования малокадрового телевизионного стандарта | 1985 |

|

SU1256245A1 |

| Устройство прерываний микропроцессорной системы | 1988 |

|

SU1621030A1 |

| Устройство для сортировки данных | 1990 |

|

SU1784967A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств на основе элементов полупроводниковой динамической памяти. Цель изобретения - повышение быстродействия устройства. Устройство содержит блок 1 синхронизации, счетчик 2 регенерации, коммутатор 4 адреса, блок 5 памяти, регистр 6, приоритетный шифратор 7, коммутатор 8, триггер 9. В устройстве запоминаются признаки внешних обращений по строчным адресам, а затем при регенерации производителя опрос строчных адресов в соответствии с этими признаками, а незадействованные строчные адреса из процесса регенерации исключаются. 1 з.п. ф-лы, 6 ил.

Фиг.З

а ЯПЛЛЛЛПЛЛЯЛЛШШЛГЛЛЛЛПП

ФигЛ

| ТЕЯЛ I | 0 |

|

SU198474A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для управления регенерацией информации в динамической памяти | 1985 |

|

SU1251183A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-08-23—Публикация

1988-10-10—Подача