100 00 00

о 4 ел

cpue.i

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств на основе элементов полупроводниковой динамической памяти.

Цель изобретения - повышение быстродействия устройства.

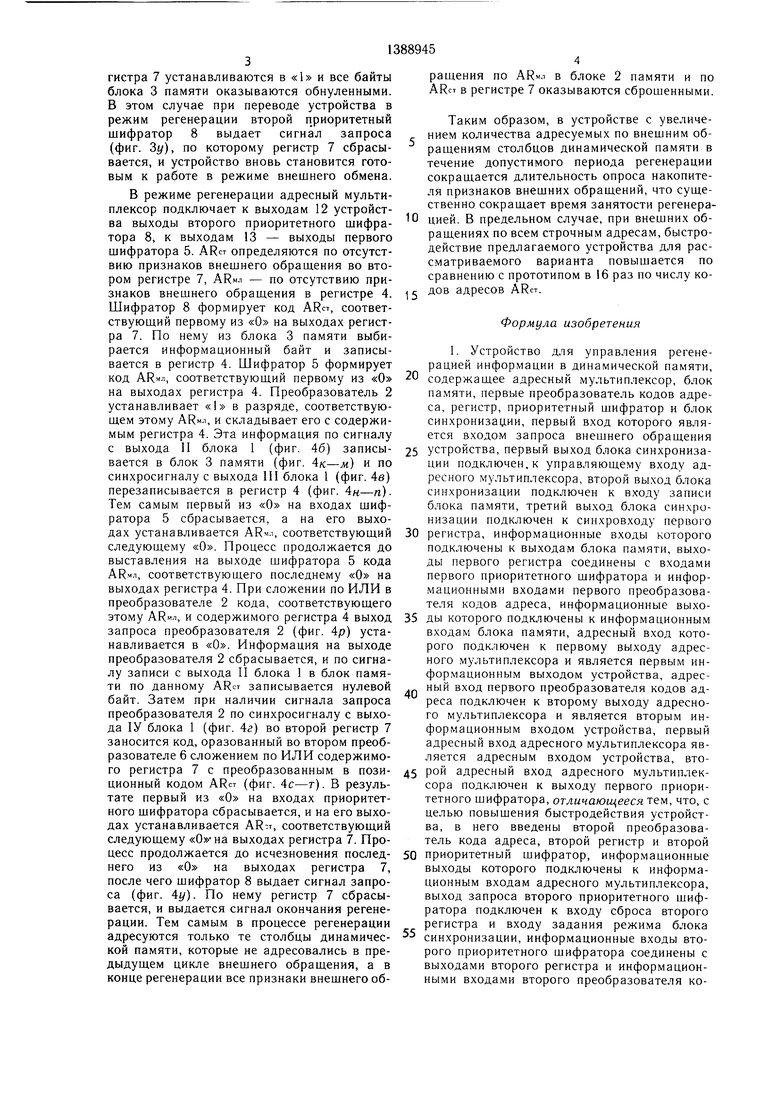

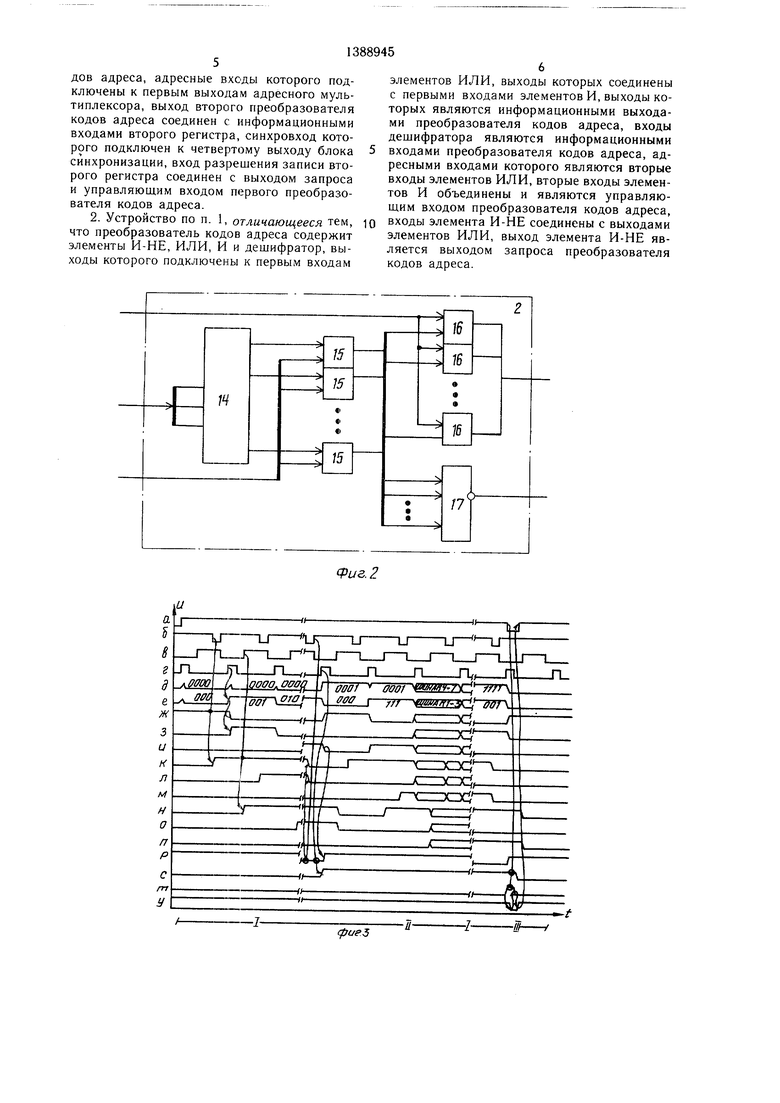

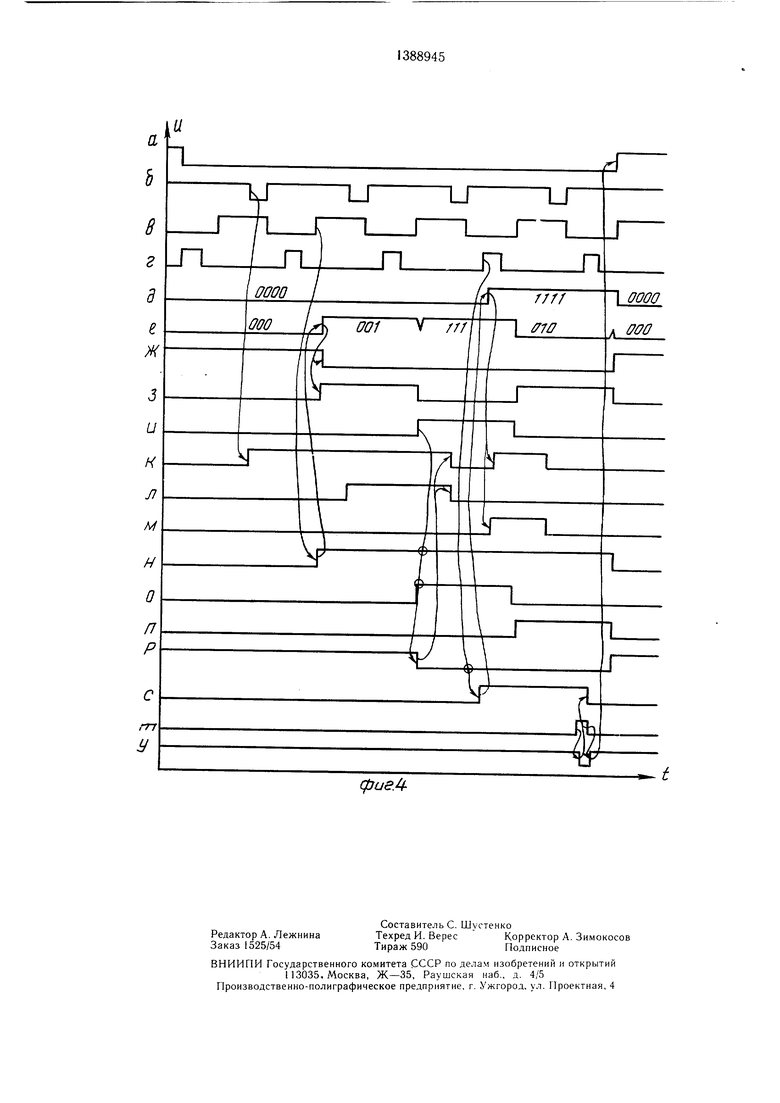

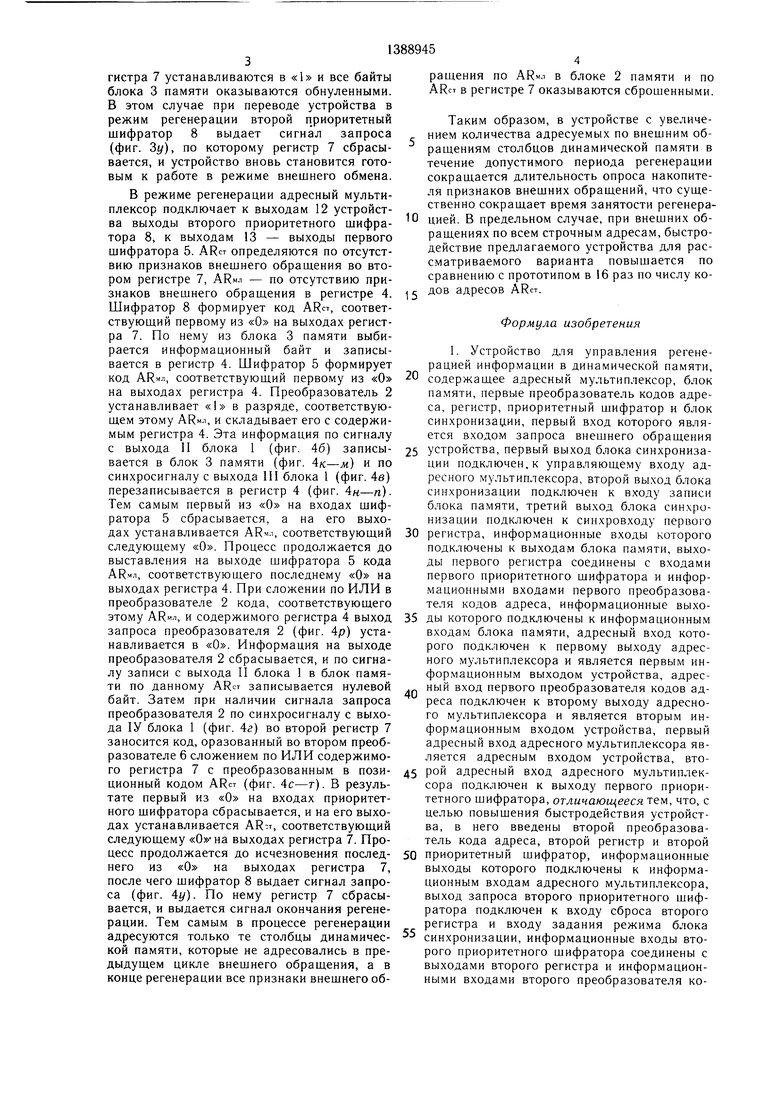

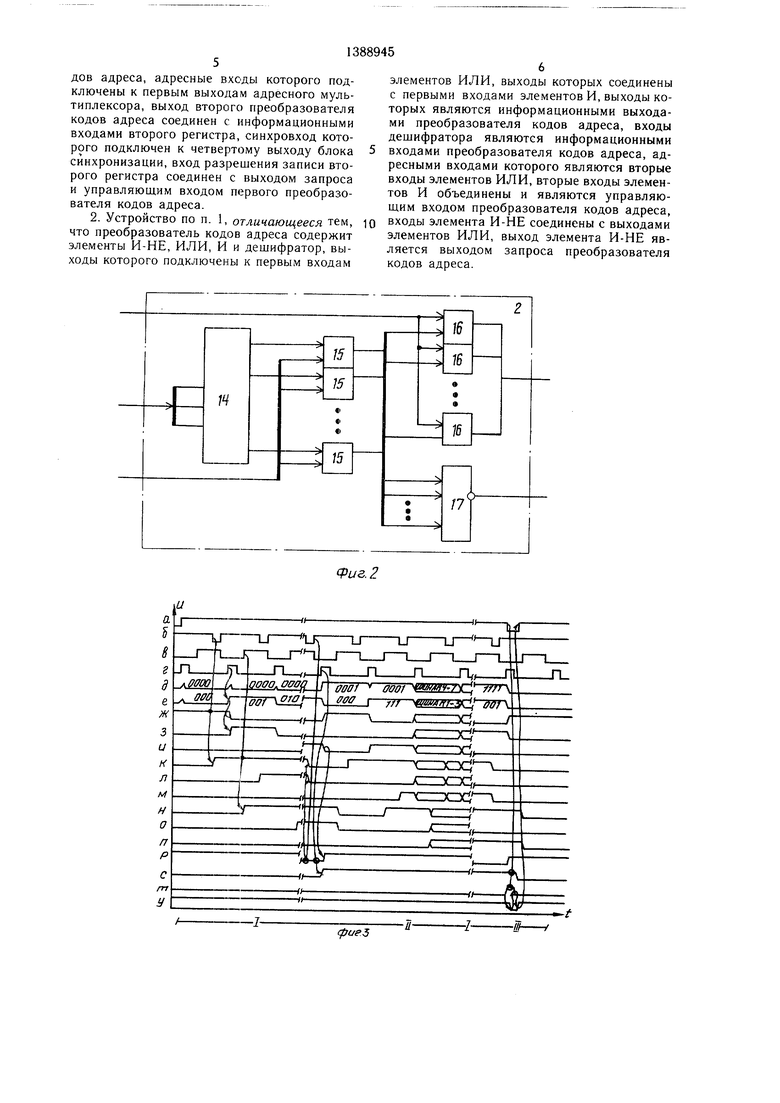

На фиг. 1 изображена функциональная схема предлагаемого устройства; на фиг. 2 - функциональная схема преобразователя кодов адреса; на фиг. 3 и 4 - временные диаграммы работы устройства в режимах внешнего обращения и регенерации соответственно.

Устройство содержит (фиг. 1) блок 1 синхронизации, первый преобразователь 2 кодов адреса, блок 3 памяти, первые регистр 4 и приоритетный шифратор 5, вторые преобразователь 6, регистр 7 и шифратор 8, а также адресный мультиплексор 9, управляющий 10 и адресный 11 входы устройства и информационные выходы 12 и 13 устройства.

Преобразователь 2 кодов адреса (фиг. 2) содержит дешифратор 14, элементы ИЛИ 15, И 16 и элемент И-НЕ 17. Входы дешифратора 14 являются адресными входами преобразователя, вторые входы элементов ИЛИ 15 - адресными входами, вторые входы элементов И 16 - управляющий вход преобразователя. Выходы элементов И 16 являются информационным выходом преобразователя, выход элемента И-НЕ является выходом запроса преобразователя. Выходы дешифратора 14 соединены с первыми входами элементов ИЛИ 15, выходы которых соединены с первыми входами элементов И и входами элементов И-НЕ.

На фиг. 3 и 4 обозначены: а-г - выходы блока 1 синхронизации; д-е - младшие разряды соответственно выходов 12 и 13 устройства; ж-и - соответственно выходы первого, второго и восьмого разрядов дешифратора 14 преобразователя 2; к-м - соответственно выходы первого, второго и восьмого разрядов блока 3 памяти; н-п - выходы первого, второго и восьмого разрядов первого регистра 4; р - выход запроса преобразователя 2; с-т - выходы первого и шестнадцатого разрядов второго регистра 7; у - выход запроса второго приоритетного шифратора 8.

По входу 10 поступают сигналы запроса внешнего обращения, тактирования, начала и конца регенерации, по входу 11 - строчные адреса внешнего обращения. С выходов 12 задаются старщие разряды строчных адресов динамической памяти, с выходов 13 - младшие.

Устройство реализовано для управления адресацией динамической памяти, в которой для регенерации опрашиваются 128 столбцов по семи разрядам строчных адресов. В качестве ARcT приняты разряды AR 7-4, в качестве ARw.i-AR3-1. Первый преобразоваo

0

5

0

5

0

5

0

5

тель 2 реализован как преобразователь трехразрядного двоичного в восьмиразрядный позиционный код, блок 3 памяти - как матрица 8x16, первый приоритетный шифратор - как преобразователь восьмиразрядного позиционного в трехразрядный двоичный код, вторые преобразователь 6 и шифратор 8 - соответственно как преобразователи 4-16 и 16-4.

Устройство работает следующим образом.

Режим внешнего обращения задается уровнем «1 с выхода I блока 1 синхронизации (фиг. За). Строчные адреса (фиг. 3d, е) поступают синхронно с сигналами с выхода 1У блока 1 (фиг. Зг). Адресный мультиплексор 9 подключает к выходам 12 устройства сигналы ARcr, к выходам 13 - ARM.1, поступающие по адресному входу 11. По ARcT из обнуленного в течение цикла регенерации блока 3 памяти выбирается байт, заносящийся по сигналу с выхода И блока I (фиг. Зв) в первый регистр 4 (фиг. Зн-л). По АКмл дещифра- тор 14 первого преобразователя 2 кодов адреса формирует признак внешнего обращения с уровнем «1, соответствующий этому AR. (фиг. Зж-п). Затем он складывается по ИЛИ с предыдущими признаками внешнего обращения по данному ARcT, зафиксированными в регистре 4, после чего информация с выхода преобразователя 2 по сигналу записи с выхода И блока 1 (фиг. 36) записывается в блок 3 памяти (фиг. З/с-м)- После этого по следующему ARcr из блока 3 памяти выбирается следующий байт. Так обнуленные за цикл регенерации ячейки блока 3 памяти устанавливаются в «1 по строчным адресам внещних обращений.

В случае, когда внешняя выборка происходит по всем ARM.1, соответствующим данному ARcT, то при выборке из блока 3 памяти байта при подаче последнего из этих адресов, записи в регистр 4, сложении его содержимого с последним признаком выборки все выходы элементов ИЛИ 15 блока 2 устанавливаются в состояние «1. По ним блок 2 вырабатывает сигнал запроса уровня «О (фиг. Зр), по которому информационные выходы блока 2 устанавливаются в состояние «О, и это записывается в блок 3 памяти. По этому же запросу синхросигналом с выхода 1У блока 1 (фиг. Зг) во второй регистр 7 заносится признак внешнего обращения по AR (фиг. 3с-т), который сформирован вторым преобразователем 6 кодов адреса. При поступлении следующего адреса сигнал запроса сбрасывается. Так, при обращении по всем ARмл, соответствующим данному ARcT, во всех разрядах байта, хранящегося в блоке 3 по адресу ARcT, устанавливаются «О, а во втором регистре 7 - признак внешнего обращения в разряде, соответствующем этому ARcT.

Если внешнее обращение ведется по всем строчным адресам AR 1-7, все разряды регистра 7 устанавливаются в «1 и все байты блока 3 памяти оказываются обнуленными. В этом случае при переводе устройства в режим регенерации второй приоритетный шифратор 8 выдает сигнал запроса (фиг. ЗУ), по которому регистр 7 сбрасывается, и устройство вновь становится готовым к работе в режиме внешнего обмена.

В режиме регенерации адресный мультиплексор подключает к выходам 12 устройства выходы второго приоритетного шифратора 8, к выходам 13 - выходы первого шифратора 5. ARc определяются по отсутствию признаков внешнего обрашения во втором регистре 7, AR.t - по отсутствию признаков внешнего обраш,ения в регистре 4. Шифратор 8 формирует код ARcr, соответствующий первому из «О на выходах регистра 7. По нему из блока 3 памяти выбирается информационный байт и записывается в регистр 4. Шифратор 5 формирует код ARмл, соответствуюш.ий первому из «О на выходах регистра 4. Преобразователь 2 устанавливает «1 в разряде, соответствующем этому ARM.1, и складывает его с содержимым регистра 4. Эта информация по сигналу с выхода II блока 1 (фиг. 46) записывается в блок 3 памяти (фиг. 4к-м) и по синхросигналу с выхода 111 блока 1 (фиг. 4в) перезаписывается в регистр 4 (фиг. 4н-п) Тем самым первый из «О на входах шифратора 5 сбрасывается, а на его выходах устанавливается AR«.i, соответствующий следующему «О. Процесс продолжается до выставления на выходе шифратора 5 кода ARv.n, соответствующего последнему «О на выходах регистра 4. При сложении по ИЛИ в преобразователе 2 кода, соответствующего

ращения по ARv.i в блоке 2 памяти и по ARcT в регистре 7 оказываются сброшенными.

Таким образом, в устройстве с увеличением количества адресуемых по внешним об- рашениям столбцов динамической памяти в течение допустимого периода регенерации сокращается длительность опроса накопителя признаков внешних обращений, что суше- ственно сокрашает время занятости регенера10 цией. В предельном случае, при внешних обращениях по всем строчным адресам, быстродействие предлагаемого устройства для рассматриваемого варианта повышается по сравнению с прототипом в 16 раз по числу дов адресов ARcr.

Формула изобретения

1. Устройство для управления регенерацией информации в динамической памяти,

Пи,

содержащее адресный мультиплексор, блок памяти, первые преобразователь кодов адреса, регистр, приоритетный шифратор и блок синхронизации, первый вход которого является входом запроса внешнего обращения

25 устройства, первый выход блока синхронизации подключен, к управляющему входу адресного мультиплексора, второй выход блока синхронизации подключен к входу записи блока памяти, третий выход блока синхронизации подключен к синхровходу первого

30 регистра, информационные входы которого подключены к выходам блока памяти, выходы первого регистра соединены с входами первого приоритетного щифратора и информационными входами первого преобразователя кодов адреса, информационные выхоэтому ARw-n, и содержимого регистра 4 выход 35 ды которого подключены к информационным

запроса преобразователя 2 (фиг. 4р) устанавливается в «О. Информация на выходе преобразователя 2 сбрасывается, и по сигналу записи с выхода II блока 1 в блок памяти по данному ARcT записывается нулевой байт. Затем при наличии сигнала запроса преобразователя 2 по синхросигналу с выхода 1У блока 1 (фиг. 4г) во второй регистр 7 заносится код, оразованный во втором преобразователе 6 сложением по ИЛИ содержимо40

входам блока памяти, адресный вход которого подключен к первому выходу адресного мультиплексора и является первым информационным выходом устройства, адресный вход первого преобразователя кодов адреса подключен к второму выходу адресного мультиплексора и является вторым информационным входом устройства, первый адресный вход адресного мультиплексора является адресным входом устройства, втого регистра 7 с преобразованным в пози- 45 рой адресный вход адресного мультиплекционный кодом ARcT (фиг. 4с-г). В результате первый из «О на входах приоритетного шифратора сбрасывается, и на его выходах устанавливается , соответствующий следующему выходах регистра 7. Просора подключен к выходу первого приоритетного шифратора, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены второй преобразователь кода адреса, второй регистр и второй

цесс продолжается до исчезновения послед- 50 приоритетный шифратор, информационные

него из «О на выходах регистра 7, после чего шифратор 8 выдает сигнал запроса (фиг. 4у). По нему регистр 7 сбрасывается, и выдается сигнал окончания регенерации. Тем самым в процессе регенерации адресуются только те столбцы динамической памяти, которые не адресовались в предыдущем цикле внешнего обращения, а в конце регенерации все признаки внешнего об55

выходы которого подключены к информационным входам адресного мультиплексора, выход запроса второго приоритетного шифратора подключен к входу сброса второго регистра и входу задания режима блока синхронизации, информационные входы второго приоритетного шифратора соединены с выходами второго регистра и информационными входами второго преобразователя коращения по ARv.i в блоке 2 памяти и по ARcT в регистре 7 оказываются сброшенными.

Таким образом, в устройстве с увеличением количества адресуемых по внешним об- рашениям столбцов динамической памяти в течение допустимого периода регенерации сокращается длительность опроса накопителя признаков внешних обращений, что суше- ственно сокрашает время занятости регенерацией. В предельном случае, при внешних обращениях по всем строчным адресам, быстродействие предлагаемого устройства для рассматриваемого варианта повышается по сравнению с прототипом в 16 раз по числу кодов адресов ARcr.

Формула изобретения

1. Устройство для управления регенерацией информации в динамической памяти,

и,

содержащее адресный мультиплексор, блок памяти, первые преобразователь кодов адреса, регистр, приоритетный шифратор и блок синхронизации, первый вход которого является входом запроса внешнего обращения

устройства, первый выход блока синхронизации подключен, к управляющему входу адресного мультиплексора, второй выход блока синхронизации подключен к входу записи блока памяти, третий выход блока синхронизации подключен к синхровходу первого

регистра, информационные входы которого подключены к выходам блока памяти, выходы первого регистра соединены с входами первого приоритетного щифратора и информационными входами первого преобразователя кодов адреса, информационные выходы которого подключены к информационным

40

входам блока памяти, адресный вход которого подключен к первому выходу адресного мультиплексора и является первым информационным выходом устройства, адресный вход первого преобразователя кодов адреса подключен к второму выходу адресного мультиплексора и является вторым информационным входом устройства, первый адресный вход адресного мультиплексора является адресным входом устройства, вто45 рой адресный вход адресного мультиплексора подключен к выходу первого приоритетного шифратора, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены второй преобразователь кода адреса, второй регистр и второй

приоритетный шифратор, информационные

5

выходы которого подключены к информационным входам адресного мультиплексора, выход запроса второго приоритетного шифратора подключен к входу сброса второго регистра и входу задания режима блока синхронизации, информационные входы второго приоритетного шифратора соединены с выходами второго регистра и информационными входами второго преобразователя кодов адреса, адресные входы которого подключены к первым выходам адресного мультиплексора, выход второго преобразователя кодов адреса соединен с информационными входами второго регистра, синхровход которого подключен к четвертому выходу блока синхронизации, вход разрешения записи второго регистра соединен с выходом запроса и управляющим входом первого преобразователя кодов адреса.

2. Устройство по п. 1, отличающееся тем, что преобразователь кодов адреса содержит элементы И-НЕ, ИЛИ, И и дешифратор, выходы которого подключены к первым входам

элементов ИЛИ, выходы которых соединены с первыми входами элементов И, выходы которых являются информационными выходами преобразователя кодов адреса, входы дешифратора являются информационными входами преобразователя кодов адреса, адресными входами которого являются вторые входы элементов ИЛИ, вторые входы элементов И объединены и являются управляющим входом преобразователя кодов адреса, входы элемента И-НЕ соединены с выходами элементов ИЛИ, выход элемента И-НЕ является выходом запроса преобразователя кодов адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления регенерацией информации в динамической памяти | 1985 |

|

SU1251183A1 |

| Устройство для регенерации динамической памяти | 1988 |

|

SU1587594A1 |

| Устройство для формирования адресов регенерации динамической памяти | 1989 |

|

SU1709394A1 |

| Устройство прерываний микропроцессорной системы | 1988 |

|

SU1621030A1 |

| Устройство для управления регенерацией динамической памяти со свободными зонами | 1990 |

|

SU1762320A1 |

| Устройство для управления регенерацией динамической памяти со свободными зонами | 1990 |

|

SU1739388A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Вычислительное устройство | 1987 |

|

SU1430962A1 |

| Процессор | 1983 |

|

SU1213485A1 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств на основе элементов полупроводниковой динамической памяти. Цель изобретения - повышение быстродействия устройства. Устройство содержит блок 1 синхронизации, преобразователи 2, 6 кодов, блок 3 па.мяти, регистры 4, 7, приоритетные шифраторы 5, 8, адресный мультиплексор 9. В устройстве с увеличением количества адресуемых по внешним обраш,ениям столбцов динамической памяти в течение допустимого периода регенерации сокраш,ается длительность опроса накопителя признаков внешних обраше- ний, что существенно сокращает время обращения по всем строчным адресам. 1 з.п. ф-лы, 4 ил. (С (Л

(рие.2

ipueS

§У

| Оперативное запоминающее устрой-CTBO | 1979 |

|

SU809363A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для управления регенерацией информации в динамической памяти | 1985 |

|

SU1251183A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-04-15—Публикация

1986-06-30—Подача