сл

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования адресов регенерации динамической памяти | 1989 |

|

SU1709394A1 |

| Устройство для управления регенерацией динамической памяти со свободными зонами | 1990 |

|

SU1762320A1 |

| Устройство для регенерации динамической памяти | 1988 |

|

SU1587594A1 |

| Устройство для поиска свободных зон памяти | 1990 |

|

SU1829046A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для адресации памяти | 1989 |

|

SU1656543A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Устройство для обработки прерываний | 1985 |

|

SU1282124A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств на микросхемах динамической памяти. Целью изобретения является повышение быстродействия устройства. Устройство содержит первый 1 и второй 2 регистры, первый коммутатор 3, дешифратор 4, группу элементов ИЛИ 5, приоритетный шифратор 6, синхро- генератор 7, счетчик 8, элемент И-ИЛИ-НЕ 9, третий регистр 10, триггер 11, второй коммутатор 12, группу сумматоров по модулю два 13, синхронизирующие выход 14 и вход 15, информационный вход 16, управляющий выход 17, первый 18 и второй 19 адресные выходы. За счет введения третьего регистра, триггера, второго коммутатора и группы сумматоров по модулю два в устройстве поочередно устанавливаются старшие разряды адреса и поочередно перебираются

х| СО

ю

CJ 00 00

младшие разряды адреса регенерации без перерыва в регенерации при переходе от зоны к зоне регенерации. При этом обеспечивается возможность задания направления перебора зон и изменения направления

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств на микросхемах динамической памяти.

Цель изобретения - повышение быстро- действия устройства.

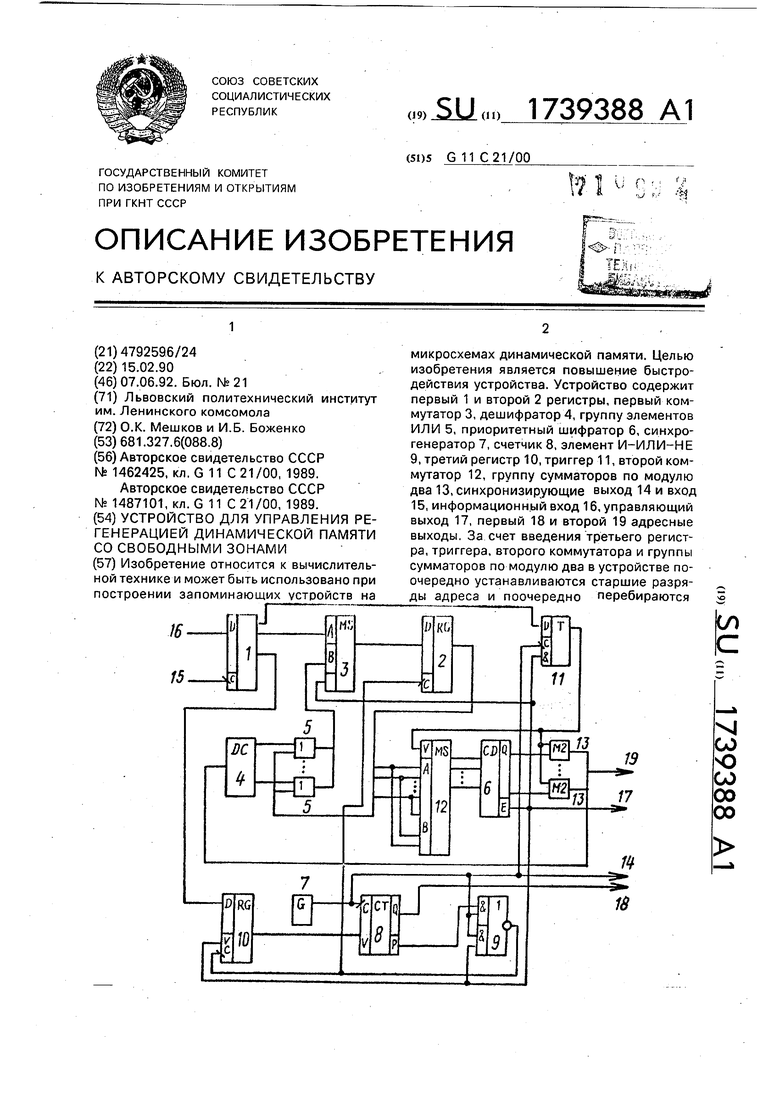

На чертеже представлена функциональная схема предлагаемого устройства.

Устройство содержит первый 1 и второй 2 регистры, первый коммутатор 3, дешифра- тор 4, группу элементов ИЛИ 5, приоритетный шифратор 6, синхрогенератор 7, счетчик 8, элемент И-ИЛИ-НЕ 9, третий регистр 10, триггер 11, второй коммутатор 12, группу сумматоров 13 по модулю два, синх- ронизирующий выход 14 и вход 15, информционный вход 16, управляющий выход 17, первый 18 и второй 19 адресные выходы. С выхода 18 задаются младшие разряды строчного адреса, а с выхода 19 - старшие разряды.

Устройство работает следующим образом.

По синхросигналу на входе 15 в регистр

Iзаносятся с входа 16 атрибуты зон. С пер- вого выхода регистра 1 снимается код зон. Зона, подлежащая регенерации, фиксируется уровнем 0 в соответствующем разряде регистра. С второго выхода регистра 1 снимается код направления адресации зон. Зо- на, подлежащая адресации по возрастанию, фиксируется уровнем О в соответствующем разряде регистра, зона, подлежащая адресации по убыванию,- уровнем 1. С третьего выхода снимается флажок направ- ления перебора зон, при переборе по возрастанию это - уровень О.

По сигналу запроса приоритетного шифратора 6 коммутатор 3 подключает к информационному входу регистра 2 первый выход регистра 1, регистр 10 переводится в режим записи, разрешается запись в триггер 11. По совпадению сигналов синхроге- нератора 7 и запроса шифратора элемент И-ИЛИ-НЕ 9 формирует сигнал записи. В регистр 2 заносится код зон, в регистр 10 - код направления адресации зон, в триггер

I1- флажок направления перебора зон. Код зон с выхода регистра 2 поступает через коммутатор 12 на вход шифратора 6 и сиг-

перебора адресов внутри зон при переходе от зоны к зоне. Это позволяет обеспечивать равнонаправленность адресации при внешних обращениях и регенерации и тем самым сократить время занятости устройства. 1 ил.

нал запроса на его выходе сбрасывается. Коммутатор 3 подключает к входам регистра выходы элементов ИЛИ 5, регистр 10 переводится в режим сдвига, запись в триггер 11 запрещается. По сбросу запроса на выходе 17 определяется возможность записи в регистр 1 новых атрибутов зон.

Шифратор 6 формирует на своем информационном выходе код, соответствующий первому из О на своих информационных входах. По О на выходе триггера 11 коммутатор 12 подключает выходы регистра 2 на входы шифратора 6 без перекоммутации. Сумматоры 13, выполняющие функцию управляемых инверторов, передают код с информационного выхода шифратора 6 на выход 19 без изменений. Тем самым наивысший приоритет присваивается первому разряду регистра 2 и на выходе 19 формируются старшие разряды адреса задействованной зоны с наименьшим значением кода адреса. Если на выходе триггера 11 присутствует 1, коммутатор 12 осуществляет перекоммутацию разрядов регистра 2: выход первого разряда подключается к последнему входу шифратора 6, второго - к предпоследнему, последнего - к первому. Сумматоры 13 инвертируют код на информационном выходе шифратора 6. Тем самым наивысший приоритет присваивается последнему из О на выходах регистра 1 и на выходе 19 формируется код адреса наибольшего значения.

По значению кода на выходах сумматоров 13 дешифратор 4 устанавливает 1 на том своем выходе, который соответствует этому коду. Элементы 5 производят сложение по ИЛИ унитарного кода дешифратора с содержанием регистра 2.

По сигналам синхрогенератора 7 на выходе 14 задается период выборки динамической памяти, а счетчик 8 генерирует младшие разряды адреса столбцов, входящих в подлежащую регенерацию зоны, старшие разряды которых установлены на выходе 19. Если на выходе регистра 10 присутствует О, счетчик инкрементируется, и перебор младших разрядов ведется по возрастанию, если 1 - счетчик декрементиру- ется, и перебор ведется по убыванию. По

совпадению сигналов синхрогенератора 7 и переноса (или заема) счетчика 8 элемент 9 формирует сигнал записи в регистр 2 и сигнал сдвига регистра 10. В регистр 2 заносится код, сформированный элементами 5,и на выходе регистра 2 устанавливается в 1 тот из находившихся в состоянии О разрядов, которому был присвоен наибольший приоритет. На выходе 19 формируется код, соответствующий уровню О следующего по приоритетному разряду регистра 2. По значению соответствующего этому разряду флажка, хранящемуся в регистре 10, счетчик 8 переустанавливается в режим суммирования (или вычитания) и перебираются младшие разряды адресов очередной подлежащей регенерации зоны.

После того, как перебраны адреса последней задействованной зоны, в регистре 2 устанавливается в 1 последний из уста- новленных перед операцией регенерации в О разрядов. Шифратор 6 формирует сигнал запроса, по которому в регистры 2 и 10 и триггер 11 из регистра 1 заносятся очередные атрибуты.

При подаче питающего напряжения регистры и триггер устанавливаются произвольно. Запись атрибутов по сигналу запроса шифратора 6 производится за один цикл регенерации в течение приведения ди- намической памяти в рабочее состояние, которое производится за 8-10 циклов регенерации.

Таким образом, в предлагаемом устройстве поочередно устанавливаются старшие адреса и поочередно перебираются младшие адреса регенерации без перерыва в регенерации при переходе от зоны к зоне. При этом обеспечивается возможность задания направления перебора зон и измене- ния направления перебора адресов внутри зон при переходе от зоны к зоне.

Это позволяет обеспечить равнонап- равленность адресации при внешних обращениях и регенерации и тем самым сократить время занятости устройства регенерацией.

Формула изобретения Устройство для управления регенера- цией динамической памяти со свободными зонами, содержащее первый и второй регистры, первый коммутатор, дешифратор, группу элементов ИЛИ, приоритетный шифратор, синхрогенератор, счетчик и элемент И-ИЛИ-НЕ, причем информационный вход первого регистра является информационным входом устройства, а синхровход пер: вого регистра является синхронизирующим

входом устройства, первый выход первого регистра подключен к первому информационному входу первого коммутатора, выход которого соединен с информационным входом второго регистра, выходы которого соединены с первыми входами соответствующих элементов ИЛИ, выходы дешифратора соединены с вторыми входами элементов ИЛИ, выходы которых соединены с вторым информационным входом первого коммутатора, выход синхрогенератора соединен с синхровходом счетчика и первыми входами первой и второй групп входов элемента И-ИЛИ-НЕ, информационный выход счетчика является первым адресным выходом устройства, второй вход первой группы входов элемента И-ИЛИ-НЕ подключен к выходу переноса счетчика, управляющий выход приоритетного шифратора соединен с управляющим входом первого коммутатора и вторым входом второй группы входов элемента И-ИЛИ-НЕ и является управляющим выходом устройства, выход элемента И-ИЛИ-НЕ соединен с синхровходом второго регистра, о т- личающееся тем, что, с целью повышения быстродействия устройства, оно содержит третий регистр, триггер, второй коммутатор и группу сумматоров по модулю два, причем второй выход первого регистра соединен с информационным входом третьего регистра, синхровход которого подключен к выходу элемента И-ИЛИ-НЕ, управляющий вход третьего регистра подключен к управляющему выходу приоритетного шифратора, а выход соединен с управляющим входом счетчика, третий выход первого регистра соединен с информационным входом триггера, синхровход которого подключен к выходу синхрогенератора, управляющий вход триггера подключен к управляющему выходу приоритетного шифратора, а выход триггера соединен с управляющим входом второго коммутатора и первыми входами сумматоров по модулю два, информационные входы первой группы коммутатора соединены с первого по последний с его информационными входами второй группы соответственно, с последнего по первый и подключены к соответствующим выходам второго регистра, выходы второго коммутатора подключены к соответствующим входам приоритетного шифратора, информационные выходы которого подключены к вторым входам сумматоров по модулю два, выходы сумматоров по модулю два подключены к входу дешифратора и являются вторым адресным выходом устройства.

| Устройство для управления регенерацией динамической памяти со свободными зонами | 1987 |

|

SU1462425A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Авторское свидетельство СССР № 1487101, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-06-07—Публикация

1990-02-15—Подача