Изобретение относится к выч нсли- тельной техт- ике и может быть использовано при построении быстродействующих запоминающих устройств большого объема на основе элементов полупроводниковой динамической памяти.

Цель изобретения - повышение быстродействия устройства.

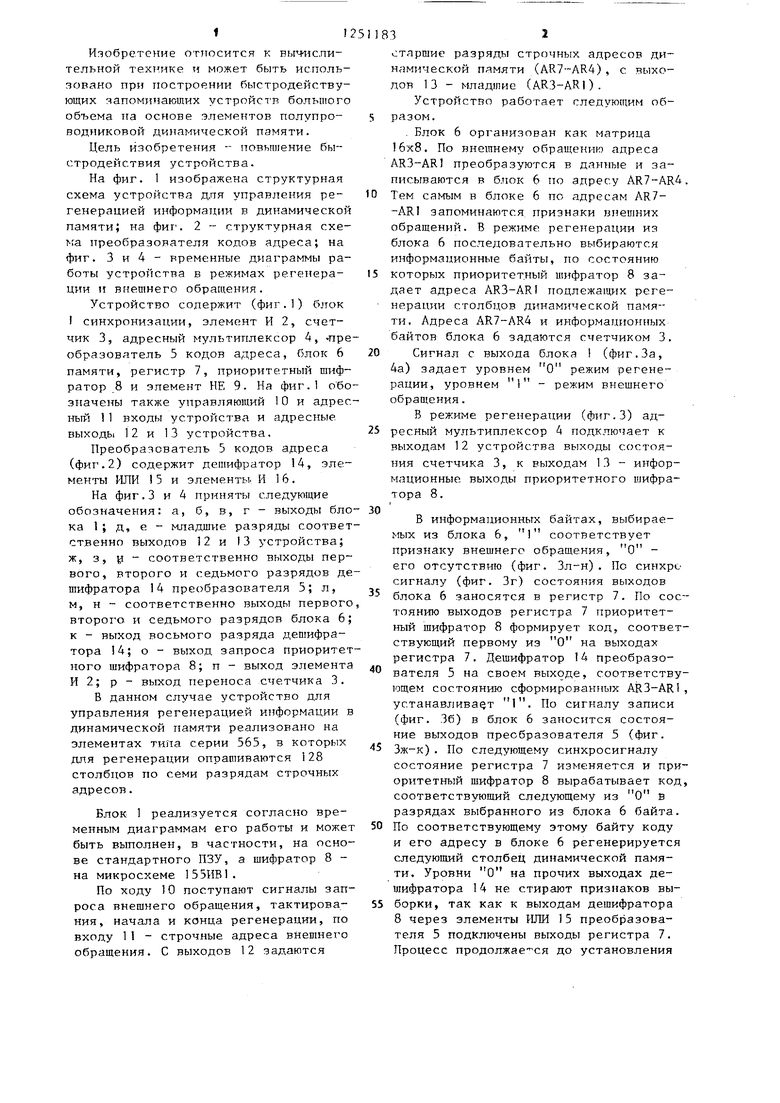

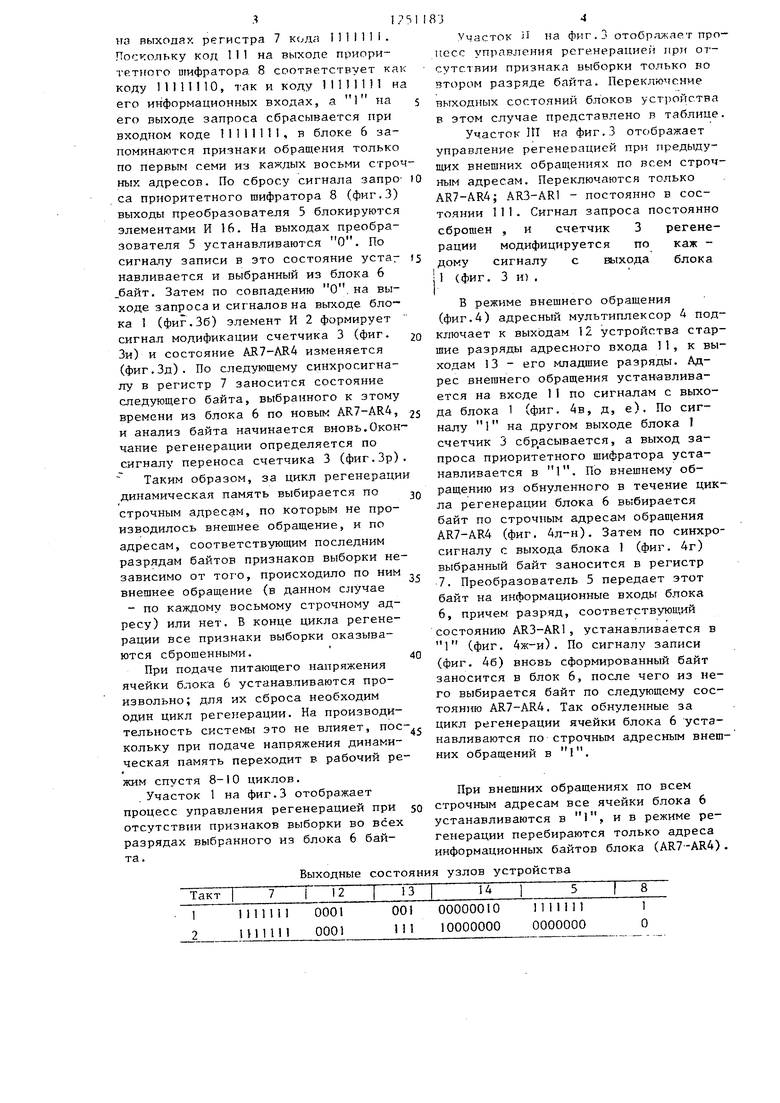

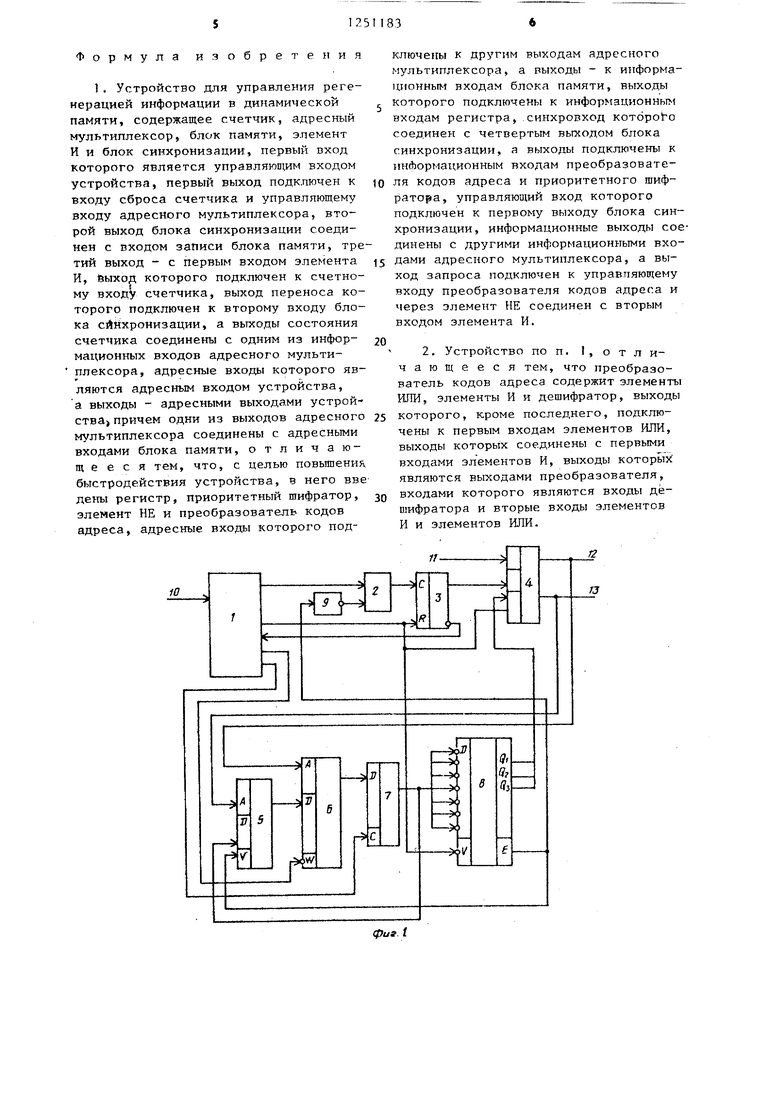

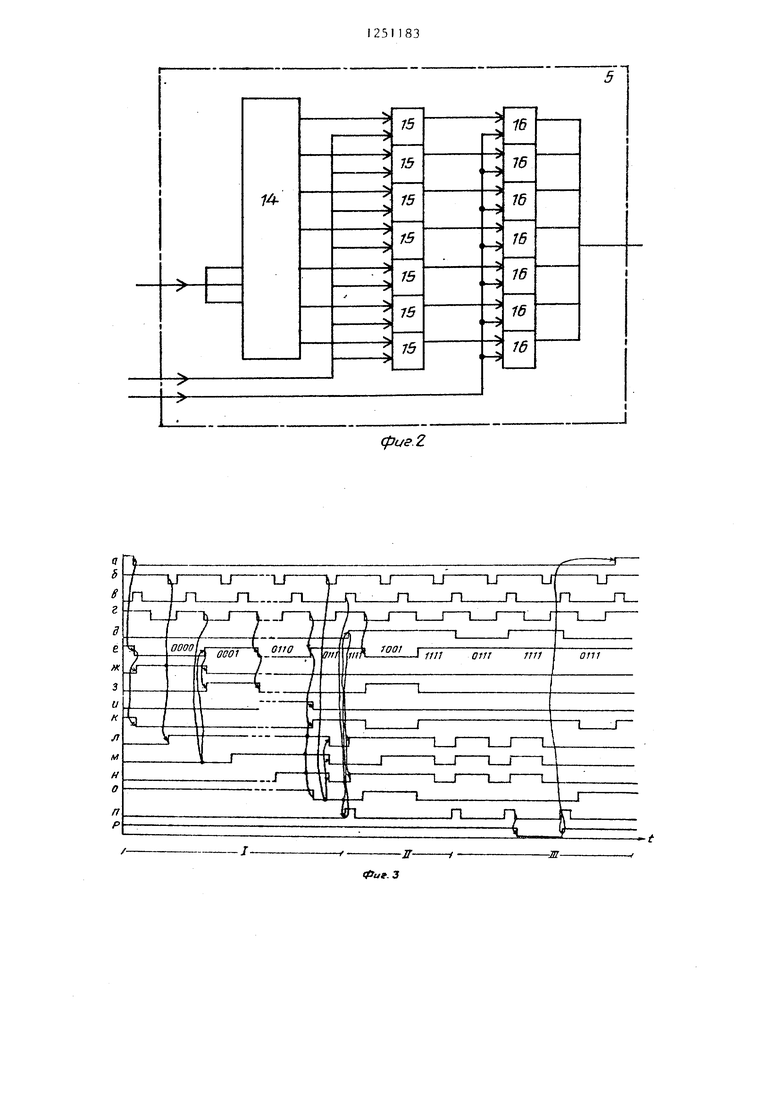

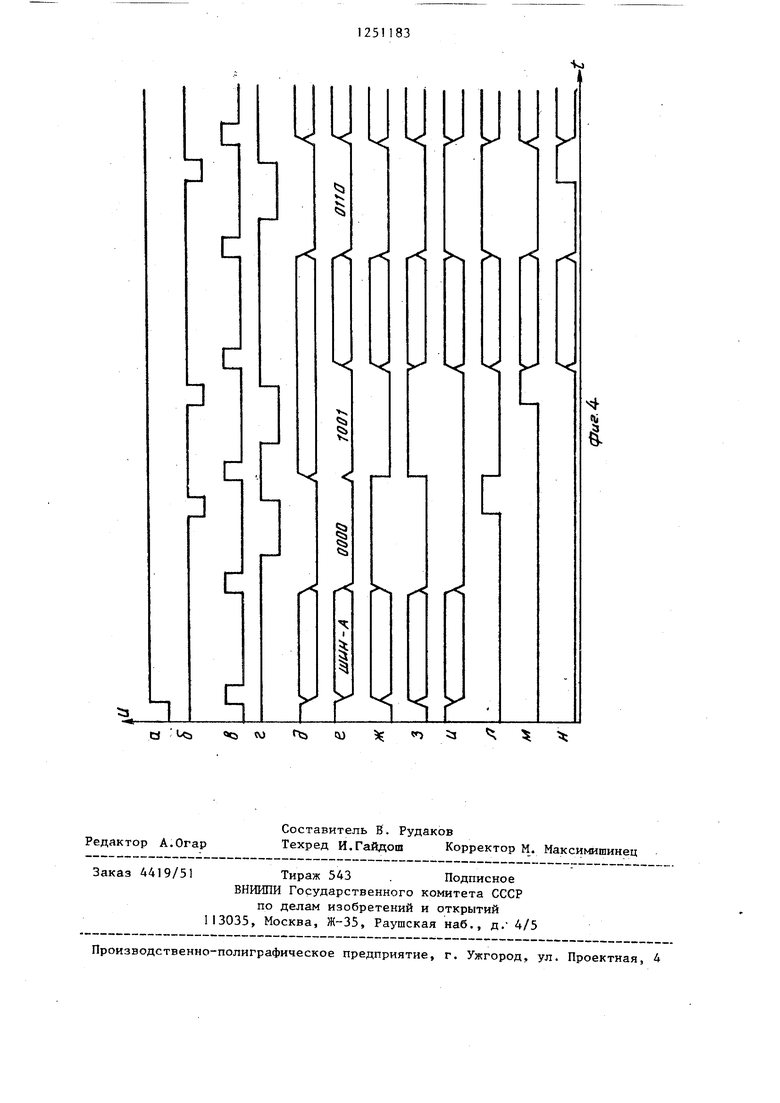

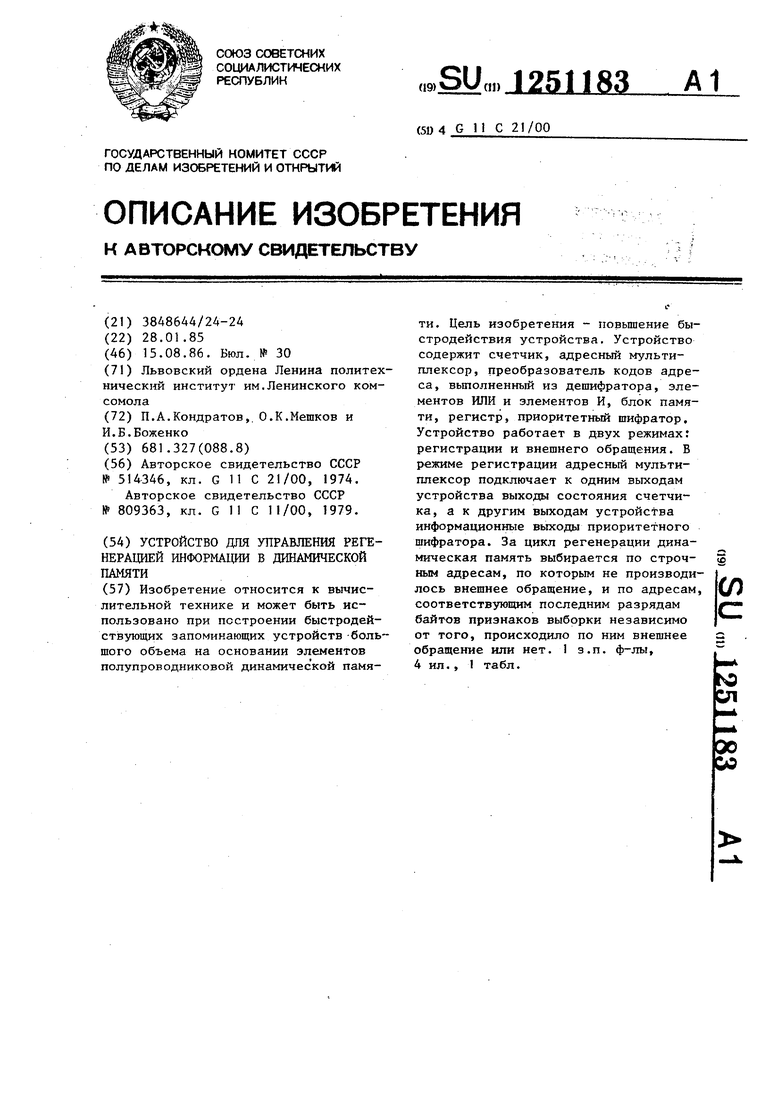

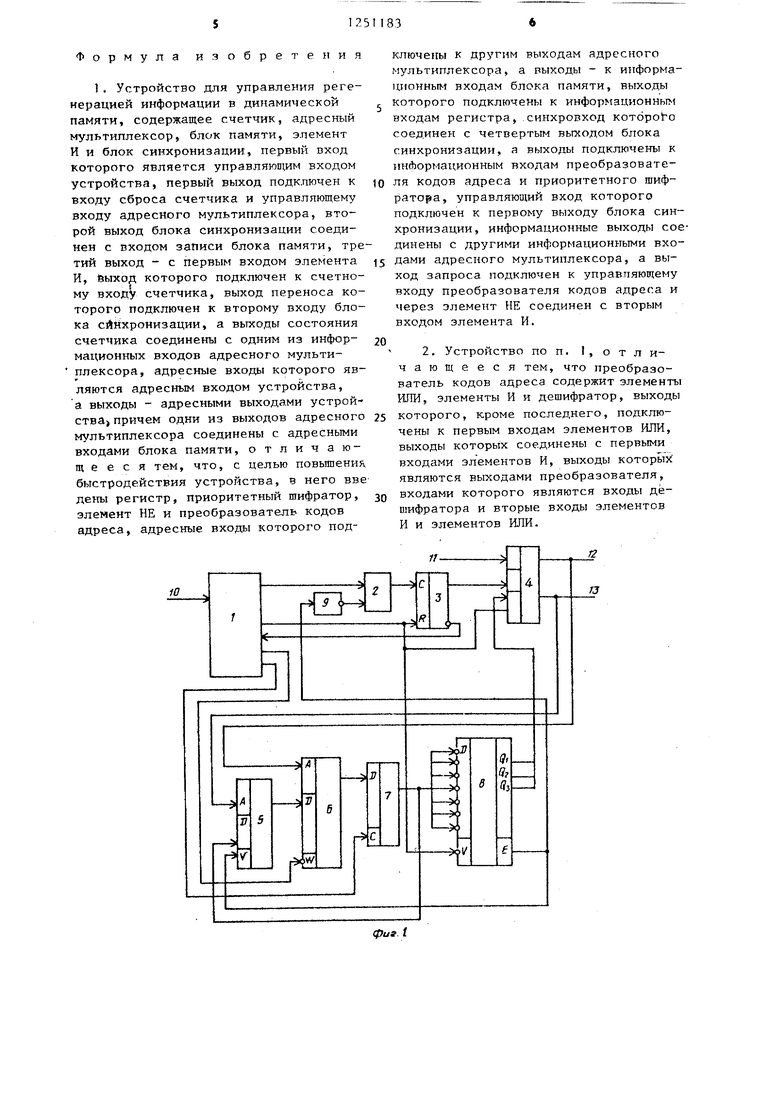

На фиг. 1 изображена структурная схема устройства для управления регенерацией информации в динамической памяти; на фиг . 2 - структурная схема преобразователя кодов адреса; на фиг. 3 и 4 - временные диаграммы работы устройства в режимах регенерации и внешнего обращения.

Устройство содержит (фиг.1) блок I синхронизации, элемент И 2, счетчик 3, адресный мультиплексор 4, -преобразователь 5 кодов адреса, блок 6 памяти, регистр 7, приоритетный шифратор 8 и элемент НЕ 9. На фиг.1 обозначены также управляющий 10 и адресный 11 входы устройства и адресные выходы 12 и 13 устройства.

Преобразователь 5 кодов адреса (фиг.2) содержит дешифратор 14, элементы ПЛИ 15 и элементы. И 16.

На фиг.3 и 4 приняты следующие обозначения: а, б, в, г - выходы блока 1 ; д, е - младщие разряды соответственно выходов 12 и 13 устройства; ж, 3, у - соответственно выходы первого, второго и седьмого разрядов дешифратора 14 преобразователя 5; л, м, н - соответственно выходы первого второго и седьмого разрядов блока 6; к - выход восьмого разряда дешифратора 4; о - выход запроса приоритетного шифратора 8; п - выход элемента И 2; р - выход переноса счетчика 3.

В данном случае устройство для управления регенерацией информации в динамической памяти реализовано на элементах типа серии 565, в которых для регенерации опрашиваются 128 столбцов по семи разрядам строчных адресов.

Блок 1 реализуется согласно временным диаграммам его работы и может быть выполнен, в частности, на основе стандартного ПЗУ, а шифратор 8 - на микросхеме 155ИВ1.

По ходу 10 поступают сигналы запроса внешнего обращения, тактирования, начала и конца регенерации, по входу 1 1 - строчные адреса внеп1него обращения. С выходов 12 задаются

старшие разряды строчных адресов динамической памяти (AR7-AR4), с выходов 13 - младшие (AR3-AR1).

Устройство работает следующим образом.

. Блок 6 организован как матрица 16x8, По внешнему обращению адреса AR3-AR1 преобразуются в данные и записываются в блок 6 по адресу AR7-AR4.

Тем самым в блоке 6 по адресам AR7- -ARI запоминаются, признаки внешних обращений. В режиме регенерации из блока 6 последовательно выбираются информационные байты, по состоянию

которых приоритетный шифратор 8 задает адреса AR3-AR1 подлежащих реге- нерации столбцов динамической памяти. Адреса AR7-AR4 и информационных байтов блока 6 задаются счетчиком 3,

Сигнал с выхода блока I (фиг.За, 4а) задает уровнем О режим регенерации, уровнем i - режим внешнего обращения.

В режиме регенерации (фиг.З) адресный мультиплексор 4 подключает к выходам 12 устройства выходы состояния счетчика 3, к выходам 13 - информационные выходы приоритетного шифратора 8.

В информационных байтах, выбираемых из блока 6, 1 соответствует признаку внешнего обращения, О - его отсутствию (фиг. Зл-н) . По синхросигналу (фиг. Зг) состояния выходов

блока 6 заносятся в регистр 7. По состоянию выходов регистра 7 приоритетный шифратор 8 формирует код, соответствующий первому из О на выходах регистра 7. Дешифратор 14 преобразователя 5 на своем выходе, соответствующем состоянию сформированных AR3-AR1, устанавливает 1. По сигналу записи (фиг. 36) в блок 6 затгосится состояние выходов преобразователя 5 (фиг.

Зж-к). По следующему синхросигналу

состояние регистра 7 изменяется и приоритетный шифратор 8 вырабатывает код, соответствующий следующему из О в разрядах выбранного из блока 6 байта.

По соответствующему этому байту коду и его адресу в блоке 6 регенерируется следующий столбец динамической памяти. Уровни О на прочих выходах дешифратора 14 не стирают признаков выборки, так как к выходам дешифратора 8 через элементы ИЛИ 15 преобразователя 5 подключены выходы регистра 7. Процесс продолжаешься до установления

S

на выходах регистра 7 кода I 1 1 I П i . Поскольку код 111 на выходе приоритетного шифратора 8 соответствует как коду 1 1 1 11П О, так и коду 11111111 на его информационных входах, а 1 на его выходе запроса сбрасывается при входном коде 11111111, в блоке 6 запоминаются признаки обращения только по первым семи из каждых восьми строчных адресов. По сбросу сигнала запро- Ю са приоритетного шифратора 8 (фиг.З) выходы преобразователя 5 блокируются элементами И 16. На выходах преобразователя 5 устанавливаются О. По сигналу записи в это состояние устаг 5 навливается и выбранный из блока 6 байт. Затем по совпадению О.на выходе запроса и сигналов на выходе блока 1 (фиг.Зб) элемент И 2 формирует сигнал модификации счетчика 3 (фиг. 20 Зи) и состояние AJR7-AR4 изменяется (фиг.Зд). По следующему синхросигналу в регистр 7 заносится состояние следующего байта, выбранного к этому времени из блока 6 по новым AR7-AR4, js и анализ байта начинается вновь.Окон™ чание регенерации определяется по сигналу переноса счетчика 3 (фиг.Зр). Таким образом, за цикл регенерации динамическая память выбирается по Q строчным адресам, по которым не производилось внешнее обращение, и по адресам, соответствующим последним разрядам байтов признаков выборки независимо от того, происходило по ним 2 внешнее обращение (в данном случае

- по каждому восьмому строчному адресу) или нет. В конце цикла регенерации все признаки выборки оказываются сброшенными. 40

При подаче питающего напряжения ячейки блока 6 устанавливаются произвольно; для их сброса необходим один цикл регенерации. На производительность системы это не влияет, пос- кольку при подаче напряжения динамическая память переходит в рабочий реjfOTM спустя 8-10 циклов.

Участок 1 на фиг.З отображает процесс управления регенерацией при $0 отсутствии признаков выборки во всех разрядах выбранного из блока 6 байта.

Выходные состояния узлов устройства

Такт

1111111 0001 001 00000010 1111111 1 ШИП 0001 111 10000000 0000000 О

I8-J4

Участок JI на фиг.З отображает процесс управления регенерацией при отсутствии признака выборки только во втором разряде байта. Переклю-чсние выходных состояний блоков уст)ойства в этом случае представлено в таблице

Участок Itl на фиг.З отображает управление регенерацией при предыдущих внешних обращениях по всем строчным адресам. Переключаются только AR7-AR4; AR3-AR1 - постоянно в состоянии 111. Сигнал запроса постоянно сброшен , и счетчик 3 регенерации модифицируется по каж - дому сигналу с выхода блока i1 (фиг. 3 И).

В режиме внешнего обращения (фиг.4) адресный мультиплексор 4 подключает к выходам 12 устройства старшие разряды адресного входа 11, к выходам 13 - его младшие разряды. Адрес внешнего обращения устан-авлива- ется на входе 11 по сигналам с выхода блока 1 (фиг. 4в, д, е). По сигналу 1 на другом выходе блока 1 счетчик 3 сбрасывается, а выход запроса приоритетного шифратора устанавливается в 1. По внешнему обращению из обнуленного в течение цикла регенерации блока 6 выбирается байт по строчным адресам обращения AR7-AR4 (фиг. 4л-н). Затем по синхросигналу с выхода блока 1 (фиг. 4г) выбранный байт заносится в регистр 7. Преобразователь 5 передает этот байт на информационные входы блока 6, причем разряд, соответствующий состоянию AR3-AR1, устанавливается в 1 (фиг. 4ж-и). По сигналу записи (фиг. 4б) вновь сформированный байт заносится в блок 6, после чего из него выбирается байт по следующему состоянию AR7-AR4. Так обнуленные за цикл регенерации ячейки блока 6 устанавливаются по строчным адресным внешних обращений в 1.

При внешних обращениях по всем строчным адресам все ячейки блока 6 устанавливаются в 1, и в режиме регенерации перебираются только адреса информационных байтов блока (AR7-AR4).

13

14

Формула изобретения

1, Устройство для управления регеерацией информации в динамической амяти, содержащее счетчик, адресный ультиплексор, блок памяти, элемент и блок синхронизации, первый вход которого является управляющим входом устройства, первый выход подключен к входу сброса счетчика и управляющему входу адресного мультиплексора, второй выход блока синхронизации соединен с входом записи блока памяти, третий выход - с первым входом элемента И, быход которого подключен к счетному входУ счетчика, выход переноса которого подключен к второму входу блока сАйхронизации, а выходы состояния счетчика соединены с одним из информационных входов адресного мульти- плексора, адресные входы которого являются адресным входом устройства, а выходы - адресными выходами устрой- ства причем одни из выходов адресного мультиплексора соединены с адресными входами блока памяти, отличающееся тем, что, с целью повышения быстродействия устройства, в него вве даны регистр, приоритетный шифратор, элемент НЕ и преобразователь кодов адреса, адресные входы которого подключены к другим выходам адресного мультиплексора, а выходы - к информационным входам блока памяти, выходы

которого подключены к информационным входам регистра, синхровход кот6ро1 о соединен с четвертым выходом блока синхронизации, а выходы подключены к информационным входам преобразователя кодов адреса и приоритетного шифратора, управляющий вход которого подключен к первому выходу блока синхронизации, информационные выходы соединены с другими информационными входами адресного мультиплексора, а выход запроса подключен к управляющему входу преобразователя кодов адреса и через элемент НЕ соединен с вторым входом элемента И.

2. Устройство по п. 1, о т л и- чающееся тем, что преобразователь кодов адреса содержит элементы ШШ, элементы И и дешифратор, выходы которого, кроме последнего, подключены к первым входам элементов ИЛИ, выходы которых соединены с первыми входами элементов И, выходы которых являются выходами преобразователя, входами которого являются входы дешифратора и вторые входы элементов И и элементов ИЛИ.

срие.2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления регенерацией информации в динамической памяти | 1986 |

|

SU1388945A1 |

| Устройство для регенерации динамической памяти | 1988 |

|

SU1587594A1 |

| Устройство для формирования адресов регенерации динамической памяти | 1989 |

|

SU1709394A1 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1988 |

|

SU1682997A1 |

| Устройство для вывода графической информации на экран телевизионного индикатора | 1987 |

|

SU1587482A1 |

| Устройство для сопряжения каналов ввода-вывода с оперативной памятью | 1986 |

|

SU1322298A2 |

| Устройство для сопряжения каналов ввода-вывода с оперативной памятью | 1985 |

|

SU1267427A1 |

| Устройство для управления регенерацией динамической памяти со свободными зонами | 1990 |

|

SU1739388A1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих запоминающих устройств -большого объема на основании элементов полупроводниковой динамичес кой памяти. Цель изобретения - повьш1ение быстродействия устройства. Устройство содержит счетчик, адресный мультиплексор, преобразователь кодов адреса, вьшолненный из дешифратора, элементов ИЛИ и элементов И, блок памяти, регистр, приоритетный шифратор. Устройство работает в двух режимах: регистрации и внешнего обращения. В режиме регистрации адресный мультиплексор подключает к одним выходам устройства выходы состояния счетчика, а к другим выходам устройства информационные выходы приоритетного шифратора. За цикл регенерации динамическая память выбирается по строчным адресам, по которым не производилось внешнее обращение, и по адресам, соответствующим последним разрядам байтов признаков выборки независимо от того, происходило по ним внешнее обращение или нет. 1 з.п. ф-лы, 4 ил., 1 табл. (С (Л сл ЭО

j

-ж ,к -. I .-....- .Ill ... 1

а Ub X5W f со o 4

Редактор А.Огар

Составитель В. Рудаков

Техред И.Гайдош Корректор М. Максимишинец

Заказ 4419/51 Тираж 543 . Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий II3035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для управления регенерацией информации в динамической памяти | 1974 |

|

SU514346A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Оперативное запоминающее устрой-CTBO | 1979 |

|

SU809363A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-08-15—Публикация

1985-01-28—Подача