Изобретение относится к вычислительной технике и может быть исполь- ioBBHO для организации комплексной отладки аппаратного и программного Обеспечения микропроцессорных систем, достроенных на базе однокристальных микроконтроллеров семейства 8051.

Цель изобретения - повьппение точности отладки за счет обеспечения возможности оценки состояния отлаживаемой системы по машинным цик,лам.

На фиг.1 приведена структурная схе 1Ца эмулятора (связи показаны в виде фин); на фиг.2 - укрупненная граф- фхема алгоритма работы. : Эмулятор содержит блок 1 интерфей- фа системы проектирования, блок 2 ре- истров адреса, блок 3 прерьшания, блок 4 трассировки по машинным циклам блок 5 управления записью/чтением, 0ЛОК 6 памяти отлаживаемой программы., блок 7 памяти вспомогательных процедур, коммутатор 8 данных, блок 9 мик- |ропрограммного управления, регистр 10 управления, коммутатор 11 состояния, блок 12 формирования команды холостого цикла работы и блок 13 интерфейса отлаживаемой системы.

п

5

0

достижении какой-либо точки останова эмулятор автоматически переводится в холостой режим работы, в котором, он выполняет цикл Ml:LIMP Ml; Ml 0202 (Ml - метка, 0202 - код командного холостого цикла работы). Этот цикл формируется с помощью блока 12. Состояние эмулятора непрерьшно опрашивается системой проектирования через коммутатор 10. Доступ к внутренним ресурсам эмулятора со стороны системы проектирования разрешен в случае достижения в блоке 3 точки прерьюания.

Система проектирования опрашивает регистры блока 4 трассировки по ма- шшшьм циклам, которые и дают ей информацию об истинном адресе останова. Блок 4 содержит регистры, которые фиксируют адреса последних четырех машинных циклов, выполняемых-эмулятором перед точкой останова, Используя память блока 6, система проектирования читает состояние эмулятора и по команде оператора модифицирует его. Чтение содержимого внутренних ресурсов осуществляется через соответствующие регистры блока 13.

При необходимости цикл работы эму

| название | год | авторы | номер документа |

|---|---|---|---|

| ВНУТРИСХЕМНЫЙ ЭМУЛЯТОР | 1996 |

|

RU2110833C1 |

| ВНУТРИСХЕМНЫЙ ЭМУЛЯТОР | 1999 |

|

RU2214621C2 |

| Устройство отладки микропрограммных блоков | 1988 |

|

SU1541617A1 |

| Устройство для отладки микропроцессорной системы | 1987 |

|

SU1453408A1 |

| Устройство для отладки программ | 1988 |

|

SU1624461A1 |

| Устройство для отладки программно-аппаратных комплексов | 1990 |

|

SU1795464A1 |

| Устройство для отладки программ | 1985 |

|

SU1298752A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для отладки микропроцессорных систем | 1989 |

|

SU1672455A1 |

Изобретение относится к вычислительной технике и предназначено для отладки микропроцессорных систем, построенных на базе однокристальных микроконтроллеров семейства 8051. Цель изобретения - повышение точности отладки за счет возможности оценки состояния отлаживаемой системы по машинным циклам. Подключаемая через блок 1 интерфейса системы проектирования инструментальная ЭВМ имеет программный доступ к блоку 2 регистров адреса, блоку 3 прерываний, блоку 4 трассировки по машинным циклам, блоку 5 управления записью /чтением, блокам памяти 6,7 отлаживаемой программы и вспомогательных процедур, регистру 8 управления, коммутатору 11 состояния и блоку 13 интерфейса отлаживаемой системы. После начальной загрузки блоков 3 и 7 производится исполнение отлаживаемой программы. При этом, по достижении точек останова в программе, эмулятор переводится в холостой режим работы с помощью блока 12 формирования команды холостого цикла работы. Доступ системы проектирования к внутренним ресурсам эмулятора может осуществляться по достижении в блоке 3 точки прерывания. Регистры блока 4 дают информацию об адресах останова в последних четырех машинных циклах. 2 ил.

Инструментальная ЭВМ системы npoeK-,Q лятора может быть повторен. Отлаженная программа блока 7 памяти эмулятора считьгаается системой проектирования для сохранения ее на дисках и последующей записи в постоянное запоминающее устройство эмулируемой микро- ЭВМ.

тирования, подключаемая к эмулятору, имеет программный доступ к блокам 2-7, регистру 10, коммутатору 1 1 и блоку 13.

Перед началом работы блок 7 загру- ркается рабочей программой, которую необходимо отладить на прикладной системе. Адресация блока 7 осуществляется с помощью блока 2 регистров адреса, предварительна загружаемого сие- темой проектирования. Блок 3 прерьюа- ния служит для задания прерывания. Прерывание ограничено четырьмя точками или одной точкой и диапазоном. Загрузка блока 3 прерывания осуществля- ется аналогично загрузке блока 7 памяти эмулятора. Блок 6 служит для хранения вспомогательных процедур в кодах эмулируемой однокристальной, мик- роЭВМ, которые служат для ее запуска контроля и загрузки содержимого ее внутренней памяти (данных и регистров). Память блока 6 скрыта по отношению к прикладной системе и не заметна для пользователей. После загрузки эмулятор переводится в режим исполнения прикладной программы. Это осуществляется с помощью служебных процедур, заносимых в блок 6. При

лятора может быть повторен. Отлажен

ная программа блока 7 памяти эмулятора считьгаается системой проектирования для сохранения ее на дисках и последующей записи в постоянное запоминающее устройство эмулируемой микро- ЭВМ.

Информация, считываемая с блока 4 системой про.ектирования, служит для контроля за реальньм прохождением от.- лаживаемой программы.

Блок 9 микропрограммного управления, регистр 10 управления и коммутатор I1 состояния служат для общего управления работой эмулятора. Блок 9 содержит схему синхронного запуска эмулятора и останова по сигналу прерывания, который генерируется блоком 3. Запуск эмулятора осуществляется по перепаду из О в 1 сигналов RUNC (запуск кода, лежащего в блоке 6) или RUNM (запуск кода, лежащего в блоке 7).управляющего слова. В обоих случаях из холостого цикла Ml:LIMP Ml управление передается на служебную подпрограмму блока 6, которая имеет следующую структуру:

Ml

N0 N0

тело программы,

где тело - часть программы, зависяща от выполняемой функции.

Обратный переход осуществляется при А8 V А9 1 .

Примером таких функций могут служить программы, написанные на языке ассемблера ASM51.

Чтение внутренней памяти данных:

MOV А, addr.B .

MOVX CR., А

LIMP LOOP (LOOP - метка)

Чтение бита:

С, .8

CR., А

LOOP

Чтение внешней памяти MOV .DPTR,addr. 16

MOVX А, CDPT

MOVX CR., А

LIMP LOOP

Чтение программной па

MOVDPT, .l6

MOVA,

MOVCA, CA + DPTR

MOVX|(3)R. , A

LIMP LOOP

Запись BO внутренюю п

MOV A, data

MOV addr. 8, A

LIMP LOOP

Установка бита:

MOV A, «r data

R R С

MOV bit, С

LIMP LOOP

Запись BO внешнюю пам

MOV DPTR, addr.16

MOV A, data

MOVX С DPTR, A

LIMP LOOP

0

5

0

5

0

5

При передаче управления на адрес 03004, А8 (аппаратная реализация) регистр 10 управления переходит в холостой цикл Ml:LSMP Ml.

При необходимости передачи управления на программу пользователя по адресу USER (точка, задаваемая оператором), которая хранится в блоке 6, используется процедура

NOP

NOP

LIMP USER

При этом блок 10 регистра управления должен быть запущен сигналом RUNM в остальных случаях - RUNG). Пассивный RUNC позволяет сработать . триггерам блока 9, приводящш эмулятор в режим работы с блоком эмулятора.

В этом режиме программа исполняется до появления сигнала прерьшания.

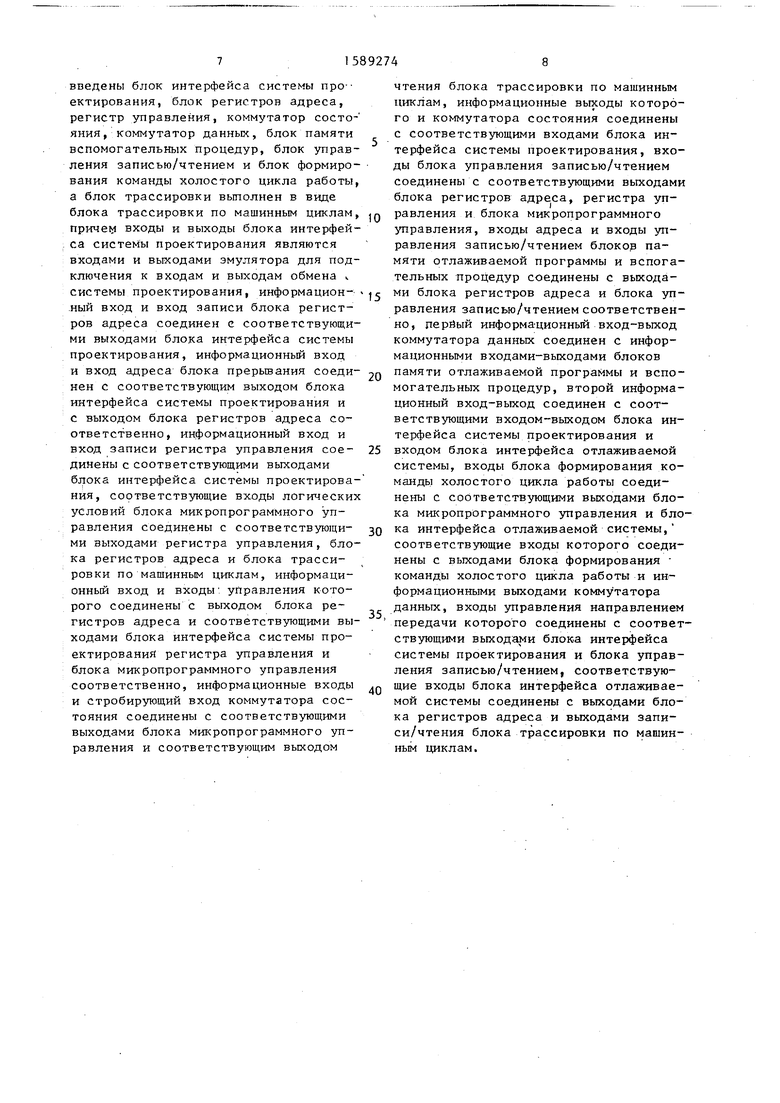

Указанные режимы работы эмулятора поясняются граф-схемой на фиг.2, где IDLE - холостой цикл работы; MON - вьптолнение программы из блока 6 памяти отлаживаемой программы; CODE - выполнение программ пользователя из блока 7 вспомогательных процедур.

Переход из режима IDLE .в режим Т MON осуществляется с помощью команды RUNC или RUNM. Обратный переход осуществляется с помощью команды RUNM . при А8 V А9 1. Для перехода из ре- . жима MON в режим CODE используется команда RUNC, а команда BREAK выпол- няет обратный переход.

40

Формула

изобретения

5

o

5

Внутрисхемный эмулятор, содержащий блок памяти отлаживаемой программы, блок прерывания, блок интерфейса отлаживаемой системы, блок трассировки, блок микропрограммного управления, соответствующий вход логических условий которого соединен с выходом прерьшания блока прерывания, соответствующие входы и выходы блока интерфейса отлаживаемой системы ярляются входами и выходами эмулятора для подключения к входам и выходам обмена отлаживаемой системы, о т л и ч а ю- щ и и с я тем, что, с целью повьш1е- ния точности отладки за счет возможности оценки состояния отлаживаемой системы по машинным циклам, в него

введены блок интерфейса системы про-- ектирования, блок регистров адреса, регистр управления, коммутатор состояния, коммутатор данных, блок памяти вспомогательных процедур, блок управления записью/чтением и блок формирования команды холостого цикла работы а блок трассировки выполнен в виде блока трассировки по машинным циклам причеу входы и выходы блока интерфейса системы проектирования являются входами и выходами эмулятора для подключения к входам и выходам обмена системы проектирования, информацион- ный вход и вход записи блока регистров адреса соединен с соответствующими выходами блока интерфейса системы проектирования, информационный вход и вход адреса блока прерьшания соеди- нен с соответствующим выходом блока интерфейса системы проектирования и с выходом блока регистров адреса соответственно, информационный вход и вход записи регистра управления сое- динены с соответствующими выходами блока интерфейса системы проектирования, соответствующие входы логических условий блока микропрограммного управления соединены с соответствующи- ми выходами регистра управления, блока регистров адреса и блока трассировки по машинным циклам, информационный вход и входы: управления которого соединены с выходом блока регистров адреса и соответствующими выходами блока интерфейса системы проектирований регистра управления и блока микропрограммного управления соответственно, информационные входы и стробирующий вход коммутатора состояния соединены с соответствующими выходами блока микропрограммного управления и соответствующим выходом

.,-

.Q срп25 зо .„

чтения блока трассировки по машинным циклам, информационные выходы которого и коммутатора состояния соединены с соответствующими входами блока интерфейса системы проектирования, входы блока управления записью/чтением соединены с соответствующими выходами блока регистров адреса, регистра управления и блока микропрограммного управления, входы адреса и входы управления записью/чтением блоков памяти отлаживаемой программы и вспога- тельных процедур соединены с выходами блока регистров адреса и блока управления записью/чтением соответственно, перйый информационньй вход-выход коммутатора данных соединен с информационными входами-выходами блоков памяти отлаживаемой программы и вспомогательных процедур, второй информационный вход-выход соединен с соответствующими входом-выходом блока интерфейса системы проектирования и входом блока интерфейса отлаживаемой системы, входы блока формирования команды холостого цикла работы соединены с соответствующими выходами блока микропрограммного -управления и блока интерфейса отлаживаемой системы, соответствующие входы которого соединены с выходами блока формирования команды холостого цикла работы и информационными выходами коммутатора данных, входы управления направлением передачи которого соединены с соответствующими выходами блока интерфейса системы проектирования и блока управления записью/чтением, соответствующие входы блока интерфейса отлаживаемой системы соединены с выходами блока регистров адреса и вькодами записи/чтения блока трассировки по машинным циклам.

IDLE 1 (АдилиАд}..

BREAK

RUNM

Фиг. 2

| УСТРОЙСТВО для ПРОВЕРКИ ГЕРМЕТИЧНОСТИ ТАРЪ! >&v и SAVIL'^^A | 0 |

|

SU168034A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

| Development Systems Handbook | |||

| - N.Y | |||

| Intel | |||

| Corp | |||

| , 1984, order number 280017-001, pp | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| I. | |||

Авторы

Даты

1990-08-30—Публикация

1988-02-09—Подача