вается число N, , которое определи- ется необходимым масштабом преобразо- вашя и соответствует максимальной величине входного сигнала U

Если преобразователь предпслагает- ся использовать при работе с одним Ш1И небольшим количеством фиксированных масштабных коэффициентов,, ОЗУ может быть заменено на ПЗУ в которое ,значение N. записзлш заранее перед установкой его в устройство,

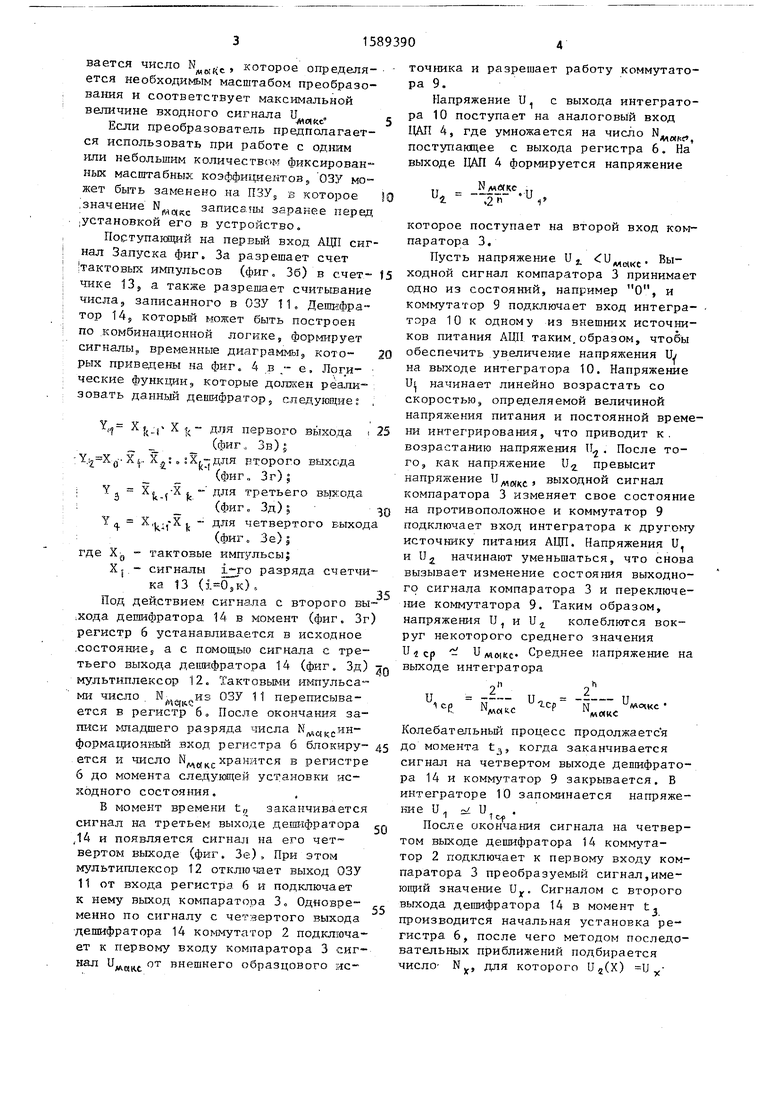

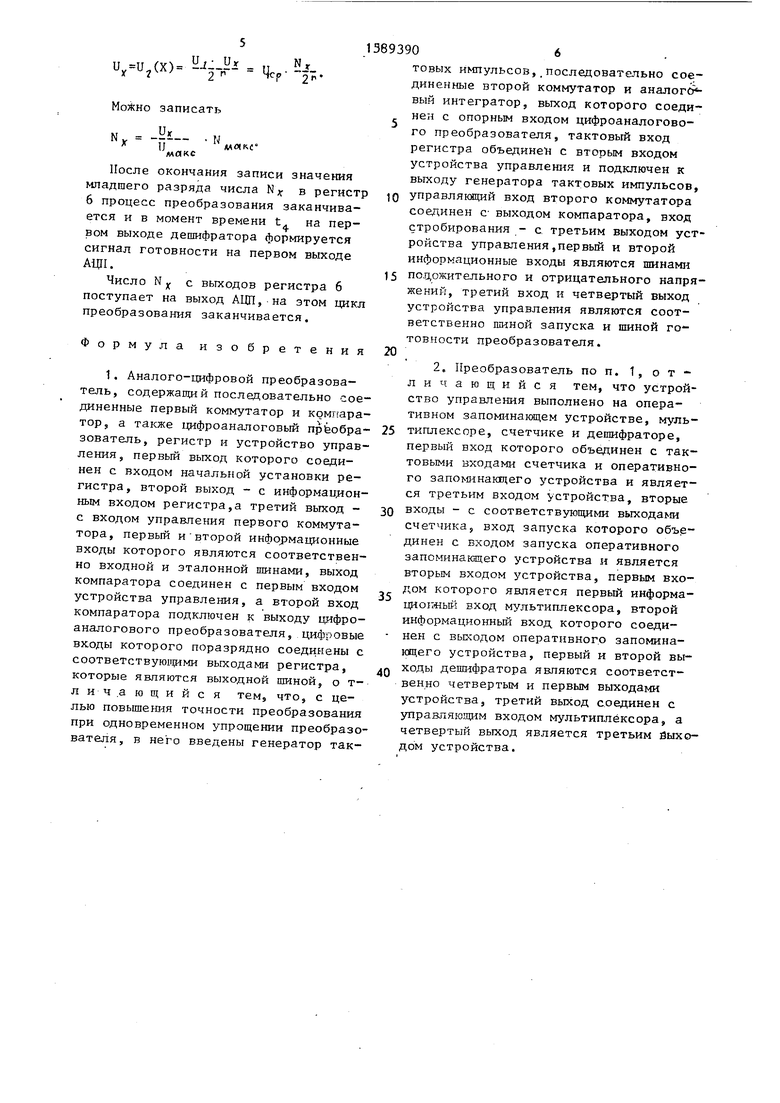

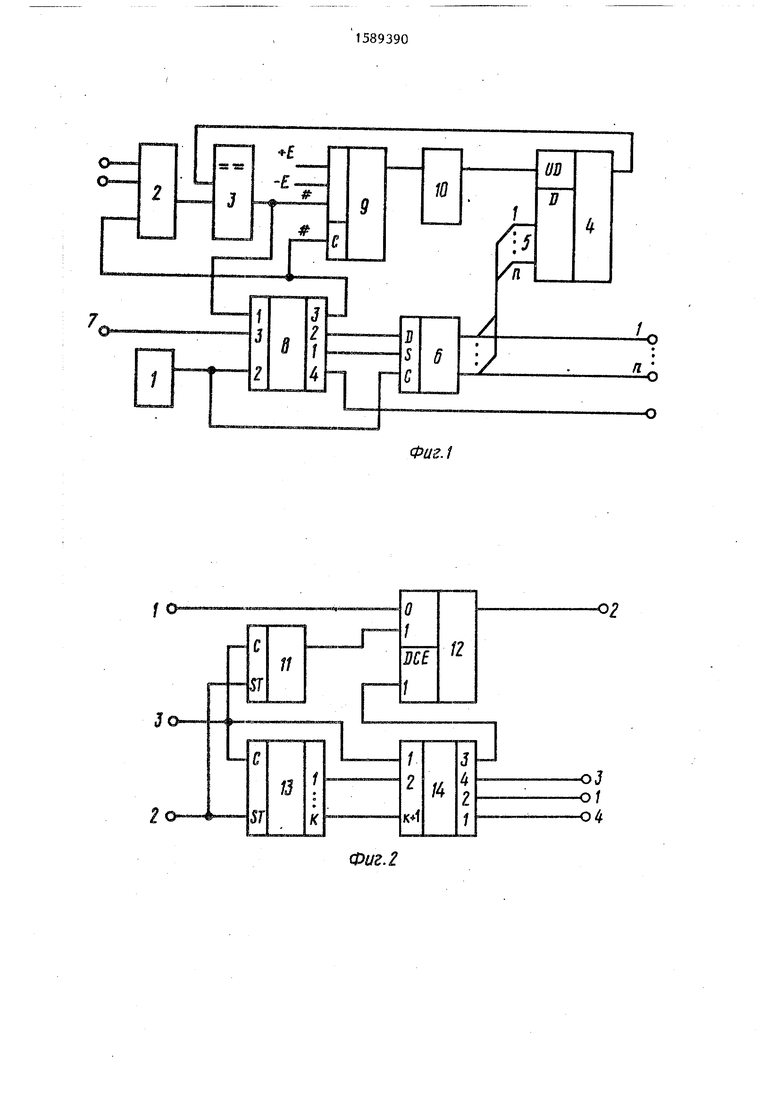

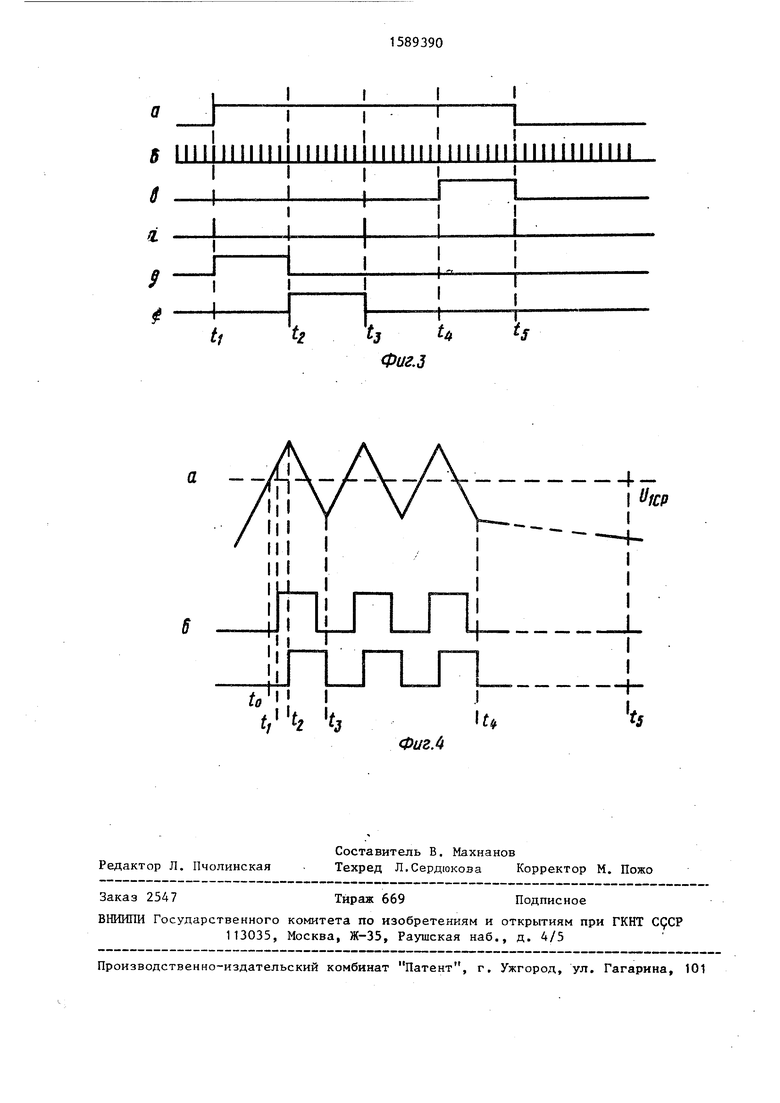

Поступамций на первьй вход АЩ1 сигнал Запуска фиг. За разрешает счет тактовых импульсов (фиг, Зб) в счет- чике 13, а также разрешает считьшание числа, записанного в ОЗУ 1U Дешж фра-- тор 14s которьй может быть построен по комбинационной логике, формирует сигналы, временные диаграм№1э кото- рых приведены на фиг. 4 в - е. Логи- ческие функции, которые дошкен реали- зовать данный деЕнфратор, следующиеt

1 k-Г k Р-ЛЯ первого выхода

„ (фиг,. Зв)| : Y.Xg-. Х|. „ ;Х --для второго выхода (фиг,, Зг) I

3 {«. третьего выхода (фиг„ Зд);

Ч- четвертого Еътход

:(фиг. Зе)|

где Xjj - тактовые имп-ульсы;

Xj,- сигналы разряда счетчика 13 ().

Под действием сигнала с второго вы хода дешифратора 14 в момент (фиг. Зг регистр 6 устанавливается в исходное .состояние; а с помощью сигнала с третьего выхода деашфратора 14 (фиг. Зд) мультиплексор 12. Тактовьми импульсами число Ы,,,из ОЗУ 11 переписывается в регистр 6, После окончания записи maдшeгo разряда числа М(.,,ин- формационный вход регистра 6 блокиру- ется и число N хранится в регистре б до момента следукщей установки исходного состояния.

в момент времени t,, заканчивается сигнал на третьем выходе дешифратора ,14 и появляется сигнал на его четвертом вькоде (фиг. Зе), При этом мультиплексор 12 отключает выход ОЗУ 11 от входа регистра 6 и подключает к нему вькод компаратора 3. Одновременно по сигналу с четвертого выхода дешифратора 14 кo пчyтaтop 2 подключает к первому входу компаратора 3 сигнал U;,(,,j от внешнего образцового ис

точника и разрешает работу коммутатора 9.

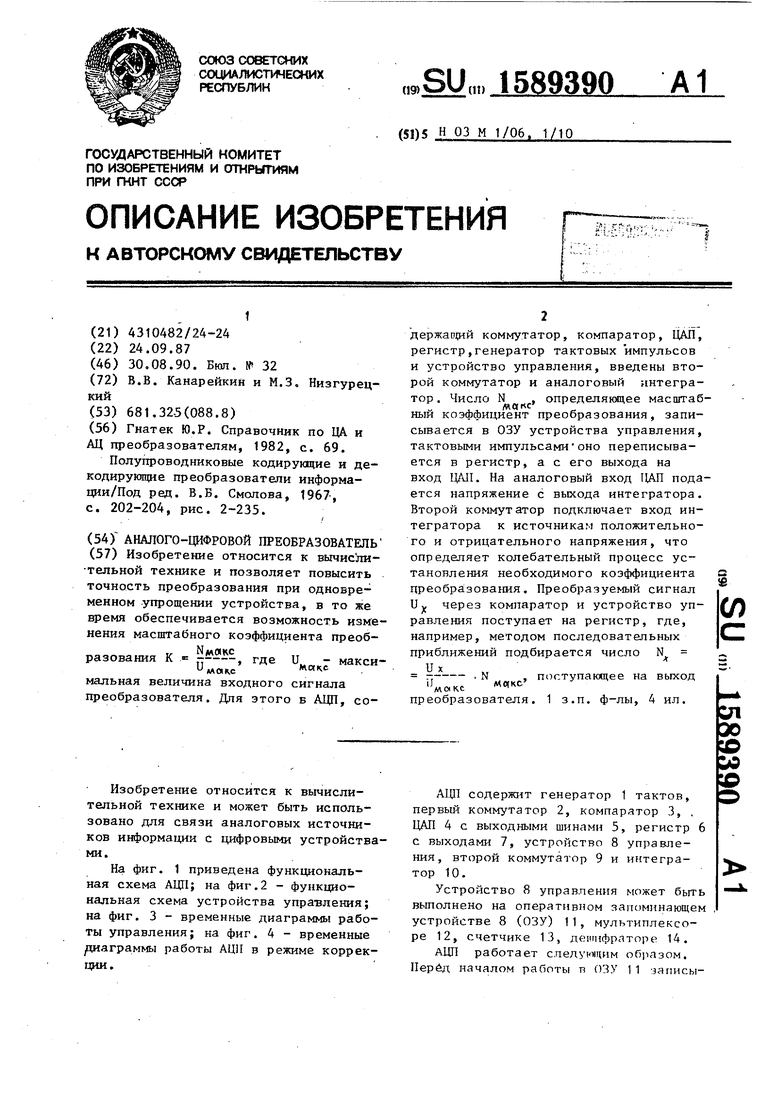

Напряжение U с выхода интегратора 10 поступает на аналоговый вход НАЛ 4, где умножается на число N..

flflOiPC f

поступающее с выхода регистра 6, На выходе иДП 4 формируется напряжение

и.

макс .. .-. ..и

Ю

1520

5

0

5

д з

которое поступает на второй вход компаратора 3,

Пусть напряжение U j млкс- i- ходной сигнал компаратора 3 принимает одно из состояний, например О, и коммутатор 9 подключает вход интегратора 10 к одному из внешних источников питания АЦП таким.образом, чтобы обеспечить увеличение напряжения Ш на выходе интегратора 10. Напряжение и начинает линейно возрастать со скоростью, определяемой величиной напряжения питания и постоянной времени интегрирования, что приводит к. возрастанию напряжения П, После того, как напряжение 0 превысит напряжение V , выходной сигнал компаратора 3 изменяет свое состояние на противоположное и коммутатор 9 подключает вход интегратора к другоьгу источнику питания АЦП. Напряжения U, и и начинают уменьшаться, что снова вызывает изменение состояния выходного сигнала компаратора 3 и переключение коммутатора 9. Таким образом, напряжения U и U колеблются вокруг некоторого среднего значения и 1 ср UMOIKC- Среднее напряжение на выходе интегратора

тд дз

50

5

Ср .л СР М ЛЯ01КС

2

N

(it . -„«КС

Колебательный процесс продолжается до момента , когда заканчивается сигнал на четвертом выходе дешифратора 14 и коммутатор 9 закрывается. В интеграторе 10 запоминается напряжение и . : и

11 Cf

После окончания сигнала на четвертом выходе дешифратора 14 коммутатор 2 подключает к первому входу компаратора 3 преобразуемый сигнал,име- Ю1ЦИЙ значение Uj,. Сигналом с второго выхода дешифратора 14 в момент t, производится начальная установка регистра 6, после чего методом последовательных приближений подбирается число- Nj, для которого иг(Х) U U,U,(X)y. .N.. MoJKHo записать

и.

и

N

макс

(И«КС

После окончания записи значения младшего разряда числа N в регистр 6 процесс преобразования заканчивается и в момент времени t на первом выходе дешифратора формируется сигнал готовности на первом выходе АЦП,

Число Ny с выходов регистра 6 поступает на выход АЦП,.на этом цикл преобразования заканчивается.

Формул

изобретения

1. Аналого-цифровой преобразователь, содержащий последовательно соединенные первый коммутатор и компаратор, а также цифроаналоговый преобразователь, регистр и устройство управления, первый выход которого соединен с входом начальной установки регистра, второй выход - с информаилон- ным входом регистра,а третий выход - с входом управления первого коммутатора, первый и-второй информационные входы которого являются соответственно входной и эталонной шинами, выход компаратора соединен с первым входом устройства управления, а второй вход компаратора подключен к выходу цифро- аналогового преобразователя, цифровые входы которого поразрядно соединены с соответствующими выходами регистра, которые являются выходной шиной, о т- л и ч а ю щ и и с я тем, что, с целью повьш1ения точности преобразования при одновременном упрощении преобразователя, в него введены генератор так3893906

товых импульсов,.поеледоватапьно соединенные второй коммутатор и аналоге вый интегратор, выход которого соеди- нен с опорным входом цифроаналогово- го преобразователя, тактовый вход регистра объединен с вторым входом устройства управления и подключен к выходу генератора тактовых импульсов,

10 управлякщий вход второго коммутатора соединен с- выходом компаратора, вход стробирования - с третьим выходом устройства управления,первый и второй информационные входы являются шинами

15 положительного и отрицательного напряжений, третий вход и четвертый выход устройства управления являются соответственно шиной запуска и шиной готовности преобразователя.

20

2, Преобразователь по п. 1, отличающийся тем, что устройство управления выполнено на оперативном запоминакщем устройстве, муль- 25 типлексоре, счетчике и дешифраторе, первый вход которого объединен с тактовыми входами счетчика и оперативного запоминающего устройства и является третьим входом устройства, вторые 30 входы - с соответствующими выходами счетчика, вход запуска которого объединен с входом запуска оперативного запоминающего устройства и является вторым входом устройства, первым вхо- дом которого является первый информа- цио17«ьй ВХОД мультиплексора, второй информационный вход которого соединен с выходом оперативного запоминающего устройства, первый и второй вы- 40 ходы дешифратора являются соответственно четвертым и первым выходами устройства, третий выход соединен с управляющим входом мультиплексора, а четвертый выход является третьим выходом устройства.

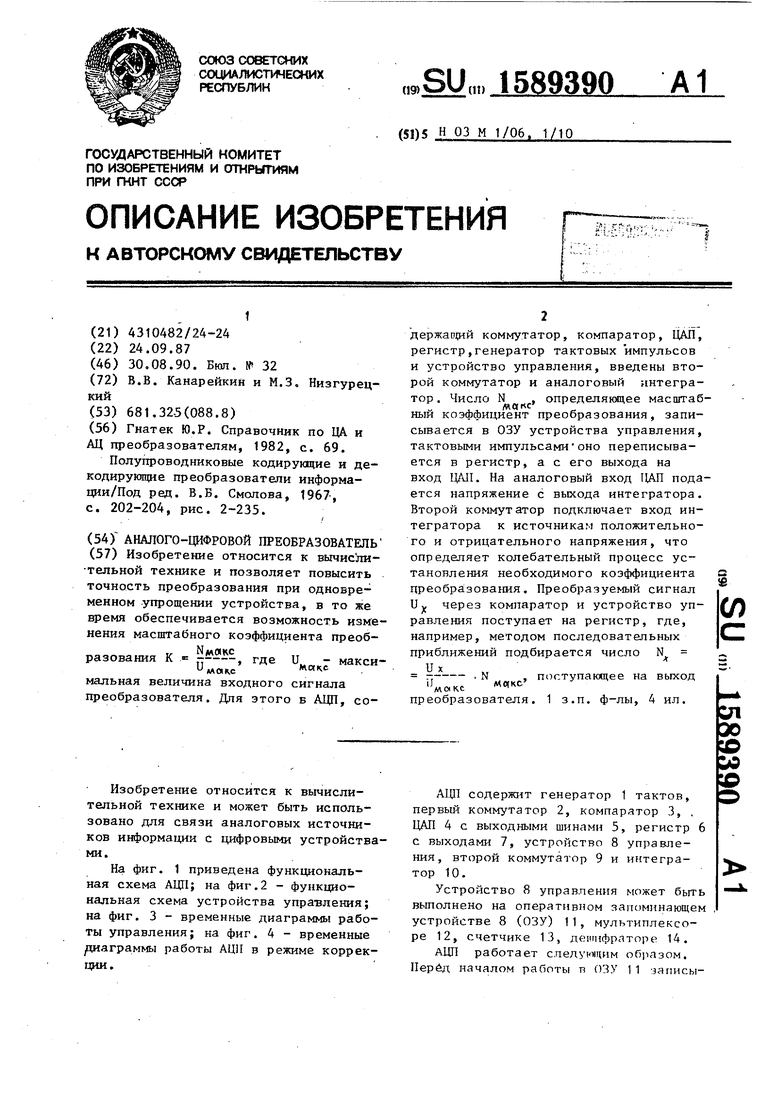

Фи2.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь сигналов датчиков переменного тока | 1986 |

|

SU1332531A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ НАПРЯЖЕНИЯ ПЕРЕМЕННОГО ТОКА В КОД | 2001 |

|

RU2195767C1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

| РЕГИСТРАТОР ПАРАМЕТРОВ АВАРИЙНЫХ СИТУАЦИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ ПОВЫШЕННОЙ ТОЧНОСТИ (ВАРИАНТЫ) | 2008 |

|

RU2376625C1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ РАЗЛИЧИЙ В ЧУВСТВИТЕЛЬНОСТИ ЭЛЕМЕНТОВ МАТРИЦЫ ФОТОПРИЕМНИКОВ | 1995 |

|

RU2108685C1 |

| Многоканальное измерительное устройство | 1988 |

|

SU1617430A1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| Цифроаналоговая система сбора и обработки информации | 1986 |

|

SU1363271A1 |

| Устройство для измерения динамической погрешности аналого-цифровых преобразователей | 1984 |

|

SU1221749A1 |

Изобретение относится к вычислительной технике и позволяет повысить точность преобразования при одновременном упрощении устройства, в то же время обеспечивается возможность изменения масштабного коэффициента преобразования K=N макс/V макс, где V макс - максимальная величина входного сигнала преобразователя. Для этого в АЦП, содержащим коммутатор, компаратор, ЦАП, регистр, генератор тактовых импульсов и устройство управления, введены второй коммутатор и аналоговый интегратор. Число N макс, определяющее масштабный коэффициент преобразования, записывается в ОЗУ устройства управления, тактовыми импульсами оно переписывается в регистр, а с его выхода на вход ЦАП. На аналоговый вход ЦАП подается напряжение с выхода интегратора. Второй коммутатор подключает вход интегратора к источникам положительного и отрицательного напряжения, что определяет колебательный процесс установления необходимого коэффициента преобразования. Преобразуемый сигнал V X через компаратор и устройство управления поступает на регистр, где, например, методом последовательных приближений подбирается число N X=V X/V макс .N макс, поступающее на выход преобразователя. 1 з.п. ф-лы, 4 ил.

Фиг. 2

t

I

I

I

III I I

5 IllllinilllinflllHllllllilllinilllllllllHlli

8 г

I

tf 0 4 s

Фиг,з

a

Редактор Л. Пчолинская

Составитель В. Махнанов

Техред Л.Сердюкоза Корректор М. Пожо

Заказ 2547

Тираж 669

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ 113035, Москва, Ж-35, Раушская наб., д. 4/5

I

I %д

Фиг Л

Подписное

| Гнатек Ю.Р | |||

| Справочник по ЦА и АЦ преобразователям, 1982, с | |||

| Способ приготовления пищевого продукта сливкообразной консистенции | 1917 |

|

SU69A1 |

| Полупроводниковые кодирующие и декодирующие преобразователи информации/Под ред | |||

| В.Б | |||

| Смолова, 1967, с | |||

| Приспособление к тростильной машине для прекращения намотки шпули | 1923 |

|

SU202A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| / | |||

Авторы

Даты

1990-08-30—Публикация

1987-09-24—Подача