сл

Г) 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Система позиционного управления электроприводом | 1987 |

|

SU1509826A1 |

| Импульсный регулятор | 1989 |

|

SU1682973A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ХАРАКТЕРИСТИК МАТЕРИАЛОВ | 1996 |

|

RU2108568C1 |

| Нелинейная следящая система | 1989 |

|

SU1615672A1 |

| Нелинейное корректирующее устройство | 1987 |

|

SU1536351A1 |

| МНОГОЗОННЫЙ ИНТЕГРИРУЮЩИЙ РЕГУЛЯТОР ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 2011 |

|

RU2471282C1 |

| Релейно-импульсный регулятор | 1983 |

|

SU1674058A1 |

| Следящая система | 1986 |

|

SU1427327A1 |

| Устройство для регулирования технологических параметров по заданной программе | 1983 |

|

SU1136121A1 |

| Система позиционного управления электроприводом | 1985 |

|

SU1312521A1 |

Изобретение относится к импульсным средствам автоматического управления и может быть использовано в качестве регулятора в системах автоматического управления компрессорными станциями. Целью изобретения является повышение точности и быстродействия регулирования. Импульсный регулятор содержит датчик 1, измеритель рассогласования 2, первый элемент ИЗ, первый усилитель мощности 4, исполнительный механизм 5, второй элемент И 6, второй усилитель мощности 7, первый интегратор 8, компаратор 9, задатчик 10, первый ключ 11, сумматор 12, второй интегратор 13, релейный элемент 14, выпрямитель 15, триггер Шмитта 16, дифференциатор 17, первый элемент НЕ 18, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 19, второй элемент НЕ 20, второй ключ 21, инвертор 22, третий элемент НЕ 23 и источник постоянного напряжения 24. Сущность изобретения заключается во введении плавно изменяющихся по частоте и длительности регулирующих импульсов в функции от величины сигнала ошибки регулирования. 2 ил.

00

01

Изобретение относится к импульсным средствам аптоматического управления и может быть использовано в качестве регулятора в системах автоматического управления компрессорными станциями.

Целью изобретения является повышение точности и быстродействия регулирования,

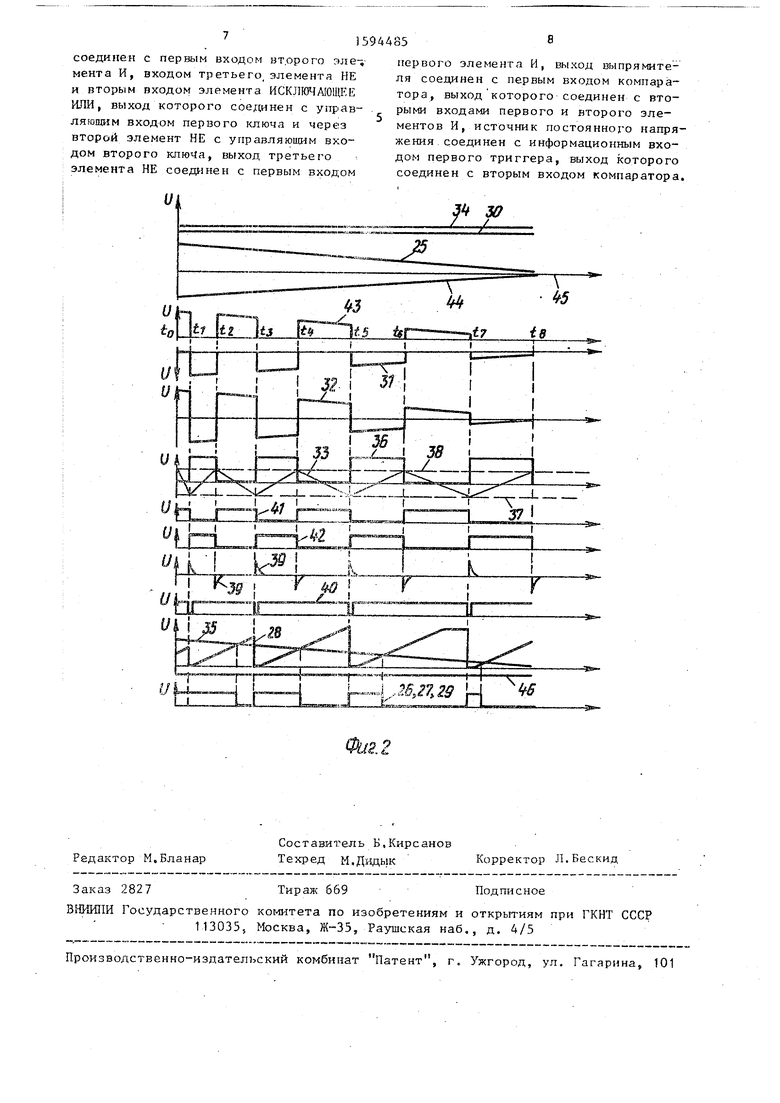

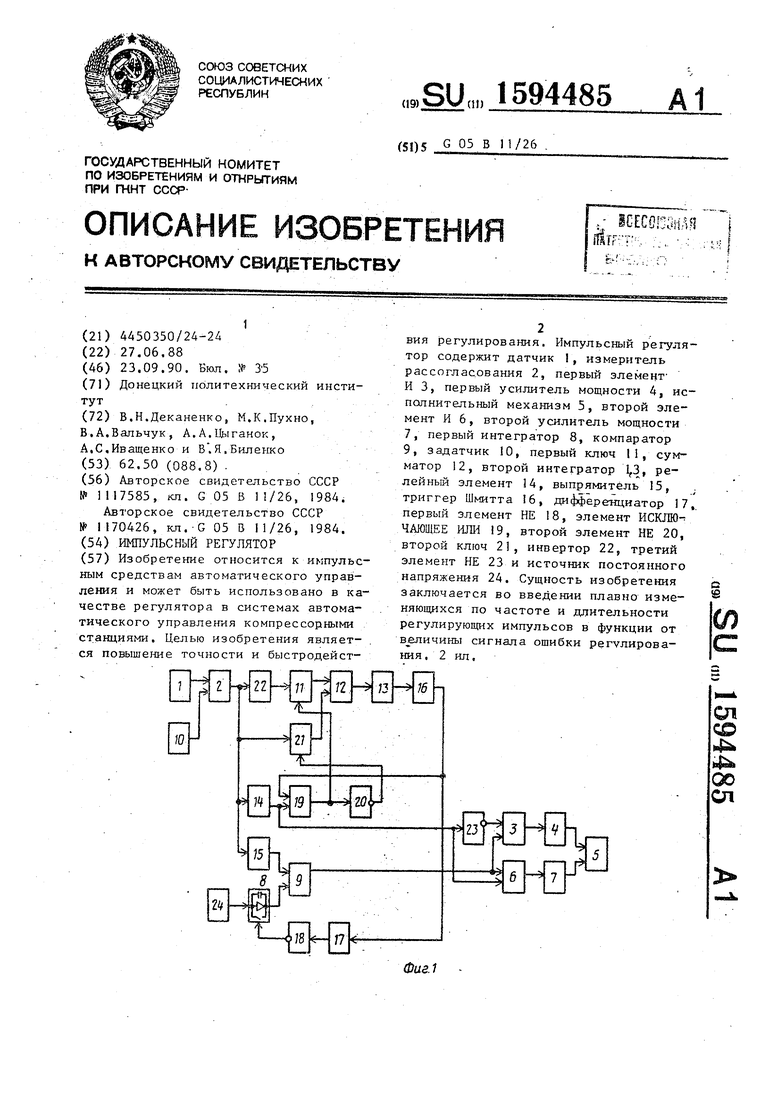

На 4иг, 1 представлена блок-схема импульсного ре.гулятора; на фиг. 2 - временные диаграммы сигналов на выходе блоков импульсного регулятора.

Импульсный регулятор (фиг. ) со- держит датчик I, измеритель 2 рассогласования, первый элемент И 3, первый усилитель 4 мощности, исполнительный механизм 5, второй элемент И 6, второй усилитель 7 мощности, пер- вый интегратор 8. компаратор 9. за- датчик 10, первый ключ 11, сумматор 12, второй.интегратор 13, рбшейшлй элемент 14, выпрямитель 15, триггер Шмитта 16, дифференциатор 17, первый элемент НЕ 18, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 19, второй элемент НЕ 20, второй ключ 21, инвертор 22, третий элемент НЕ 23, источник 24 постоянного напряжения.

Импульсный регулятор работает следующим образом.

Сигнал с датчика 1 поступает на вход измерителя 2 рассогласования, где сравнивается с сигналом зада1Ф1я (фиг, 2, кривая 30), Сигнал рассогласования, например, положительной полярности (фиг. 2, крирая 25) через замкнутый второй КЛЮЧ 21 поступает на второй вход сумматора 12 (кривая .43), Замкнутое состояьше второго ключа 21 и первого ключа 11 соответствует нулевому уровню сигнала на управляющем входе, соответственно кривые 42 и 41 (фиг, 2), С выхода сумматора

12 сигнал (фиг, 2, кривая 32, интервал времени t(,t,) поступает на вход второго интегратора 13, Выходное напряжение второго интегратора 13 щзи этом линейно уменьшается (фиг, 2, . кривая 33) до тех пор, пока не станет равным отрицательному уровню (г, 2, кривая 37), срабатывания триггера Шмитта 16 (фиг, 2, момент времени t ,) В этот момент времени триггер Шммтта 16 переключается в состояние кой 1 (фиг, 2, кривая 36, Момент времени t ), При этом сигнал кой 1 (кривая 36, интервал времени

-.

|5 20 5 30

.- 45

,-.

35

5

В54

) подается на первый вход гзле- мента ИСКЛЮЧАЮЩЕЕ ШШ 19, на второй вход которого подается также сигнал логической 1 с выхода релейного элемента 14 (фиг. 2, кривая 34), так как на его выходе присутствует положительный сигнал рассогласования (фиг. -2, кривая 25) с выхода измерителя 2 рассогласования.

На выходе элемента ИСКЛЮЧА10ЩЕЕ ИЛИ 19 появляется сигнал логического О (фиг, 2, кривая 41, интервал времени ), а на выходе второго элемента НЕ 20 - сигнал логической I (фиг, 2, момент времени , кривая 42), Эти сигналы, поступая на управляющие входы ключей 11 и 21, переключают первый 11 и второй 21 ключи (кривые 31 и 43 соответственно), при,этом первый ключ 11 замыкается, а второй ключ 21 раз-, мыкается. На первый вход сумматора 12 с выхода инвертора 22 через замкнутый первый ключ 11 (интервал времени t - -t.,j) подается инверсный сигнал рассогласования (фиг. 2, кривая 31), С выхода сумматора (фиг, 2, кривая 32, интервал времени t,-t) сигнал подается на вход второго интегратора 13, выходной сигнал которого начинает линейно возрастать (фиг, 2, кривая 33, момент времени t,-t). Напряжение на выходе второго интегратора 13 растет до тех пор, пока не становится равным 11оложительному уровню (фиг. 2, кривая 38) срабатывания триггера Шмитта 16, В этот момент времени (фиг. 2, момент времени t) выходной сигнал триггера Шмитта 16 (фиг. 2, кривая 36) становится равен логическому О,

При этом на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 19 подается сигнап логического О (фиг. 2, кривая 36, момент времени ), на второй вход - сигнал логической 1 (фиг, 2, кривая 34), так как сигнал рассогласования по-прежнему остается положительной ПОЛЯРНОСТИ. На выходе элемента ИСКЛЮЧАЮЩЕЕ ИЖ 19 появится сигнал логической 1 (фиг. 2, кривая 41, интервал времени t -t 3) , а на выходе второго элемента НЕ 20 - сигнал логического О (фиг,- 2, кри- вая 42, интервал времени ). После этого происходит переключение первого 11 и второго 21 ключей (фиг,- 2, кривые 31 и 43 соответственно), В интервале первый ключ 11 разомкнут, а второй ключ 21 замкнут.

Далее процесс повторяется аншюгнч- ным образом ((Ьнгл 2, интервал времени, tj-tj). С умеиыпением сигнала рассогласования (фьм-. 2, кривая 25) уменьшается уровень сигнала на выходе сумматора 12 (фиг. 2, кривая 32),

что приводит к более медленному возрастанию (убыванию) напряжения на выходе второго интегратора 13 (фиг, 2, кривая 33), а следовательно, и к уменьшению частоты импульсов на вы-, ходе триггера Шмитта 16 (фиг. 2, кривая 36),

С выхода триггера Шмитта 16 импульсы поступают на дифференциатор 1.7, с выхода которого продифференцированный сигнал (фиг. 2, кривая 39) через первый элемент НЕ 18 (фиг, 2, кривая 40) поступает на вход обнуления первого интегратора 8. На информационный вход интегратора 8 подается также сигнап (фиг. 2, кривая 46) с источника.24 постоянного напряжения, величина которого определяет скорость HapacTaifflH напряжения (фиг. 2, кривая 28) на выходе интегратора 8, Р моменты времени t,, t,,

t, t, когда сигнап на выходе первого элемента НЕ 18 (фиг. 2, кривая 40) равен логическому О, происходит обнуление первого интегратора 8, после чего сигнал на его выходе начинает линейно возрастать (фиг, 2, кривая 28), В эти периоды времени сигнап (фиг. 2, кривая 40) равен логической 1, Сигнал с выхода первого интегратора 8 поступает на первый вход компаратора 9, на-второй вход которого подается сигнал положительной полярности с выхода выпрямителя 15 (фиг, 2, кривая 35). Этот сигнал является выпрямленным сигналом рассогласования. На выходе компаратора

9 появляются импульсы (фиг, 2, кривая 29) , длительность и частота которых зависит от величины сигнала рассогласования.

Импульсы с выхода компаратора 9 поступают на первый 3 и второй б- элементы И, на другие входы которых подается сигнап с выхода релейного элемента 14 (фиг. 2, кривая 34), причем-; на первый элемент И 3 он подается, через третий элемент НЕ 23 (фиг. 2, кривая 45). Сигнал на выходе элемента НЕ 23 равен в этот период логическому О, Релейный элемент 14 служит для выбора канала регулирования

(Меньше или Больше). При гшложи- тельном сигнапе рассогласова.чия

(фиг. 2, кривая 25) работает канал Больше - второй элемент И 6, второй усилитель 7 мощности и испални- тельный механизм 5,

При отрицательном сигнале рассогласования работает канал Меньше третий элемент НЕ 23, первый элемент И 3, первый ycилитeJ ь 4 мощности и исполнительный механизм 5. Кроме того, в этом случае изменяется полярность сигнала на выходе релейного элемента

14 и очередность переключения первого 11 и второго 21 ключей при неизменных сигналах на выходах других блоков.

Таким образом, повышается точность и быстродействие регулятора за счет плавно изменяющихся по частоте и длительности регулирующих импульсов в зависимости от величины сигнала рассогласования.

25

0

5

0

5

0

5

Формула изобретения

Импульсный регулятор, содержащий датчик, выход которого соеданен с первым входом измерителя рассогласо- . вания, второй вход которого соединен с задатчиком, первый и второй элементы И, каждый из которых через соответствующий усилитель мощности соединен с соответствующим входом исполнительного- механизма, первь й ключ, два интегратора, сумматор и источник постоянного напряжения, отличающийся тем, что, с целью повышения точности и быстродействия регулирования , в него дополнительно введены инвертор, триггер Шмитта, второй ключ, репейный элемент, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, три элемента НЕ, выпрямитель, компаратор и дифференциатор, выход измерителя рассогласования соединен с входами выпрямителя, релейного элемента, второго ключа и инвертора, выход которого соедянен с входом первого ключа, выход которого соединен с первым входом сумматора, выход которого- через последовательно соединенные второй интегратор и триггер Шмитта соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и входом дифференци- атора, выход которого через первый элемент НЕ соединен с входам обнуления первого интегратора, выход второго ключа соединен с вторым входом сумматора, выход релейного элемента

f 1-11 I1 1,,жг1,гз 1-1 w

IР . i - fi-- --t.,-,,-.,j-py.-v......

У, 30

| Импульсный регулятор | 1983 |

|

SU1117585A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Импульсный регулятор | 1984 |

|

SU1170426A1 |

Авторы

Даты

1990-09-23—Публикация

1988-06-27—Подача