1

Изобретение относится к аналогоцифровым преобразователям и может быть использовано в связи, вычислительной и измерительной технике, а также в автоматизированных системах управления технологическими процессами и системах автоматизации научных исследований.

По основному авт.св. 805489 известен следящий аналого-цифровой преобразователь, содержаний блок сравнения, первый вход которого соединен с датчиком входного сигнала, а второй вход соединен с выходом цифро-аналогового преобразователя, цифровые .входы которого соединены с выходами соответствующих разрядов реверсивного счетчика, выход блока сравнения соединен с первьм входом логического блока, второй вход которого соединен с единичным выходом триггера переполнения реверсна ного счетчика, счетные входы триггеров реверсивного счетчика соединены с соответствующими .:выходами группы элементов И, первые входы которых соединены с вьосодами соответствующих разрядов распределителя импульсов, управляющий вход блока сравнения соединен с первьм выходом блока

управления, первый вход крторого соединен с выходом генератора импульсов, вт.орой вход соединен с выходом логического блока, второй и третий выходы соединены соответственно со входами сложения и вычитания реверсивного счетчика, четвертый выход соединен со вторыми входами группы элементов И, пятый выход соединен

10 со входом сдвига вправо распределителя импульсрв и с первым входом блока разрешения удвоения, второй вход которого соединен с шестым выходом блока управления, а выход 15 блока разрешения удвоения соединен со входом сдвига влево распределителя импульсов 1.

Недостатке этого преобразователя является большая погрешность преоб20разования, обусловленная отсутствием коррекции смены направления изменения сигнала. Например, если направление изменения сигнала некоторое время не менялось, то в результате

25 повторякидихся ответов блока сравненения шаг квантования растет. Допустим, что на 1-ом шаге образцовый сигнал принял.значение Vo(i), а на (i + 1)-ом шаге V (i+D Vo(l),

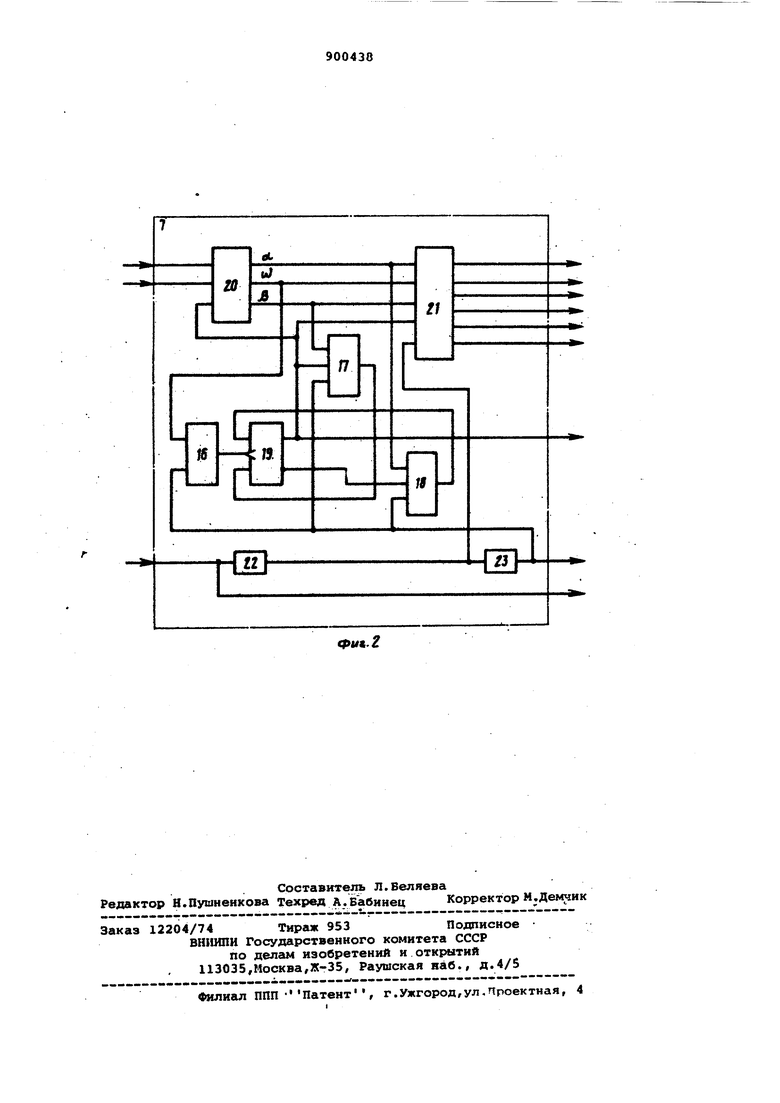

30 входной сигнал за это время сменил направление изменения и стал V, V (1) , т.е. искать входной сиг нал (как это делается в известном устройстве) между уровнями VQ (i) и VQ (i + I) бессмысленно и, кроме того, этот поиск пр.иводит к потере времени и отставанию образцового сигнала от входного что, в свою очередь, приводит к увеличению погрешности преобразования. Кроме того, в известном устройст ве при большой скорости изменения входного сигнала вблизи границ диапазона возможных изменений зна™ сигнала возможен выход величи ны числового эквивалента за границы диапазона, что также увеличивает погрешность преобразования. Цель изобретения - уменьшение погрешности преобразования. Поставленная цель достигается тем, что в следящий аналого-цифрово преобразователь, содержащий первый блок сравнения, первый вход которог соединен с датчиком входного сигнал а второй вход соединен с выходом первого цифро-аналогового преобразо вания, цифровые входы которого соед нены с выходами соответствующих раз рядов реверсивного счетчика, выход первого блока, второй вход которого соединен с единичным выходом тригге ра переполнения еверсивного счетчика, счетные входы триггеров ревер сивного счетчика - соединены с соответствующими выходами первой группы элементов первые вхрды которых сое динены с выходами соответствующих разрядов распределителя mCiyjribcoB, перЬый выход блока,управления соеди нен с выходом генератора импульсов, второй вход соединен с выходом первого логического блока, первый и вт рой выходы соединены соответственно со входами установки режима сложения и вычитания реверсивного счетчи ка, третий выход соединен со вторыми входами первой группы элементов и, четвертый выход соединен со входом сдвига вправо,распределители импульсов,пятый выход соединен с первым вхбдом блока разрешения удва ивания, выход которой соединен со входом сдвига влево распределителя импульсов, введены второй блок срав нения, второй цифроаналоговый преобразователь, регистр с дополнительным старшим разрядом пepeпoлнeн второй логический блок,вторая и тре группы элементов И,причем первый вх второго блока сравнения соединен о выходом датчика входного сигнала, второй вход соединен с шестым выходом блока управления и с третьш-i входом первого блока сравнения, а третий вход соединен с выходом второго цифро-аналогового преобразо вания, цифровые входы которого соединены с выходами соответствующих разрядов регистра, выход второго блока сравнения соединен с первым входом второго логического блока, второй вход которого соединен с единичным вьссодом триггера переполнения регистра, а выход соединен с третьим входом блока управления, установочные входы разрядов регистра соедине ны с выходами соответствующих разрядов реверсивного счетчика и со второй группой входов блока разрешения удваивания, третья группа входов которой соединена с выходами соответствующих разрядов распределителя импульсов, вторые входы второй группы элементов И соединены с седьмым выходом блока управления, при этом выходы разрядов регистра соединены с первыми входами третьей группы элe 1eнтoв И, вторые входы которых соединены с восьмым выходом блока управления, а выходы соединены с установочными входами соответствующих разрядов реверсивного счетчика, девятый выход блока управления соединен с шиной N . На фиг.1 представлена функциональная блок-схема следящего аналого-цифрового преобразователя; на фиг. 2 - один из возможных вариантов реализации блока управления. Устройство содержит первый блок 1 сравнения, первый цифроаналоговый преобразователь 2, ре.версивный счет чик 3, первый логический блок 4,первую группу элементов И 5, распределитель 6 импульсов, блок 7 управления, генератор 8 импульсов, блок 9разрешения удвоения, второй блок 10сравнения,второй иифроаналого-вый преобразователь 11, регистр 12, второй логический блок 13, вторая и третья группы элементов И 14 и 15, блок 7 управления, содержащий три элемента И 16 - 18, триггер 19, первый и второй дешифраторы 20 и 21, первый и второй элементы 22 и.23 задержки. Второй логический блок 13 анало: гичен первому логическому блоку 4, Эти логические блоки предназначены для устранения опасности выхода из режима слежения при работе вблизи границ диапазона. Для этого они при единичном состоянии соответствующего триггера переполнения инвертируют ответ соответствующего блока сравнения. .Введем следующие обозначения сигналов (фиг.55: Sj - выход i-ro логического блока, равный единице, если соответствую1дий образцовый уровень Меньше входного сигнала; «С- 1, если входной сигнал находится выше верхней границы отрезка; U/ - 1, если входной сигнал находится внутри отрезка;

- 1, если входной сигнал находится ниже нижней границы , отрезка;

g - сигнал от генератора штульсов;

g - сигнал на выходе первого элемента задержки;

д - сигнална выходе второго элемента задержки;

N - 1, если величина образцового сигнала возрастает, т.е. N - признак направления;

f; - сигнал на i-ом выходе блока 7 управления (фиг.1,2).

Тогда получим следующие выражения для сигналов

, NVSiN;a; S, , 82 ; SjNVS, N ; f, g ; f, (vu)N )g, ; f j (VoJN) g, ; f( 5 «Jg, (V) g, ; f (coV-i ) g,; f g (J.)g,;

fg N.

Ha дополнительно введенном регистре и соответствующем цифро-аналоговом преобразователе запоминаетс предыдущее значение числового эквивлента и соответствующего образцового уровня, сравнение с которым позволяет быстро выявлять смену направления изменения сигнала и тем самым позволяет быстро изменять направление изменения образцового сигнала При этом, если в известном устройстве уменьшение шага квантования в два раза происходит при первой же смене ответа блока сравнения, то в предлагаемом устройстве уменьшение . шага происходит только при условии, что сигнал находится между предыдущим и текущим образцовыми уровнями, что значительно повышает вероятност правильного ответа и соответственно уменьшает погрешность преобразовани

Кроме того, блок разрешения удваивания шага в известном устройстве работает только на основании ответов блока сравнения, без учета значения текущего числового эквива-;лента .и значения скорости изменения образцового сигнала, хранящегося на распределителе импульсов, поэтому и возникает возможность выхода числового эквивалента за границы диапазона возможных изменений входн го сигнала,наличие логического блока устраняет опасность срыва процесса слежения. Устранить возможность выхода можно, если в блоке разрешения удваивания учитывать величину числового эквивалента и скорости изменения образцового сигнала. Так, в устройстве предлагается иметь обнуленными все разряды числового эквивалента более младшие, чем разряд, на который указывает распределитель импульсов.

Как уже отмечалось, регистр 12 служит только для запоминания предыдущего значения числового эквивалента и поэтому, если рассматривать образцовые уровни первого 2 и второго 11 ци1фроа налоговых преобразователей как границы некоторого отрезка, внутри которого находится входной сигнал, то на реверсивном счетчике 3 может храниться код как нижней, так и верхней границы отрезка. Как уже отмечалось, признаком направления является код. Если ,

Q то на реверсивном счетчике 3 - код верхней границы, если ,TO на реверсивном счетчике 3 - код нижней границы.

Следует отметить ,что как и в известном,в предлагаемом устройстве

5 в распределителе 6 импульсов з.апрещен сдвиг влево при коде 10 ...Си сдвиг вправо при коде 0...01 (не показано).

Устройство работает следующим образом.

Предположим, что сигнал начальной установки устанавливает признак N в , реверсивный счетчик 3 и распределитель юлпулъсов 6-в состояние

5 0...01, регистр - в состояние 0...0 (цепи начальной установки на фиг.1 не показаны). Так как вначале и при дальнейшей нормальнойработе триггеры переполнения реверсивного

Q счетчика 3 и регистра 12 находятся в нулевом состоянии, то первый 4 и второй 13 логические блоки пропус кают на свои выходы ответы блоков сравнения без инвертирования.

c Вначале казадого такта преобразования по сигналу f, с шестого выхода блока 7 управления происходит опрос блоков сравнения, сигналы от которых поступают на-второй и третий входы блока управления. В зависимости от ответов блоков, сравнения вырабатывается, во-первы5:, сигнал fj или fJ , переродящие соответственно реверсивный счетчик 3 в режим сложения или вычитания; во-вторых,

5 сигналы f-j или fg , производящие переписывание информации с реверсивного счетчика 3 на регистр 12 или наобрг рот; в третьих, сигналы fj или fg , производящие подготовку значения теQ кущего шага квантования, так по сигналу fg осуществляется сдвиг вправо содержимого распределителя 6 илшульсов, т.е. текущий шаг квантования уменьшается в два раза; по сигналу

f5 блок разрешения удваивания выдает сигнал сдвига влево в распределиг тель 6 импульсов, если в разряде реверсивного счетчика 3, на который указывает распределитель 6 импульсов, находится О.

0 Если же из-за большой скорости

изменения сигнала вблизи верхней границы диапазона произойдет переполнение реверсивного счетчика 3, т-, е. установится код 10...3(кодов больших

5 чем 10...О быть не может из-за используемого правила формирорания кодов), то из-за единичного состояния триггера переполнения первый логический блок 4 передает на свой выход проинвертированный сигнал первого блока сравнения, процесс же работы остальньлх блокрв преобразователя совпадает с описанным процессом. Так как при этом рассматриваемый код может быть переписан (по сигналу f ) в регистр 12, в последнем также предусмотрен разряд переполнения, а сигнал со второго блока 10 сравнения пропускается через второй логический блок 13, аналогичный первому логическому блоку 4.

Код, характеризующий величину сигнала, снимается с реверсивного счетчика 3. Определить, является ли этот код нижней или верхней границей отрезка, можно либо с помощьк признака N , либо с помощью кода, снимаемого с регистра 12. Код, снимаемый с расзпределителя б, импульсов, несет информацию о текущей скорости сигнала и о погретпности преобразования.

Формула изобретения

Следящий аналого-цифровой преобразователь по авт.св. 805489, отличающийся тем, что, с целью уменьшения погрешности преоразования, введены второй блок сравнения, второй цифро-аналоговый преобразователь, регистр, с дополнительным старшим разрядом переполнения, второй логический блок, вторая и третья группы элементов И,

причем первый вход второго блока сравнения соединен с выходом датчика входного сигнала, второй вход соединен с шестым вы содом блока управления и с третьим первого , блока сравнения, а третий вход сое;:. динен с выходом второго цифро-ангшогового преобразователя, цифровые входы которого соединены с выходами соответствующих разрядов регистра, выход вторюго блока сравнения соединен с первым входом второго логического блока, второй вход которого соединен с единичным выходом триггера переполнения регистра, а выход соединен с третьим входом блока управления, установочные входы разрядов регистра соединены с выходами второй группы, первые входы которых соединены с выходами соответствующих разрядов реверсивного счетчика

0 и со второй группой входов блока разрешения удваивания, третья группа входов которой соединена с выходами соответствующих разрядов распределителя импульсов, вторые входы

5 второй группы элементов И соединены с седьмым выходом блока управления, при этом выходы разрядов регистра соединены с первыми входами третьей группы элементов Н,вторые входы KOTOF DC соединены с восьмым выходом блока управления, а выходы соединены с установочными входами соответствующих разрядов реверсивного счетчика, девятый блока управления соединен с шиной Н .

5 Источники инфо1 юции,

принятые во внимание при экспертизе

1. Авторское свидетельство СССР 805489, кл. Н 03 К 13/02,08.09.79.

20

j0

11

| название | год | авторы | номер документа |

|---|---|---|---|

| Следящий аналого-цифровой преобразова-ТЕль | 1979 |

|

SU828401A1 |

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU907794A1 |

| Следящий аналого-цифровой преобразо-ВАТЕль | 1979 |

|

SU797064A1 |

| Следящий аналого-цифровой преобразователь | 1988 |

|

SU1580555A1 |

| Следящий аналого-цифровой преобразо-ВАТЕль | 1979 |

|

SU805489A1 |

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU900437A2 |

| Следящий аналого-цифровой преобразователь | 1983 |

|

SU1102031A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU824431A1 |

| Следящий аналого-цифровой преобразователь | 1979 |

|

SU799129A1 |

| Следящий аналого-цифровой преобразователь | 1980 |

|

SU892702A1 |

И

eput.Z

Авторы

Даты

1982-01-23—Публикация

1980-05-23—Подача