Пере Л. 6 ЗУ

Изобретение относится к вычислительной технике и предназначено для использования в случаях, когда информация с выхода буферного запоминающего устройства должна считываться в том же порядке, в каком она поступила на вход, и является усовершенствованием изобретения по авт. св. № 1399821.

Цель изобретения - расширение области применения устройства за счет возможности формирования сигнала переполнения буферного запоминающего устройства, если ранее записанная информация не использована.

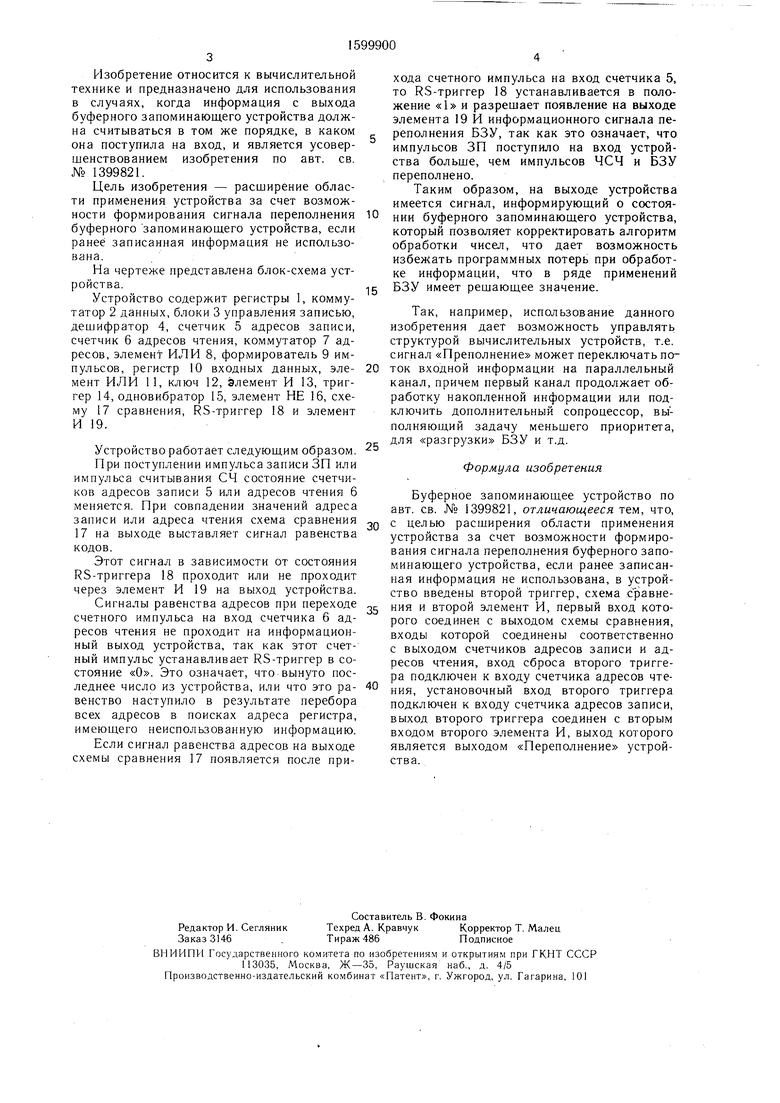

На чертеже представлена блок-схема устройства,

Устройство содержит регистры 1, коммутатор 2 данных, блоки 3 управления записью, дешифратор 4, счетчик 5 адресов записи, счетчик 6 адресов чтения, коммутатор 7 адресов, элемент ИЛИ 8, формирователь 9 импульсов, регистр 10 входных данных, эле- мент ИЛИ 11, ключ 12, Элемент И 13, триггер 14, одновибратор 15, элемент НЕ 16, схему 17 сравнения, RS-триггер 18 и элемент И 9.

Устройство работает следующим образом.

При поступлении импульса записи ЗП или импульса считывания СЧ состояние счетчиков адресов записи 5 или адресов чтения 6 меняется. При совпадении значений адреса записи или адреса чтения схема сравнения 17 на выходе выставляет сигнал равенства кодов.

Этот сигнал в зависимости от состояния RS-триггера 18 проходит или не проходит через элемент И 19 на выход устройства.

Сигналы равенства адресов при переходе счетного импульса на вход счетчика 6 адресов чтения не проходит на информационный выход устройства, так как этот счетный импульс устанавливает RS-триггер в состояние «О. Это означает, что вынуто последнее число из устройства, или что это ра- венство наступило в результате перебора всех адресов в поисках адреса регистра, имеющего неиспользованную информацию.

Если сигнал равенства адресов на выходе схемы сравнения 17 появляется после при

0

f.

0

5

0

0

хода счетного импульса на вход счетчика 5, то RS-триггер 18 устанавливается в положение «1 и разрешает появление на выходе элемента 19 И информационного сигнала переполнения БЗУ, так как это означает, что импульсов ЗП поступило на вход устройства больше, чем импульсов ЧСЧ и БЗУ переполнено.

Таким образом, на выходе устройства имеется сигнал, информирующий о состоянии буферного запоминающего устройства, который позволяет корректировать алгоритм обработки чисел, что дает возможность избежать программных потерь при обработке информации, что в ряде применений БЗУ имеет рещающее значение.

Так, например, использование данного изобретения дает возможность управлять структурой вычислительных устройств, т.е. сигнал «Преполнение может переключать поток входной информации на параллельный канал, причем первый канал продолжает обработку накопленной информации или подключить дополнительный сопроцессор, выполняющий задачу меньшего приоритета, для «разгрузки БЗУ и т.д.

Формула изобретения

Буферное запоминающее устройство по авт. св. № 1399821, отличающееся тем, что, с целью расширения области применения устройства за счет возможности формирования сигнала переполнения буферного запоминающего устройства, если ранее записанная информация не использована, в устройство введены второй триггер, схема сравнения и второй элемент И, первый вход которого соединен с выходом схемы сравнения, входы которой соединены соответственно с выходом счетчиков адресов записи и адресов чтения, вход сброса второго триггера подключен к входу счетчика адресов чтения, установочный вход второго триггера подключен к входу счетчика адресов записи, выход второго триггера соединен с вторым входом второго элемента И, выход которого является выходом «Переполнение устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1986 |

|

SU1399821A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Устройство для сопряжения электронных вычислительных машин | 1984 |

|

SU1257653A2 |

| Буферное запоминающее устройство | 1988 |

|

SU1583980A1 |

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1522220A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ БЫСТРОЙ СИНХРОНИЗАЦИИ В СИСТЕМАХ С ШУМОПОДОБНЫМИ СИГНАЛАМИ | 1989 |

|

SU1841074A1 |

| Устройство для ввода информации | 1987 |

|

SU1432544A1 |

| Буферное запоминающее устройство | 1981 |

|

SU1008793A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1444893A1 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

Изобретение относится к вычислительной технике. Буферное устройство целесообразно применять в различных микропроцессорных измерителях. Целью изобретения является расширение области применения за счет возможности формирования сигнала переполнения буферного запоминающего устройства, если ранее записанная информация не использована. Буферное устройство содержит регистры 1, счетчики адреса записи 5 и адреса чтения 6, коммутатор адреса 7, дешифратор 4, блоки управления записью 3, выходной коммутатор 2, формирователь импульсов 9, входной регистр 10, схему совпадения И 13, триггер 14, одновибратор 15, ключ 12 и схему ИЛИ 11. Новым является введение схемы сравнения 17, второго триггера 18 и второго элемента И 19 с соответствующими связями, которые при равенстве адресов записи и чтения (при условии, что счетчик чтения "догнал" счетчик записи) выдают информационный сигнал о переполнении буферного устройства. 1 ил.

| Буферное запоминающее устройство | 1986 |

|

SU1399821A1 |

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

Авторы

Даты

1990-10-15—Публикация

1989-03-23—Подача