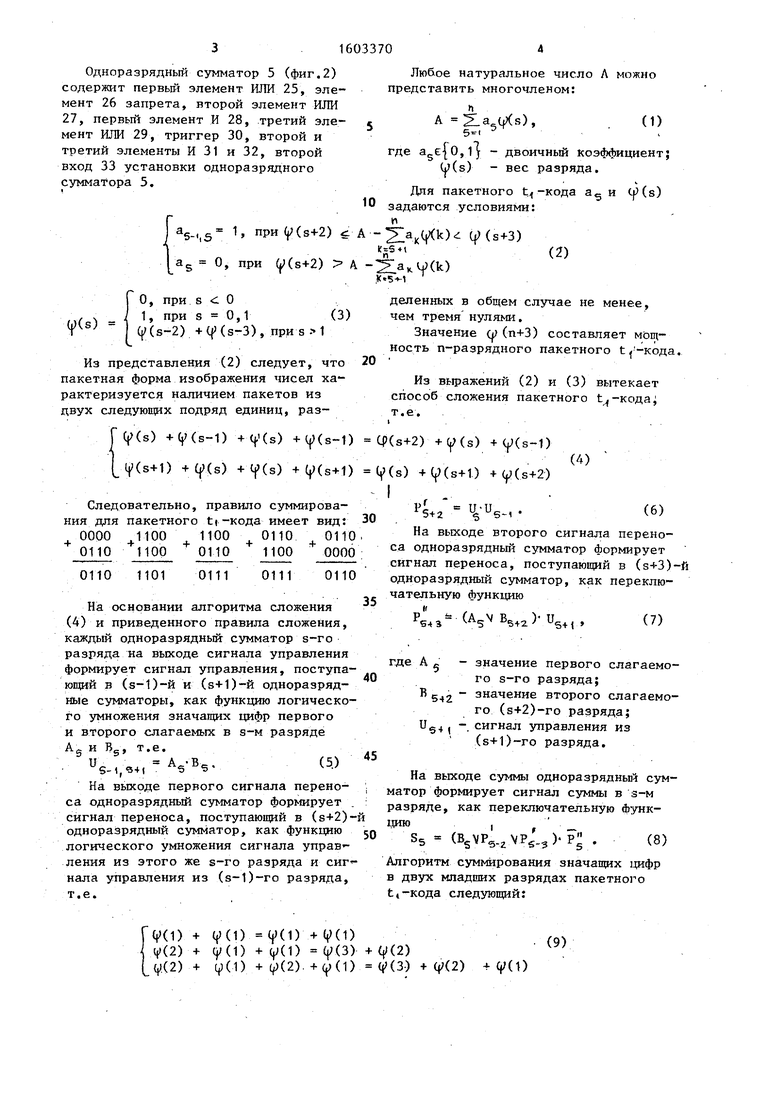

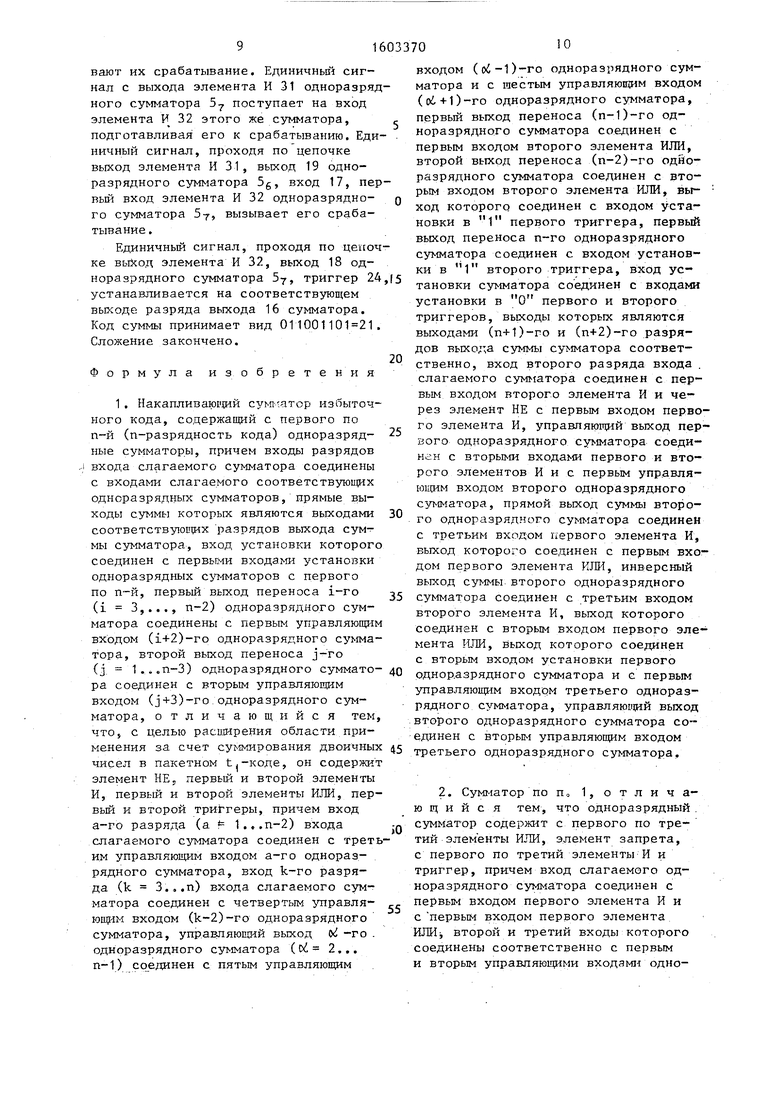

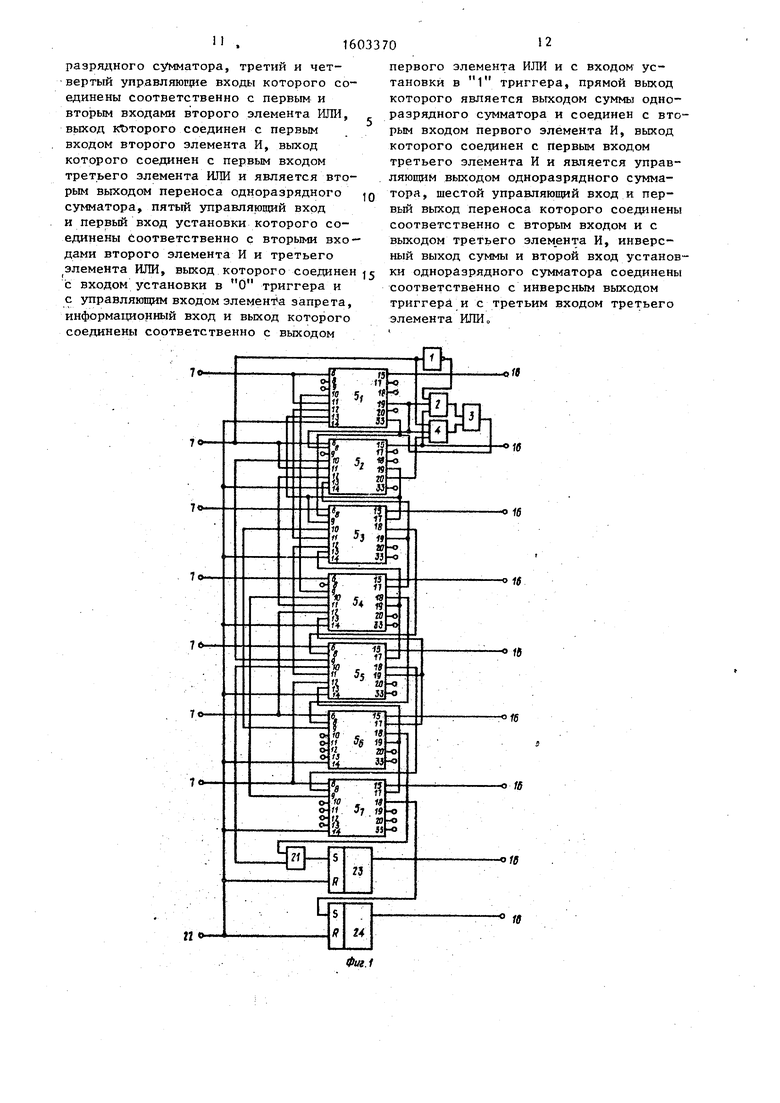

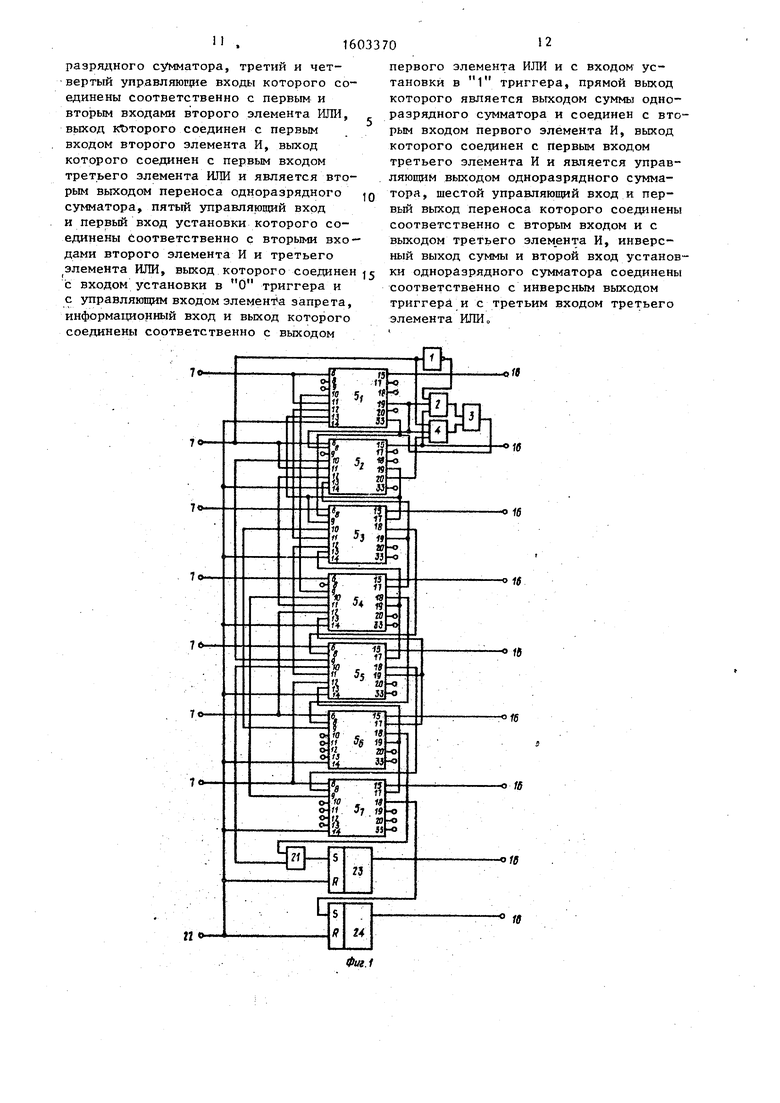

Одноразрядный сумматор 5 (фиг.2) содержит первьй элемент ИЛИ 25, элемент 26 запрета, второй элемент ИЛИ 27, первьш элемент И 28, .третий элемент ИЛИ 29, триггер 30, второй и третий элементы И 31 и 32, второй вход 33 установки одноразрядного сумматора 5.

Любое натуральное число Л можно представить многочленом:

А 2.3 tfXs),

5-1

(1)

10

где age|0,1y - двоичный коэффициент; (j(s) - вес разряда.

Для пакетного t -кода а и cp(s) задаются условиями:

S-,5 Ь при(;(з+2) А (k)i ( (s+3)

((2)

ag О, при ((s+2) А -21акЧ(и)

.К.

Любое натуральное число Л можно представить многочленом:

А 2.3 tfXs),

5-1

(1)

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор избыточного кода | 1987 |

|

SU1476460A1 |

| Накапливающий сумматор | 1988 |

|

SU1532916A1 |

| Сумматор избыточной минимальной системы счисления | 1988 |

|

SU1539768A1 |

| Накапливающий сумматор | 1991 |

|

SU1800454A1 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Последовательный сумматор | 1983 |

|

SU1149248A1 |

| Комбинационный сумматор | 1985 |

|

SU1310808A1 |

| Накапливающий сумматор | 1989 |

|

SU1702375A1 |

| Параллельный сумматор | 1981 |

|

SU1018114A1 |

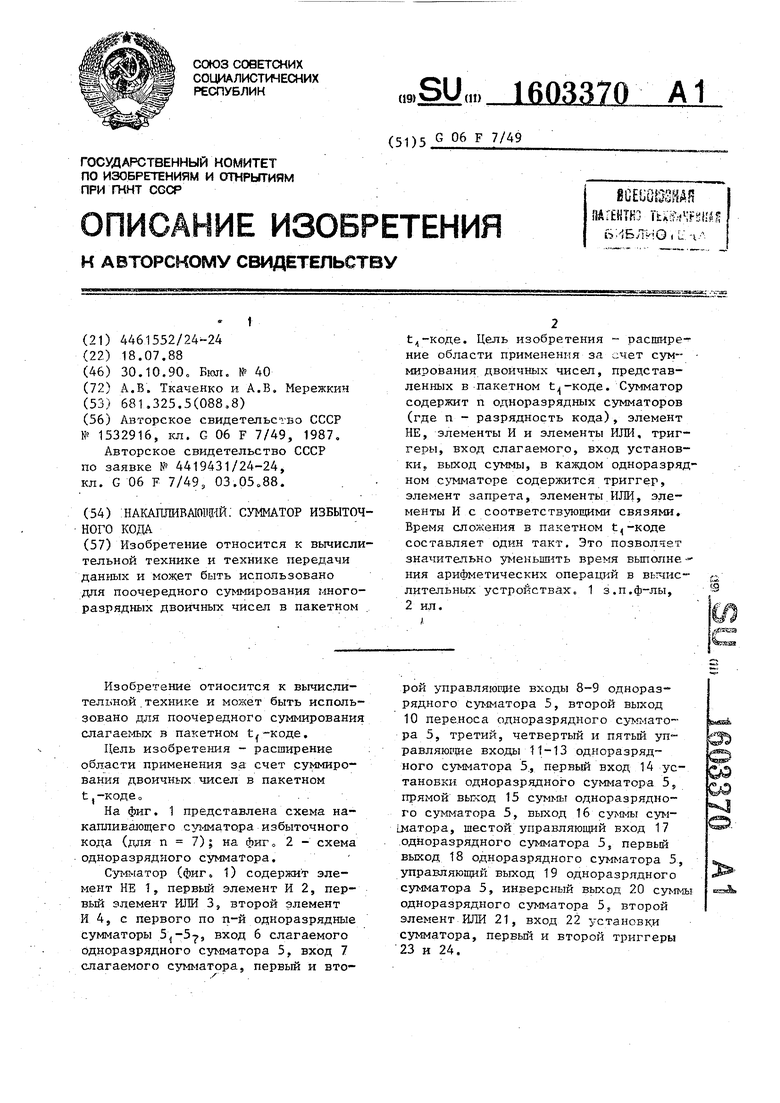

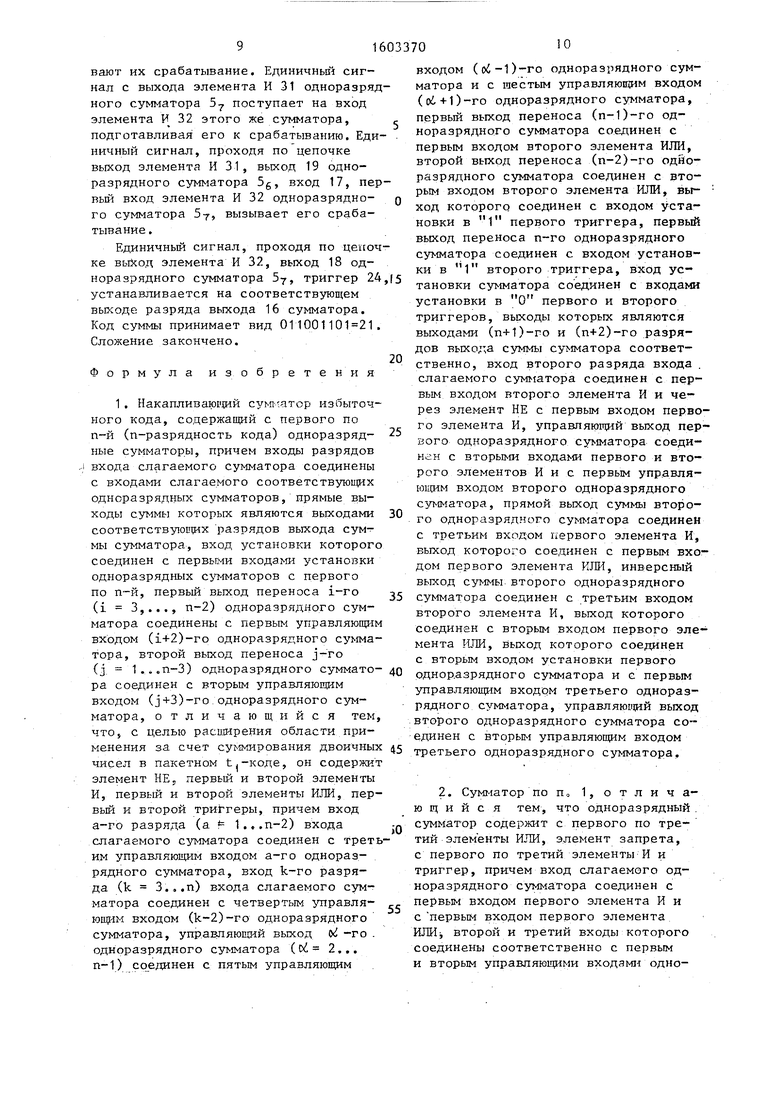

Изобретение относится к вычислительной технике и технике передачи данных и может быть использовано для поочередного суммирования многоразрядных двоичных чисел в пакетном T1-коде. Цель изобретения - расширение области применения за счет суммирования двоичных чисел, представленных в пакетном T1-коде. Сумматор содержит N одноразрядных сумматоров (где N - разрядность кода), элемент НЕ, элементы И и элементы ИЛИ, триггеры, вход слагаемого, вход установки, выход суммы, в каждом одноразрядном сумматоре содержится триггер, элемент запрета, элементы ИЛИ, элементы И с соответствующими связями. Время сложения в пакетном T1-коде составляет один такт. Это позволяет значительно уменьшить время выполнения арифметических операций в вычислительных устройствах. 1 з.п.ф-лы, 2 ил.

10, при S : О 1, при S 0,1 (3) C{;(s-2) +Cf (s-3),

Из представления (2) следует, что пакетная форма изображения чисел характеризуется наличием пакетов из двух следующих подряд единиц, раз-

(p(s) -KfKs-1) -t-(4s) qj(s+2) +((;(s) -t-(j;(s-i) I)(s4-1) -K|)(s) +t{ (s) +ф() ((s) -K(s+1) ((s+2)

Следовательно, правило суммирования для пакетного ti-кода имеет вид: 30

1100 1100 0110 1100 0110 1100

1101 0111 0111

+

0000 :

0110

На основании алгоритма сложения (4) и приведенного правила сложения, каждый одноразрядный сумматор s-ro разряда на выходе сигнала управления формирует сигнал управления, поступающий в (8-1)-й и (з+1)-й одноразрядные сумматоры, как функцию логического умножения значащих цифр первого и второго слагаемых в s-м разряде т.е.

Ад И Вд,

и.

(5)

S-1, 34(

На выходе первого сигнала перено- са одноразрядный сумматор формирует сигнал переноса, поступающий в (8+2)одноразрядный сумматор, как функцию логического умножения сигнала управления из этого же s-ro разряда и сиг нала управления из (s-l)-ro разряда, т.е.

ф(1) + ф(1) (|)(1) + V(1)

V(2) + yd) + (,J(1) (|;(3) + (1(2)

V.(2) + ф(1) + (;)(2).+((1) {|;(3-) + ф(2) -f-(;(O

т.е.

деленных в общем случае не менее, чем тремя нулями.

Значение q) (п+3) составляет мощность п-разрядного пакетного t -кода.

Из вьфажений (2) и (3) вытекает способ сложения пакетного t -кода;

(4)

(6)

На выходе второго сигнала переноса одноразрядный сумматор формирует сигнал переноса, поступающий в (з+3)-й одноразрядный сумматор, как переключательную функцию If

р - СА V R V б4а vA

и

5+1

(7)

В

где А 5 - значение первого слагаемого s-ro разряда; 542 значение второго слагаемого (s+2)-ro разряда; Ug , - сигнал управления из (s+1)-ro разряда.

На выходе суммы одноразрядньп- сумматор формирует сигнал суммы в з-м разряде, как переключательную функЦ™ . , Se (B,VP , VP, V Р . (8)

5 ( . Алгоритм суммирования значащих дафр в двух младших разрядах пакетного Ь,-кода следующий:

(9)

Следовательно, правило суммирования для двух младших разрядов пакетного t,-кода имеет вид:

00

n

10

но

п

fOO

10 +00

00

но

110

нос

110

ню

100

ню

11 11

вания четырех последовательно соединенных элементов 4 Т.

Предположим, необходимо сложить пакетные коды чисел 2 и 11.представленные следующим образом: Разряд № 1234567 Вес разряда 1 122345 Число 2 1100000 Число 11 1100011

Сущность изобретения состоит в рализации формул (4)-(9) для суммирования чисел, представленных в пакет ном t -кoдe.

Одноразрядные сумматоры 5 преднзначены для выработки сигнала суммы на выходе 15 при поочередном поступлении на его вход 6 значащих цифр двух слагаемых, а на входы 8 и 9 - первого и второго сигналов переноса из (s-2)-ro и (з-З)-го разрядов соответственно., выработки первого и второго сигналов переноса на выходах 18 и 10 в. (з+2)-й и ()-й разряды соответственно вьфаботкк сигнала управления на выходе 19 в (з-1)-й и (Б+О-Й разряды, хранения полученного значения суммы и установки в нуль.

Элемент ИЛИ 21 и триггеры 23 и 24 Q соответств -ющими связями предназначены для реализации алгоритма сложения пакетного t,-кода (4) в старших разрядах.

Элемент НЕ 1, элементы И 2 и 4 и элемент ИЛИ 3 с соответствуюпщми связями предназначены для реализагщи алгоритма сложения пакетного t.-кода (9) в двух младших разрядах.

Накапливающий сумматор (фиг,1) работает следующим образом.

После подачи на установочный вход 22 единичного сигнала сумматор устанавливается в исходное состояние

Коды первого и второго слагаемых подаются на вход 7 сумматора поочередно, в виде семиразрядных двоичных чисел в пакетном t,-кoдe в течение времени с, равного времени срабаты-

1603370

20

10

Пакетный код первого слагаемого числа 2 подается на вход 7 сумматора, единичные сигналы с первого и второго разрядов слагаемых, проходя по цепочке вход 6, элемент УЛК 25, элемент 26 запрета, триггер 30, выход 15 одноразрядных сумматоров 5/ и 52, устанавливаются на соответ- ствхтопщх выходах разрядов выхода 16 сумматора, т.е. происходит обычная запись кода числа 2.

Затем на вход 7 сумматора подается пакетный код второго слагаемого - J5 числа 11. Единичный сигнал с второго разряда, проходя через вход 6, поступает на первый вход элемента И 31 одноразрядного сумматора 5, вызывая его срабатывание. Единичный сигнал с выхода элемента И 31 проходит через выход 19 одноразрядного су гматора 5 по цепочке: вход 6; элемент ИЛИ 25; элемент 26 запрета; триггер 20; выход 15 одноразрядного 25 сумматора 5 и устанавливается на соответствующем выходе разряда выхода 16 сумматора.

Одновременно единичные сигналы с шестого и седьмого разрядов второго слагаемого, проходя по цепочке вход 6,,элемент ИЛИ 25. элемент 26 запрета, триггер 30, вькод 15 одноразрядных сумматоров 5g и 5-,,, устанавливаются на соответств ующих выходах разрядов выхода 16 сумматора. Код результата сложения принимает вид 111001100 13. Сложение закончено.

Предположим, необходимо сложить пакетньш коды чисел 8 и 6, ставленные следующим образом:

0

5

0

пред

1234567 1 122345 1001100 10001 10

Cyi.iMaTop приводится в исходное состояние.

Первое слагаемое (пакетный код

числа 6) подается на вход 7 сумматора, единичные сигналы с первого, четвертого и пятого разрядов слагаемого, проходя по цепочке вход 6, элемент ИЛИ 25, элемент 26 запрета, : триггер 30, 15 одноразрядных

сумматоров 5(, 54 и 5, устанавливаются на соответствуюп нх выходах разрядов выхода 16 сумматора. Затем на вход 7 сумматора, подается пакетный

код числа 8. Единичный сигнал из первого разряда поступает через вход 6 на первьп вход элемента И 31 одноразрядного сумматора 5 и вызывает его срабатывание. Единичный сигнал с выхода элемента И 31 проходит через выход 19 одноразрядного сумматора 5, поступает на одноразрядный сумматор

Первое слагаемое (пакетный код числа 11) подается на вход 7 сумматора. Единичные сигналы из первого, второго, шестого и седьмого разрядов, проходя по цепочке вход 6,

5 и, проходя по цепочке вход 6, эле- ю элемент ИЛИ 25, элемент 26 запрета, мент РШИ 25, элемент 26 запрета, триг- триггер 30, выход 15 одноразрядных гер 30, выход 15, устанавливается на сумматоров 5,, 5л, 5g и 5, соответ- соответствующем выходе разряда выхода 16 сумматора. Одновременно единичный

15

сигнал из шестого разряда, проходя по цепочке вход 6, элемент ИЛИ 25, элемент 26 запрета, триггер 30, выход 15 одноразрядного сумматора 5g , устанавливается на соответствующем выходе разряда выхода 16 сумматора, единичный сигнал из шестого разряда, проходя по цепочке вход 12, элемент ИЛИ 27, первый вход элемента И 28 од1 оразрядного сумматора 5, подго- . тавливает его к срабатыванию.

Одновременно единичный сигнал из пятого разряда проходит черея вход 6, элемент И 31, устанавливается на выходе 19 одноразрядного сумматора 5 и далее поступает через вход 13 на второй вход элемента И 28 одноразрядного сз мматора 5,, вызывает его .срабатывание, единичный сигнал с выхода элемента И 28 проходит через элемент ИЛИ 29 на вход установки в нуль триггера 30 и управляющий вход элемента 26 запрета, при этом триггер 30 устанавливается в нулевое состояние, стирая значения предыдущего слагаемого в четвертом разряде. Еди- ничньм сигнал с выхода элемента И 28 одноразрядного сумматора 5 является вторым сигналом переноса и, поступая через выход 10 на цепочку-вход 9, элемент ИЛИ 25, элемент 26 запрета, триггер 30, выход 15 одноразрядного сумматора 5, устанавливается на соответствующем выходе разряда выхода 16 сумматора. Код суммы принимает вид: 110011100 14. Сложение закончено.

Предположим, необходимо сложить пакетные коды чисел 11 и 10, представленные в пакетной форме сле- дуюрщм образом: Разряд №1234567 .

Вес разряда 1122345 Число 11 1100011 Число 10 1000011

20

ственно, устанавливается на соответ- ствуюиих выходах разрядов выхода 16 сумматора, единичные сигналы с прямых выходов триггеров 30 устанавливаются на вторых входах элементов И 31 одноразрядных сумматоров 5, 5 и 5, подготавливая их к срабатыванию, кроме того, единичный сигнал устанавливается на одном входе элемента :И 2 с выхода 15 одноразрядного сумматора 5. Затем на вход 7 сумматора подается пакетный код числа 25 10. Нулевой сигнал с второго разряда, проходя через элемент НЕ 1, инвертируется и единичный сигнал с выхода элемента НЕ 1 поступает на другой вход элемента И 2, подготавливая его к срабатыванию. Единичный сигнал из первого разряда, проходя по цепочке вход 6, элемент И 31, выход 19 одноразрядного сумматора 5., поступает на вход элемента И 2, вызывая его срабатывание. Единичный сигнал с выхода элемента И 2, проходя через элемент ИЛИ 3, поступает на вход 33 и вход 8 одноразрядных сумматоров 5, и 5з соответственно. Единич30

35

40

ный сигнал с входа 33 одноразрядного сумматора 5 поступает через элемент ИЛИ 29 на вход установки в нуль триггера 30, триггер 30 устанавливается в нулевое состояние и нулевой сигнал

45 через выход 15 одноразрядного сумматора 5 устанавливается на соответствующем выходе разряда выхода 16 сумматора ,

Единичный сигнал с входа 8 одноgQ разрядного сумматора 5, проходя . по цепочке элемент ИЛИ 25, элемент 26 запрета, триггер 30, выход 15 одноразрядного сумматора 5j, устанавливается на соответствующем вьжоде разряда выхода 16 сумматора, Одновр е- менно единичные сигналы из шестого :И седьмого разрядов, проходя по цепочке вх д 6, выход элемента И 31 одноразрядных сумматоров 5 g и 5, вызы55

Подачей единичного сигнала на вход 22 сумматор обнуляется, т.е. приводится в исходное состояние.

Первое слагаемое (пакетный код числа 11) подается на вход 7 сумматора. Единичные сигналы из первого, второго, шестого и седьмого разрядов, проходя по цепочке вход 6,

элемент ИЛИ 25, элемент 26 запрета, триггер 30, выход 15 одноразрядных сумматоров 5,, 5л, 5g и 5, соответ-

ю элемент ИЛИ 25, элемент 26 запрета, триггер 30, выход 15 одноразрядных сумматоров 5,, 5л, 5g и 5, соответ-

5

0

ственно, устанавливается на соответ- ствуюиих выходах разрядов выхода 16 сумматора, единичные сигналы с прямых выходов триггеров 30 устанавливаются на вторых входах элементов И 31 одноразрядных сумматоров 5, 5 и 5, подготавливая их к срабатыванию, кроме того, единичный сигнал устанавливается на одном входе элемента :И 2 с выхода 15 одноразрядного сумматора 5. Затем на вход 7 сумматора подается пакетный код числа 5 10. Нулевой сигнал с второго разряда, проходя через элемент НЕ 1, инвертируется и единичный сигнал с выхода элемента НЕ 1 поступает на другой вход элемента И 2, подготавливая его к срабатыванию. Единичный сигнал из первого разряда, проходя по цепочке вход 6, элемент И 31, выход 19 одноразрядного сумматора 5., поступает на вход элемента И 2, вызывая его срабатывание. Единичный сигнал с выхода элемента И 2, проходя через элемент ИЛИ 3, поступает на вход 33 и вход 8 одноразрядных сумматоров 5, и 5з соответственно. Единич0

5

0

ный сигнал с входа 33 одноразрядного сумматора 5 поступает через элемент ИЛИ 29 на вход установки в нуль триггера 30, триггер 30 устанавливается в нулевое состояние и нулевой сигнал

5 через выход 15 одноразрядного сумматора 5 устанавливается на соответствующем выходе разряда выхода 16 сумматора ,

Единичный сигнал с входа 8 одноQ разрядного сумматора 5, проходя . по цепочке элемент ИЛИ 25, элемент 26 запрета, триггер 30, выход 15 одноразрядного сумматора 5j, устанавливается на соответствующем вьжоде разряда выхода 16 сумматора, Одновр е- менно единичные сигналы из шестого :И седьмого разрядов, проходя по цепочке вх д 6, выход элемента И 31 одноразрядных сумматоров 5 g и 5, вызы5

вают их срабатывание. Единичньш сигнал с выхода элемента И 31 одноразрядного сумматора 5 поступает на вход элемента И 32 этого же сумматора, подготавливая его к срабатыванию. Еди- ничный сигнал, проходя по цепочке вьгход элемента И 31, вькод 19 одноразрядного сумматора 5g, вход 17, первый вход элемента И 32 одноразрядно- го сумматора 5-f, вызывает его срабатывание .

Единичный сигнал, проходя по цепочке вьйсод элемента И 32, выход 18 одноразрядного сумматора Зу, триггер 24, устанавливается на соответствующем выходе разряда выхода 16 сумматора. Код суммы принимает вид 011001101 21. Сложение закончено.

Формула изобретения

что, с целью расиирения области применения за счет суг мирования двоичных чисел в пакетном t -коде, он содержит элемент НЕ„ первый и второй элементы И, первый и второй элементы ИЛИ, пер- вьй и второй триггеры, причем вход а-го разряда (а 1...П-2) входа слагаемого сумматора соединен с третьим управляющим входом а-го однораз- . рядного сумматора, вход k-ro разряда (k З.,.п) входа слагаемого сумматора соединен с четвертым управляющим входом (k-2)-ro одноразрядного сумматора, управляющий выход (Xi -го . одноразрядного сумматора (od 2... п-1) сое;щнен с пятым управляющим

с. Q

(5

03370 О

входом (oi-l)-ro одноразрядного сумматора и с шестым управляю1цим входом (oi+1)-ro одноразрядного сумматора, первый выход переноса (п-1)-го одноразрядного сумматора соединен с первым входом второго элемента HJHi, второй выход переноса (п-2)-го одноразрядного сумматора соединен с вторым входом второго элемента ИЛИ, вы- ход которого соединен с входом установки в 1 первого триггера, первый выход переноса п-го одноразрядного сумматора соединен с входом установки в 1 второго триггера, вход установки сумматора соединен с входами установки в О первого и второго триггеров, выходы которых являются выходами (п+1)-го и (п+2)-го разрядов выхода суммы сумматора соответственно, вход второго разряда входа . слагаемого сумматора соединен с пер- вьм входом второго элемента И и через элемент НЕ с первым входом первого элемента И, управляющий выход первого одноразрядного сумматора соеди- нгн с вторыми входами первого и второго элементов И и с первым упрдвля- юнщм входом второго одноразрядного сумматора, прямой выход суммы второго одноразрядного сумматора соединен с третьим входом riepBoro элемента И, выход которого соединен с первым входом первого элемента ИЛИ, инверсный выход суммы второго одноразрядного сумматора соединен с третьим вх-одом второго элемента И, выход которого соединен с вторым входом первого элемента ИЛИ, выход которого соединен с вторым входом установки первого одноразрядного сумматора и с первым управляющим входом третьего одноразрядного сумматора, управляющий выход второго одноразрядного сумматора со единен с вторым управляющим входом третьего одноразрядного сумматора.

20

25

30

35

40

45

элемента ИЛИ, выход которого соединен с входом установки в О триггера и с управляющим входом элементна запрета, информационный вход и выход которого соединены соответственно с выходом

первого элемента ИЛИ и с входом установки в 1 триггера, прямой вькод которого является выходом суммы одноразрядного сумматора и соединен с вторым входом первого элемента И, выход которого соединен с первым входом третьего элемента И и является управляющим выходом одноразрядного сумматора, шестой управляющий вход и. первый выход переноса которого соединены соответственно с вторым входом и с выходом третьего элемента И, инверсный выход суммы и второй вход установки одноразрядного сумматора соединены соответственно с инверсным выходом триггерами с третьим входом третьего элемента ИЛИ

Фиг. г

Авторы

Даты

1990-10-30—Публикация

1988-07-18—Подача