Јь

ОЭ ОЭ

о

| название | год | авторы | номер документа |

|---|---|---|---|

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Накапливающий сумматор избыточного кода | 1988 |

|

SU1603370A1 |

| Параллельный сумматор | 1986 |

|

SU1363188A1 |

| Сумматор последовательного действия | 1989 |

|

SU1689945A2 |

| Устройство для умножения | 1979 |

|

SU773622A1 |

| КОМБИНАЦИОННЫЙ СУММАТОР СТРУКТУРНЫХ КОДОВ | 1991 |

|

RU2023288C1 |

| Устройство для суммирования Фибоначчи-десятичных кодов | 1989 |

|

SU1649535A1 |

| Комбинационный сумматор | 1985 |

|

SU1310808A1 |

| Комбинационный сумматор | 1986 |

|

SU1327092A1 |

| Сумматор кодов фибоначчи | 1976 |

|

SU732864A1 |

Изобретение предназначено для построения сверхбыстродействующих самоконтролирующихся микропроцессоров. Изобретение позволяет расширить область применения сумматора путем суммирования чисел, представленных в избыточной пакетной системе счисления. Сумматор избыточного кода содержит полусумматор 1, элементы ИЛИ 2,3, элементы И 4,13,14, одноразрядные сумматоры 5-6, каждый из которых состоит из элементов ИЛИ, элементов И, элемента 1 запрета. 1 з.п. ф-лы, 2 ил.

.,

11

Изобретение относится к автоматике и вычислительной технике и может быть использовано в специализированных вычислительных машинах для параллельного суммирования многоразрядных двоичных чисел.

Целью изобретения является расширение области применения та счет суммирования пакетных кодов.

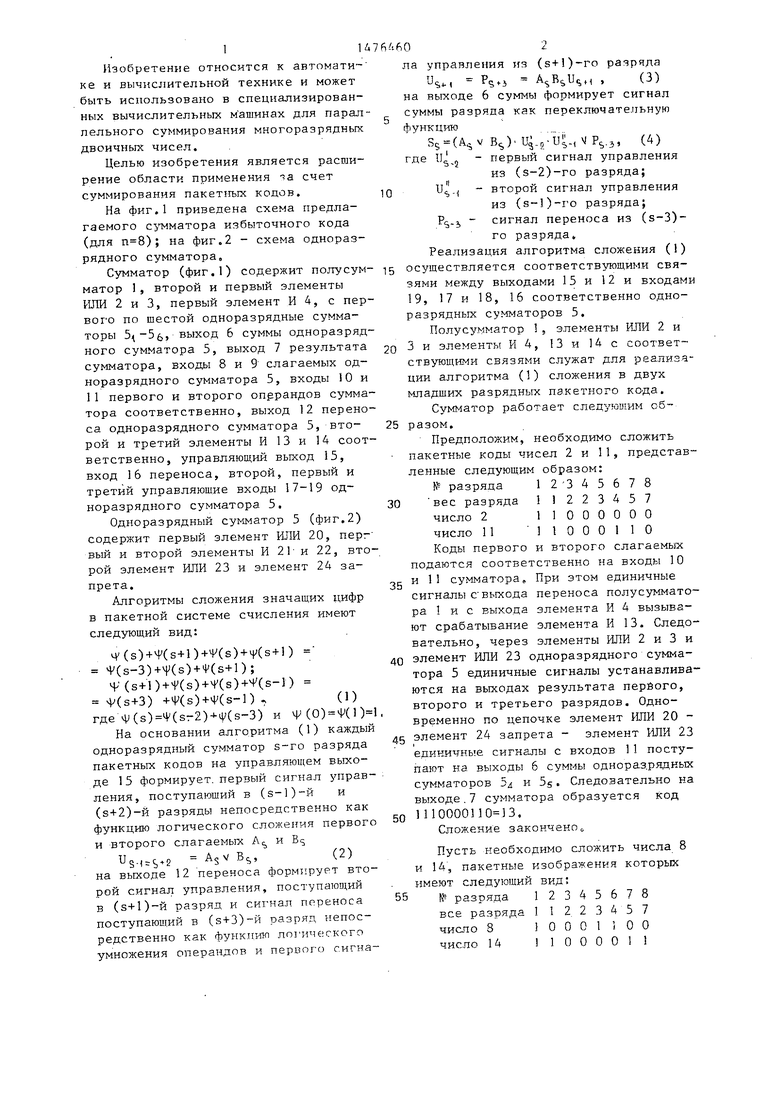

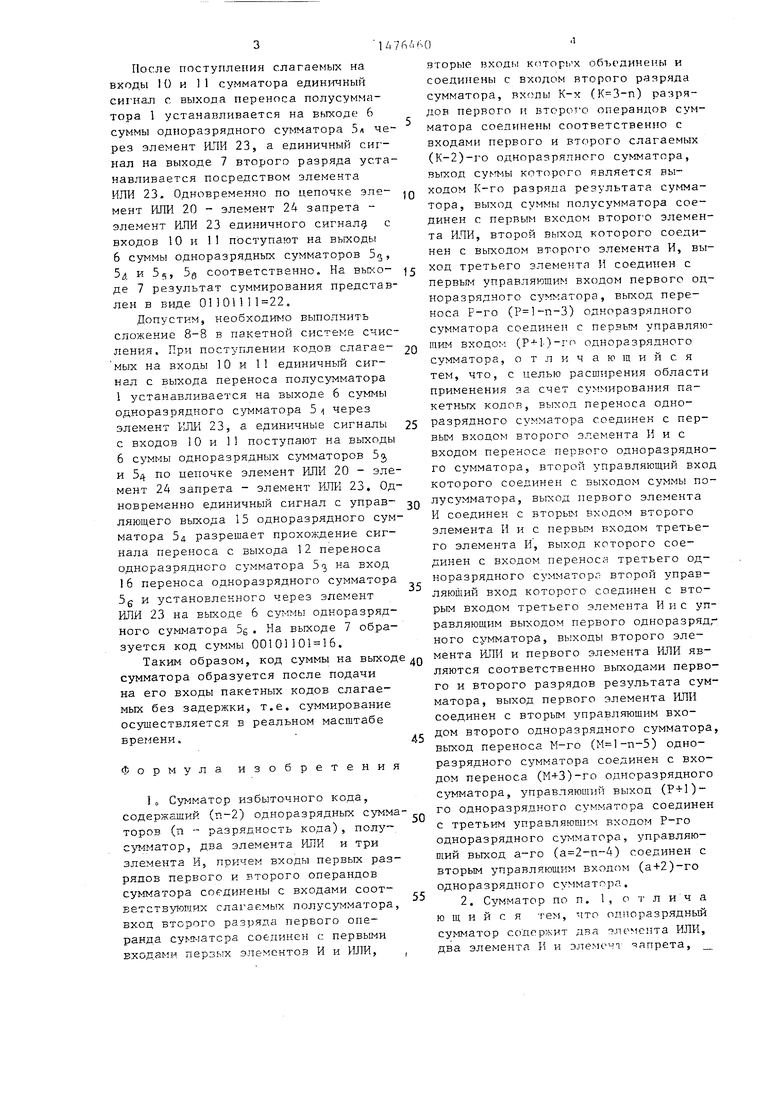

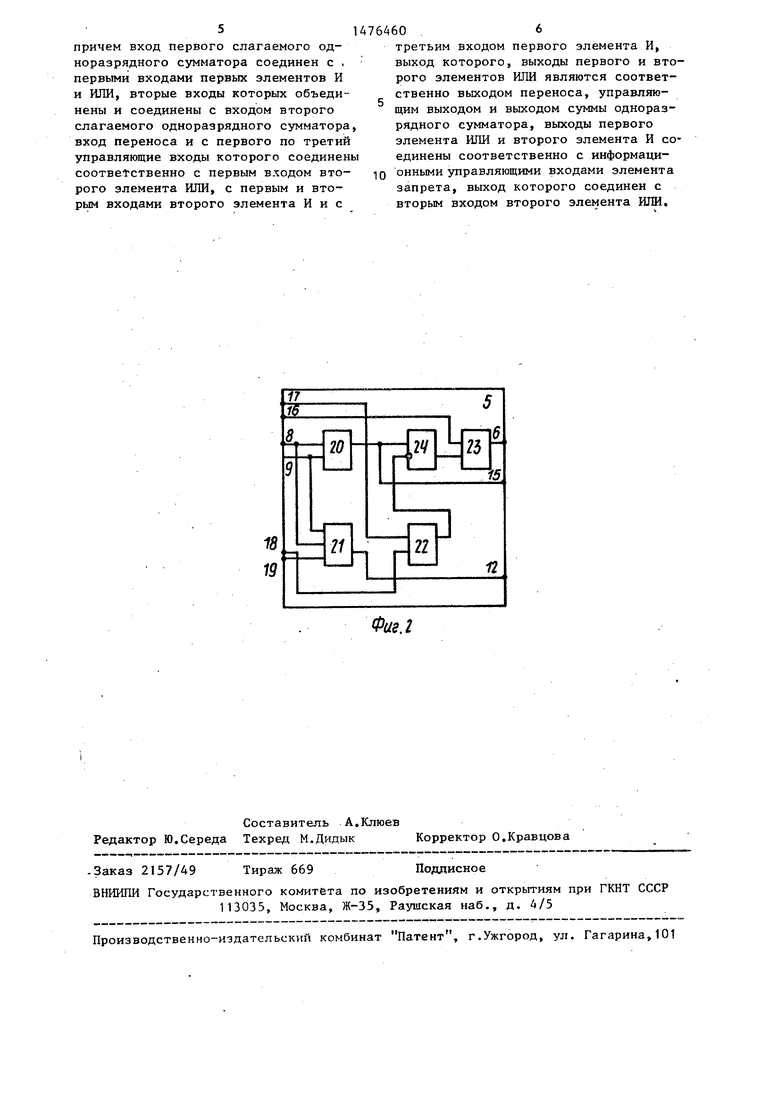

На фиг.1 приведена схема предлагаемого сумматора избыточного кода (для ); на фиг.2 - схема одноразрядного сумматора.

Сумматор (фиг.1) содержит полусумматор 1, второй и первый элементы ИЛИ 2 и 3, первый элемент И 4, с первого по шестой одноразрядные сумматоры ,, выход 6 суммы одноразрядного сумматора 5, выход 7 результата сумматора, входы 8 и 9 слагаемых одноразрядного сумматора 5, входы 10 и 11 первого и второго операндов сумматора соответственно, выход 12 переноса одноразрядного сумматора 5, второй и третий элементы И 13 и 14 соответственно, управляющий выход 15, вход 16 переноса, второй, первый и третий управляющие входы 17-19 одноразрядного сумматора 5,

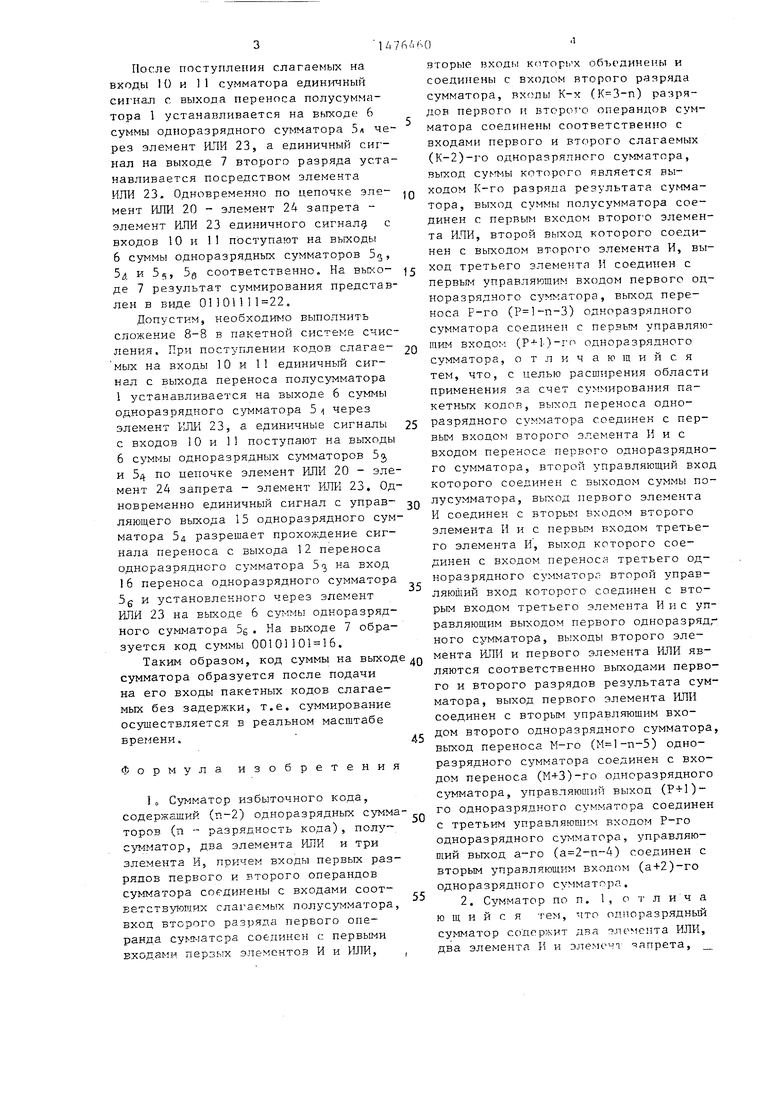

Одноразрядный сумматор 5 (фиг.2) содержит первый элемент ИЛИ 20, перг вый и второй элементы И 21 и 22, второй элемент ИЛИ 23 и элемент 24 запрета.

Алгоритмы сложения значащих цифр в пакетной системе счисления имеют следующий вид:

vV(s)+S4s + l)+V(s) + v(s + l) 4;(s-3)+H;(s) + lV(s+l);

Н- (s+l)+f(s)+4 (s)+4;(s-l) 44s+3) +H4s)+Y(s-l) (О где V(s)44sr2) + 4(s-3) и V (0) f(l )

На основании алгоритма (1) каждый одноразрядный сумматор s-ro разряда пакетных кодов на управляющем выходе 15 формирует первый сигнал управления, поступающий в (з-1)-й и (з+2)-й разряды непосредственно как функцию логического сложения первого и второго слагаемых AS и 1Ц

U

АО V

Ч

(2)

на выходе 12 переноса формирует второй сигнал управления, поступающий в (з+1)-й разряд и сигнал переноса поступающий в (з+3)-й оазряд непосредственно как функцию логического умножения операндов и первого гигва764602

па управления из (s+l)-ro разряда

US,M AsBsu i , (3) на выходе 6 суммы формирует сигнал суммы разряда как переключательную функцию

S5(Asv Bs)-UЈ.p-Ui:., VPS3, (4) где - первый сигнал управления из (s-2)-ro разряда;

и:

- второй сигнал управления

из (s-l)-ro разряда; Рс,,5, - сигнал переноса из (з-З)го разряда

Реализация алгоритма сложения () 5 осуществляется соответствующими связями между выходами 15 и 12 и входами 19, 17 и 18, 16 соответственно одноразрядных сумматоров 5.

Полусумматор 1, элементы ИЛИ 2 и о 3 и элементы И 4, 13 и 14 с соответствующими связями служат для реализации алгоритма (1) сложения в двух младших разрядных пакетного кода.

Сумматор работает следующим сб- 5 разом.

Предположим, необходимо сложить пакетные коды чисел 2 и 11, представленные следующим образом:

№ разряда 1 2 3 4 5 6 7 8 0 вес разряда 1 1 223457 число 2 11000000 число 11 11000110 Коды первого и второго слагаемых подаются соответственно на входы 10 с и 11 сумматора. При этом единичные сигналы с выхода переноса полусумматора 1 и с выхода элемента И 4 вызывают срабатывание элемента И 13. Следовательно, через элементы ИЛИ 2 и 3 и 0 элемент ИЛИ 23 одноразрядного сумматора 5 единичные сигналы устанавливаются на выходах результата первого, второго и третьего разрядов. Одновременно по цепочке элемент ИЛИ 20 - 5 элемент 24 запрета - элемент ИЛИ 23 единичные сигналы с входов 11 поступают на выходы 6 суммы одноразрядных сумматоров 5л и 5s. Следовательно на выходе.7 сумматора образуется код 0 1110000130 13.

Сложение закончено„

Пусть необходимо сложить числа 8 и 14Э пакетные изображения которых имеют следующий вид: 5 № разряда 12345678 все разряда 1 1 223457 число 3 10001100 число 14 1 1 О О О О 1 1

314

После поступления слагаемых на входы 10 и 11 сумматора единичный сигнал с выхода переноса полусумматора 1 устанавливается на выходе 6 суммы одноразрядного сумматора 5л через элемент ИЛИ 23, а единичный сигнал на выходе 7 второго разряда устанавливается посредством элемента ИЛИ 23, Одновременно по цепочке эле- мент ИЛИ 20 - элемент 24 запрета - элемент ИЛИ 23 единичного сигналу с входов 10 и 11 поступают на выходы 6 суммы одноразрядных сумматоров 5 5д и 5«5, соответственно. На выхо- де 7 результат суммирования представлен в виде 01101111 22.

Допустим, необходимо выполнить сложение 8-8 в пакетной системе счисления. При поступлении кодов слагае- мых на входы 10 и 11 единичный сигнал с выхода переноса полусумматора 1 устанавливается на выходе 6 суммы одноразрядного сумматора 5 ц через элемент ИЛИ 23, а единичные сигналы с входов 10 и 11 поступают на выходы 6 суммы одноразрядных сумматоров 5о, и 5 по цепочке элемент ИЛИ 20 - элемент 24 запрета - элемент ИЛИ 23, Одновременно единичный сигнал с управ- ляющего выхода 15 одноразрядного сумматора 54 разрешает прохождение сигнала переноса с выхода 12 переноса одноразрядного сумматора 5т, на вход 16 переноса одноразрядного сумматора 5g и установленного через элемент ИЛИ 23 на выходе 6 суммы одноразрядного сумматора 5g. На выходе 7 образуется код суммы 00101101 16.

Таким образом, код суммы на выходе сумматора образуется после подачи на его входы пакетных кодов слагаемых без задержки, т.е. суммирование осуществляется в реальном масштабе времени,

Формула изобретения

1 о Сумматор избыточного кода, содержащий (п-2) одноразрядных сумма- торов (п -- разрядность кода), полусумматор, два элемента ИЛИ и три элемента И, причем входы первых разрядов первого и второго операндов сумматора сординены с входами соответствующих слагаемых полусумматора, вход второго разряда первого операнда сумматора соединен с первыми входами перзь-х эпементов И и ИЛИ, ,

Q 5

0 Q

Q 5

5

,()-1

вторые входы которых объединены и соединены с входом второго разряда сумматора, входы К-х () разрядов первого и второго операндов сумматора соединены соответственно с входами первого и второго слагаемых (К-2)-го одноразрядного сумматора, выход суммы которого является выходом К-го разряда результата сумматора, выход суммы полусумматора соединен с первым входом второго элемента ИЛИ, второй выход которого соединен с выходом второго элемента И, выход третьего элемента И соединен с первым управляющим входом первого одноразрядного сумматора, выход переноса Р-го (Р 1-п-3) одноразрядного сумматора соединен с первь м управляющим входом (Р-М)-гп одноразрядного сумматора, отличающийся тем, что, с целью расширения области применения за счет суммирования пакетных кодов, выход переноса одноразрядного сумматора соединен с первым входом второго элемента И и с входом переноса первого одноразрядного сумматора, второй управляющий вход которого соединен с выходом суммы полусумматора, выход первого элемента И соединен с вторым входом второго элемента И и с первым входом третьего элемента И, выход которого соединен с входом переноса третьего одноразрядного сумматора второй управляющий вход которого соединен с вторым входом третьего элемента И и с управляющим выходом первого одноразрядного сумматора, выходы второго элемента ИЛИ и первого элемента ИЛИ являются соответственно выходами первого и второго разрядов результата сумматора, выход первого элемента ИЛИ соединен с вторым управляющим входом второго одноразрядного сумматора, выход переноса 5-го (М 1-п-5) одноразрядного сумматора соединен с входом переноса (М+3)-го одноразрядного сумматора, управляющий выход (Р-И) го одноразрядного сумматора соединен с третьим управляющим входом Р-го одноразрядного сумматора, управляющий выход а-го (а 2-п-4) соединен с вторым управляющим входом (а+2)-го одноразрядного сумматора.

51

причем вход первого слагаемого одноразрядного сумматора соединен с , первыми входами первых элементов И и ИЛИ, вторые входы которых объединены и соединены с входом второго слагаемого одноразрядного сумматора, вход переноса и с первого по третий управляющие входы которого соединены соответственно с первым входом второго элемента ИЛИ, с первым и вторым входами второго элемента И и с

764606

третьим входом первого элемента И, выход которого, выходы первого и второго элементов ИЛИ являются соответственно выходом переноса, управляющим выходом и выходом суммы одноразрядного сумматора, выходы первого элемента ИЛИ и второго элемента И соединены соответственно с информаци- 10 онными управляющими входами элемента запрета, выход которого соединен с вторым входом второго элемента ИЛИ.

Фиг.I

Авторы

Даты

1989-04-30—Публикация

1987-10-22—Подача