Изобретение относится к области автоматики и вычислительной техники, в частности к устройствам для управления выдачей команд и может быть использовано при построении устройства выдачи команд и программного контроля их исполнения в специализированных вычислительных и многофункциональных управляющих системах.

Цель изобретения - повышение достоверности выдачи команд за счет исключения возможности набора последующей команды до окончания выдачи предыдущей и дискретного исполнения команды с контролем и корректировкой ее выполнения.

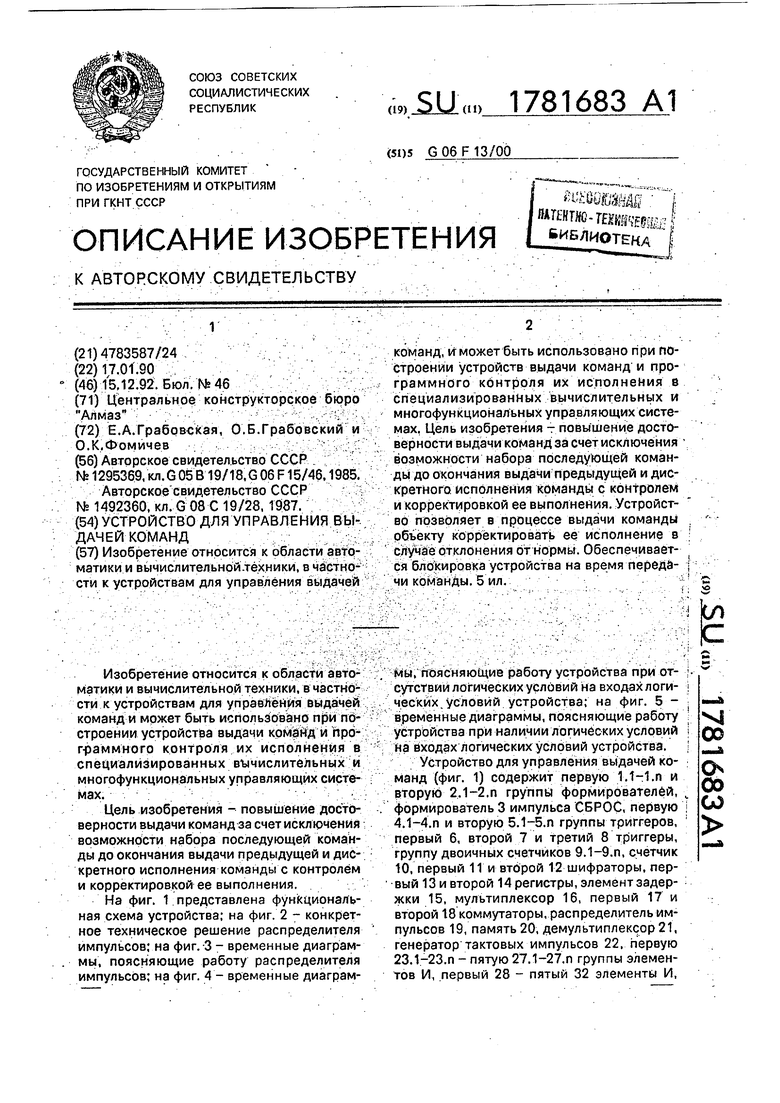

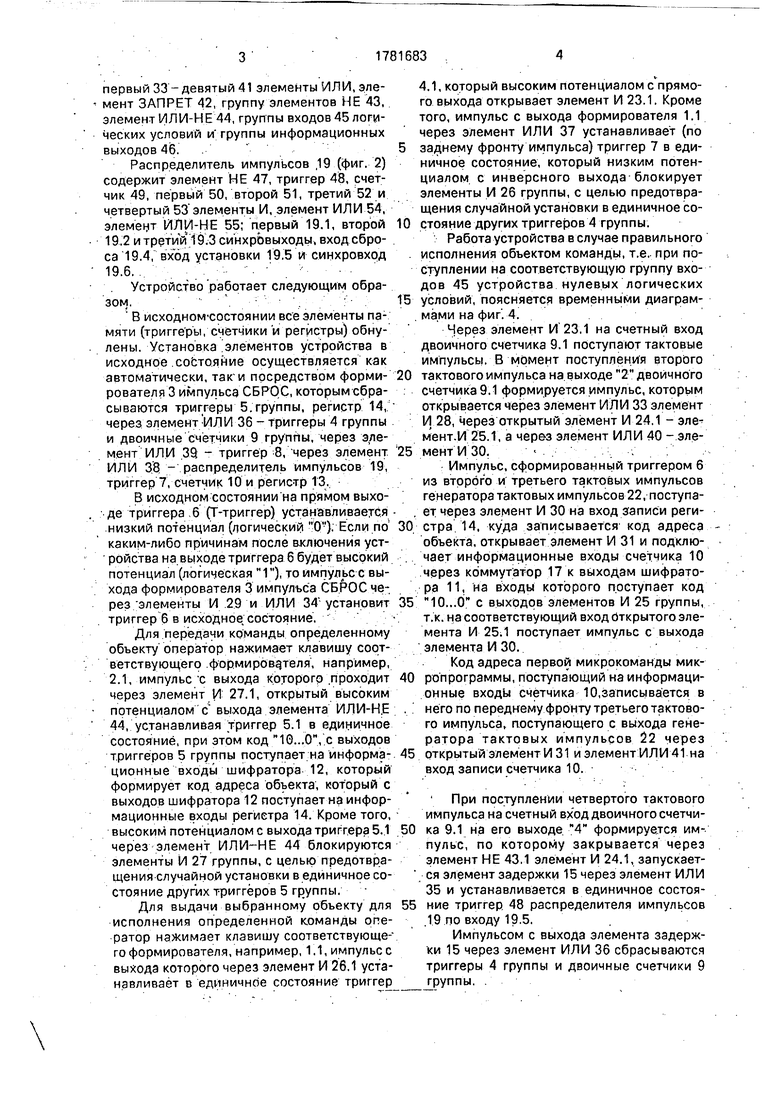

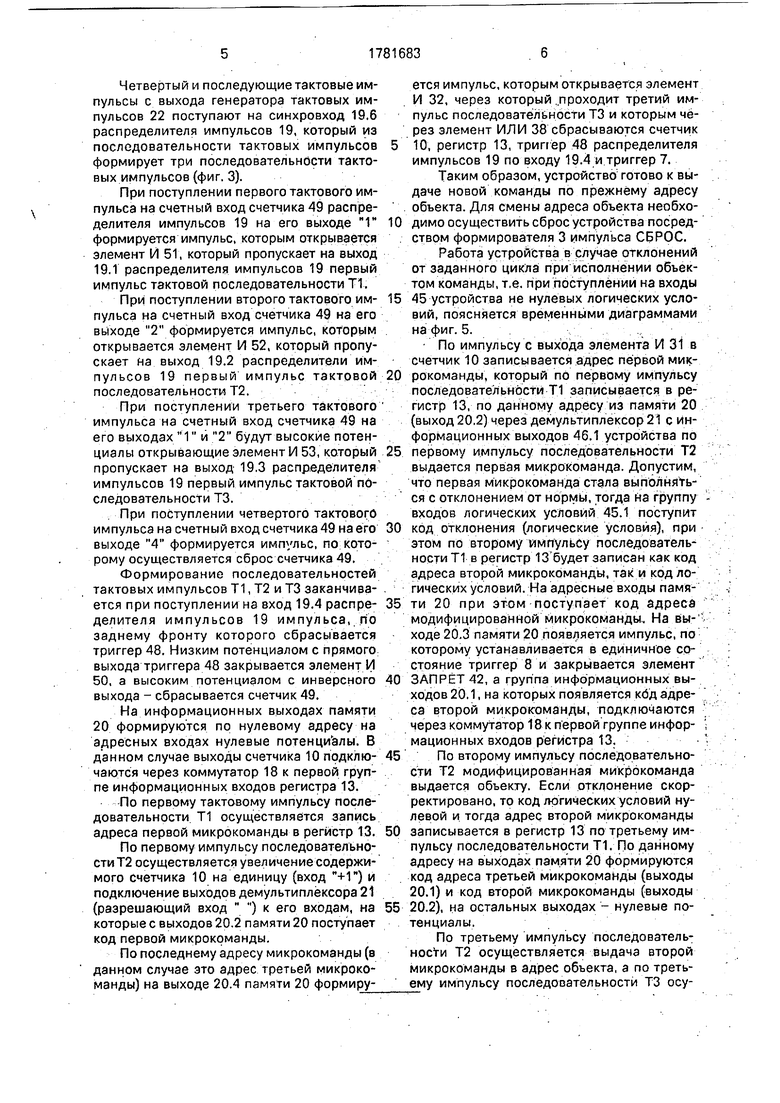

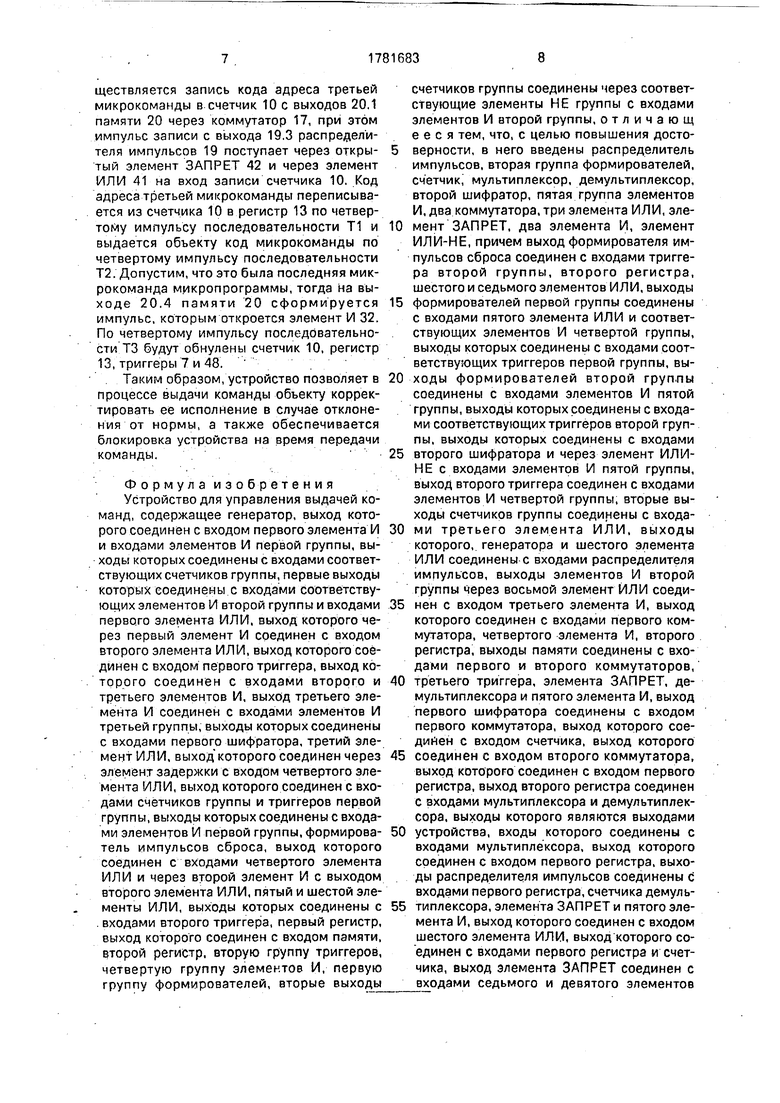

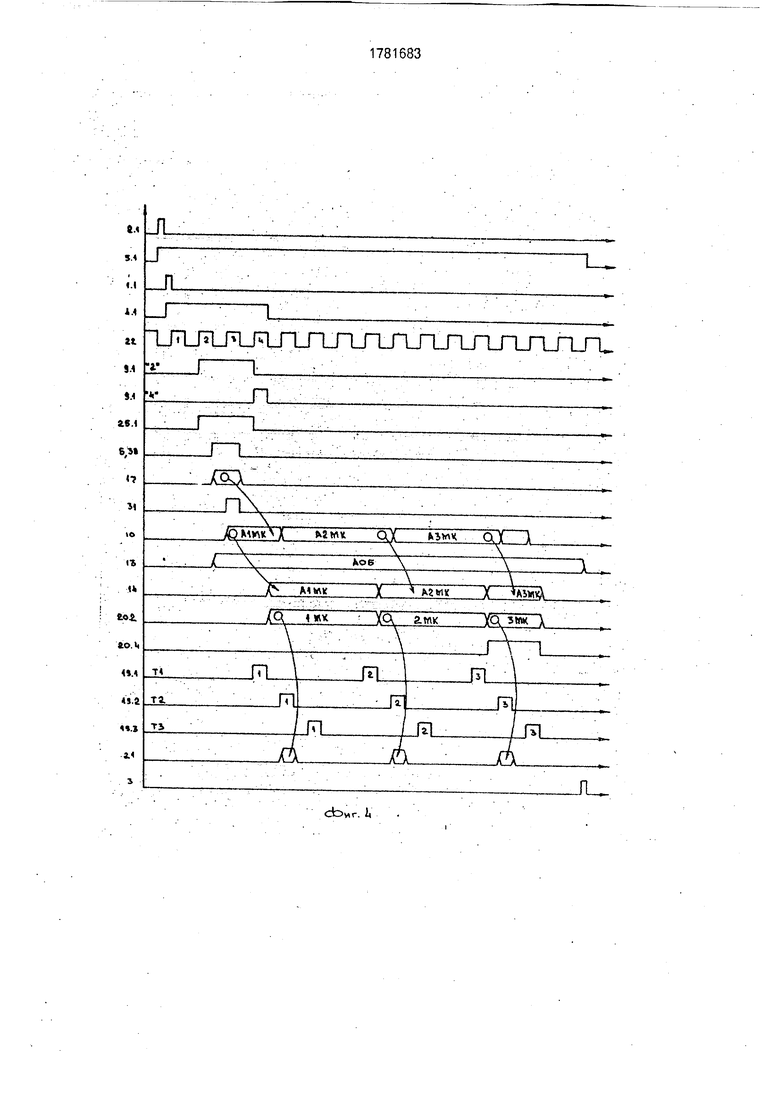

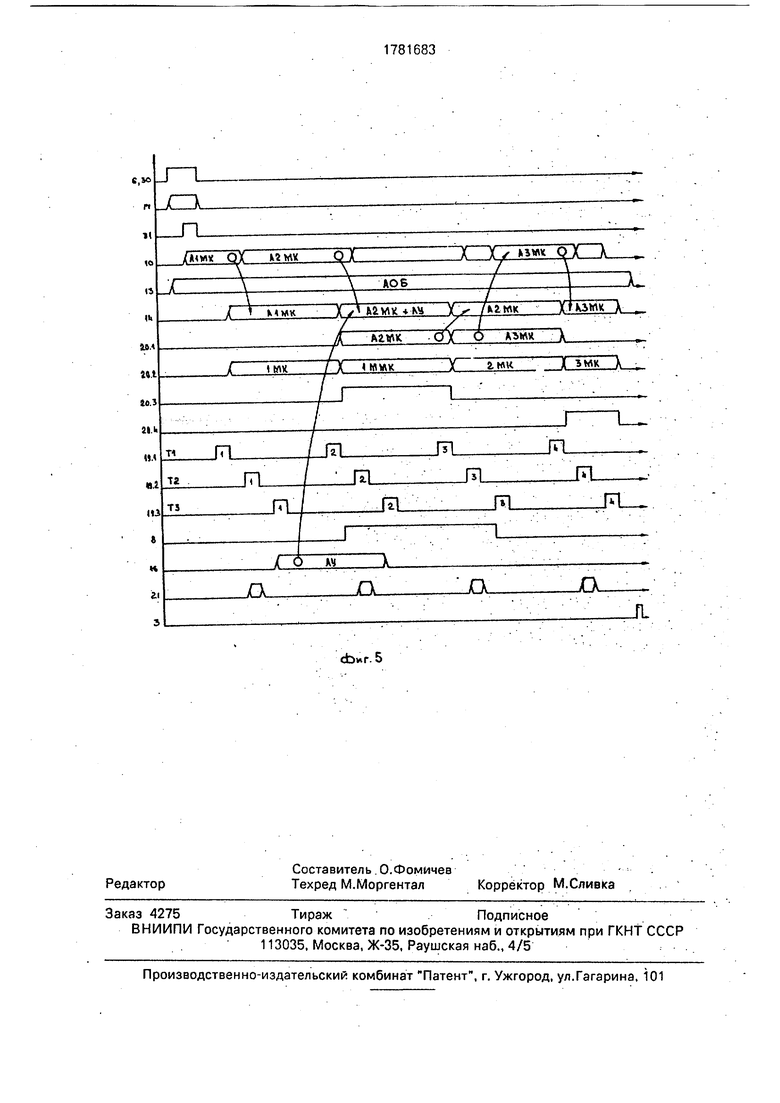

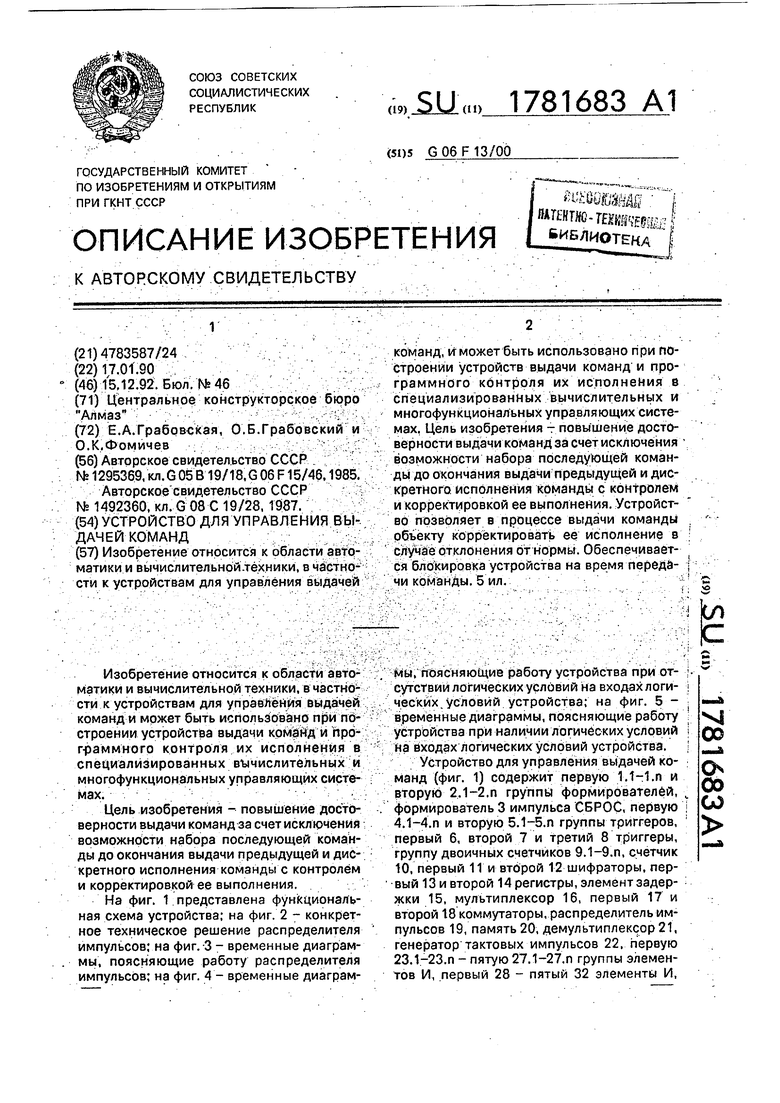

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - конкретное техническое решение распределителя импульсов: на фиг.-3 - временные диаграммы, поясняющие работу распределителя импульсов; на фиг. 4 - временные диаграммы, поясняющие работу устройства при от- сутствии логических условий на входах логи- i ческих.условий устройства; на фиг. 5 - временные диаграммы, поясняющие работу устройства при наличии логических условий на входах логических условий устройства.

Устройство для управления выдачей команд (фиг. 1) содержит первую 1.1-1.П и вторую 2.1-2.П группы формирователей, формирователь 3 импульса СБРОС, первую 4.1-4.п и вторую 5.1-5.П группы триггеров, первый 6, второй 7 и третий 8 триггеры, группу двоичных счетчиков 9.1-Э.п, счетчик 10, первый 11 и второй 12 шифраторы, первый 13 и второй 14 регистры, элемент задержки 15, мультиплексор 16, первый 17 и второй 18 коммутаторы, распределитель импульсов 19, память 20, демультиплексор 21, генератор тактовых импульсов 22, первую 23.1-23.п - пятую 27.1-27.П группы элементов И, первый 28 - пятый 32 элементы И,

V8 00

00 Ы

первый 33 -девятый 41 элементы ИЛИ, элемент ЗАПРЕТ 42, группу элементов НЕ 43, элемент ИЛИ-НЕ 44, группы входов 45 логических условий и группы информационных выходов 46.

Распределитель импульсов ,19 (фиг. 2) содержит элемент НЕ 47, триггер 48, счетчик 49, первый 50, второй 51, третий 52 и четвертый 53 элементы И, элемент ИЛИ 54, элемент ИЛИ-НЕ 55; первый 19.1, второй 19.2 и третий 19.3 синхровыходы, вход сброса 19.4, вход установки 19.5 и синхровход 19.6.

Устройство работает следующим образом.

В исходном-состоянии все элементы памяти (триггеры, счетчики и регистры) обнулены. Установка элементов устройства в исходное состояние осуществляется как автоматически, так и посредством формирователя 3 импульса СБРОС, которым сбрасываются триггеры 5.группы, регистр 14, через элемент ИЛИ 36 - триггеры 4 группы и двоичные счетчики 9 группы, через элемент ИЛИ 39, - триггер 8, через элемент ИЛИ 38 - распределитель импульсов 19, триггер 7, счетчик 10 и регистр 13.

В исходном состоянии на прямом выходе триггера 6 (Т-триггер) устанавливается низкий потенциал (логический О). Если по каким-либо причинам после включения устройства на выходе триггера 6 будет высокий потенциал (логическая 1), то импульс с выхода формирователя 3 импульса СБРОС через элементы И 29 и ИЛИ 34 установит триггер 6 в исходное состояние.

Для передачи команды определенному объекту оператор нажимает клавишу соответствующего формирователя, например, 2.1, импульс с выхода которого проходит через элемент И 27.1, открытый высоким потенциалом с выхода элемента ИЛИ-НЕ 44, устанавливая триггер 5.1 в единичное состояние, при этом код 10...О, с выходов триггеров 5 группы поступает на информационные входы шифратора 12, который формирует код адреса объекта, который с выходов шифратора 12 поступает на информационные входы регистра 14. Кроме того, высоким потенциалом с выхода триггера 5.1 через элемент ИЛИ-НЕ 44 блокируются элементы И 27 группы, с целью предотвращения случайной установки в единичное состояние других триггеров 5 группы.

Для выдачи выбранному объекту для исполнения определенной команды оператор нажимает клавишу соответствующе- го формирователя, например, 1.1, импульс с выхода которого через элемент И 26,1 устанавливает в единичное состояние триггер

4.1, который высоким потенциалом с прямого выхода открывает элемент И 23.1. Кроме того, импульс с выхода формирователя 1.1 через элемент ИЛИ 37 устанавливает (по

заднему фронту импульса) триггер 7 в единичное состояние, который низким потенциалом с инверсного выхода блокирует элементы И 26 группы, с целью предотвращения случайной установки в единичное состояние других триггеров 4 группы.

Работа устройства в случае правильного исполнения объектом команды, т.е. при поступлении на соответствующую группу входов 45 устройства нулевых логических

условий, поясняется временными диаграммами на фиг. 4.

Через элемент И 23.1 на счетный вход двоичного счетчика 9.1 поступают тактовые импульсы. В момент поступления второго

тактового импульса на выходе 2 двоичного счетчика 9.1 формируется импульс, которым открывается через элемент ИЛИ 33 элемент И 28, через открытый элемент И 24.1 - эле- мент.И 25.1, а чер&з элемент ИЛИ 40 - элемент И 30.

Импульс, сформированный триггером 6 из второго и третьего тактовых импульсов генератора тактовых импульсов 22, поступает через элемент И 30 на вход записи регистра 14, куда записывается код адреса объекта, открывает элемент И 31 и подключает информационные входы счетчика 10 через коммутатор 17 к выходам шифратора 11, на входы которого поступает код

10...О с выходов элементов И 25 группы, т.к. на соответствующий вход Открытого элемента И 25.1 поступает импульс с выхода элемента И 30.

Код адреса первой микрокоманды микропрограммы, поступающий на информационные входы счетчика 10,записывается в него по переднему фронту третьего тактового импульса, поступающего с выхода генератора тактовых импульсов 22 через

открытый элемент И 31 и элемент ИЛИ 41 на вход записи счетчика 10.

При поступлении четвертого тактового импульса на счетный вх од двоичного счетчика 9.1 на его выходе 4 формируется импульс, по которому закрывается через элемент НЕ 43.1 элемент И 24.1, запускается элемент задержки 15 через элемент ИЛИ 35 и устанавливается в единичное состояние триггер 48 распределителя импульсов 19 по входу 19 5.

Импульсом с выхода элемента задержки 15 через элемент ИЛИ 36 сбрасываются триггеры 4 группы и двоичные счетчики 9 группы.

Четвертый и последующие тактовые импульсы с выхода генератора тактовых импульсов 22 поступают на синхровход 19.6 распределителя импульсов 19, который из последовательности тактовых импульсов формирует три последовательности тактовых импульсов (фиг. 3).

При поступлении первого тактового импульса на счетный вход счетчика 49 распределителя импульсов 19 на его выходе 1 формируется импульс, которым открывается элемент И 51, который пропускает на выход 19.1 распределителя импульсов 19 первый импульс тактовой последовательности Т1.

При поступлении второго тактового импульса на счетный вход счетчика 49 на его выходе 2 формируется импульс, которым открывается элемент И 52, который пропускает на выход 19.2 распределители импульсов 19 первый импульс тактовой последовательности Т2.

При поступлении третьего тактового импульса на счетный вход счетчика 49 на его выходах 1 и 2 будут высокие потенциалы открывающие элемент И 53, который пропускает на выход 19,3 распределителя импульсов 19 первый импульс тактовой последовательности ТЗ.

При поступлении четвертого тактового импульса на счетный вход счетчика 49 на его выходе 4 формируется импульс, по которому осуществляется сброс счетчика 49,

Формирование последовательностей тактовых импульсов Т1, Т2 и ТЗ заканчивается при поступлении на вход 19.4 распределителя импульсов 19 импульса, по заднему фронту которого сбрасывается триггер 48. Низким потенциалом с прямого выхода триггера 48 закрывается элемент И 50, а высоким потенциалом с инверсного выхода - сбрасывается счетчик 49.

На информационных выходах памяти 20 формируются по нулевому адресу на адресных входах нулевые потенциалы. В данном случае выходы счетчика 10 подключаются через коммутатор 18 к первой группе информационных входов регистра 13.

По первому тактовому импульсу последовательности Т1 осуществляется запись адреса первой микрокоманды в регистр 13.

По первому импульсу последовательности Т2 осуществляется увеличение содержимого счетчика 10 на единицу (вход +1) и подключение выходов демультиплексора 21 (разрешающий вход ) к его входам, на которые с выходов 20.2 памяти 20 поступает код первой микрокоманды.

По последнему адресу микрокоманды (в данном случае это адрес третьей микрокоманды) на выходе 20.4 памяти 20 формируется импульс, которым открывается элемент И 32, через который проходит третий импульс последовательности ТЗ и которым через элемент ИЛИ 38 сбрасываются счетчик 5 10, регистр 13, трип ер 48 распределителя импульсов 19 по входу 19.4 и триггер 7.

Таким образом, устройство готово к выдаче новой команды по прежнему адресу объекта. Для смены адреса объекта необхо- 0 димо осуществить сброс устройства посредством формирователя 3 импульса СБРОС.

Работа устройства в случае отклонений от заданного цикла при исполнении объектом команды, т.е. при поступлении на входы

5 45 устройства не нулевых логических условий, поясняется временными диаграммами на фиг. 5.

По импульсу с выхода элемента И 31 в счетчик 10 записывается адрес первой мик0 рокоманды, который по первому импульсу последовательности Т1 записывается в регистр 13, по данному адресу из памяти 20 (выход 20.2) через демультиплексор 21 с информационных выходов 46.1 устройства по

5 первому импульсу последовательности Т2 выдается первая микрокоманда. Допустим, что первая микрокоманда стала выполняться с отклонением от нормы, тогда на группу - входов логических условий 45.1 поступит

0 код отклонения (логические условия), при этом по второму импульсу последовательности Т1 в регистр 13 будет записан как код адреса второй микрокоманды, так и код логических условий. На адресные входы памя5 ти 20 при этом поступает код адреса модифицированной микрокоманды. На выходе 20.3 памяти 20 появляется импульс, по которому устанавливается в единичное состояние триггер 8 и закрывается элемент

0 ЗАПРЕТ 42, а группа информационных выходов 20.1, на которых появляется код адреса второй микрокоманды, подключаются через коммутатор 18 к первой группе инфор- , мационных входов регистра 13.

5 По второму импульсу последовательности Т2 модифицированная микрокоманда выдается объекту. Если отклонение скорректировано, то код логических условий нулевой и тогда адрес второй микрокоманды

0 записывается в регистр 13 по третьему импульсу последовательности Т1, По данному адресу на выходах памяти 20 формируются код адреса третьей микрокоманды (выходы 20.1) и код второй микрокоманды (выходы

5 20.2), на остальных выходах - нулевые потенциалы.

По третьему импульсу последовательности Т2 осуществляется выдача второй микрокоманды в адрес объекта, а по третьему импульсу последовательности ТЗ осуществляется запись кода адреса третьей микрокоманды в счетчик 10 с выходов 20.1 памяти 20 через коммутатор 17, при этом импульс записи с выхода 19.3 распределителя импульсов 19 поступает через открытый элемент ЗАПРЕТ 42 и через элемент ИЛИ 41 на вход записи счетчика 10. Код адреса третьей микрокоманды переписывается из счетчика 10 в регистр 13 по четвертому импульсу последовательности Т1 и выдается объекту код микрокоманды по четвертому импульсу последовательности Т2. Допустим, что это была последняя микрокоманда микропрограммы, тогда на выходе 20.4 памяти 20 сформируется импульс, которым откроется элемент И 32. По четвертому импульсу последовательности ТЗ будут обнулены счетчик 10, регистр 13, триггеры 7 и 48.

Таким образом, устройство позволяет в процессе выдачи команды объекту корректировать ее исполнение в случае отклонения от нормы, а также обеспечивается блокировка устройства на время передачи команды.

Формула изобретения Устройство для управления выдачей команд, содержащее генератор, выход которого соединен с входом первого элемента И и входами элементов И первой группы, выходы которых соединены с входами соответствующих счетчиков группы, первые выходы которых соединены с входами соответствующих элементов И второй группы и входами первого элемента ИЛИ, выход которого через первый элемент И соединен с входом второго элемента ИЛИ, выход которого соединен с входом первого триггера, выход которого соединен с входами второго и третьего элементов И, выход третьего элемента И соединен с входами элементов И третьей группы, выходы которых соединены с входами первого шифратора, третий элемент ИЛИ, выход которого соединен через элемент задержки с входом четвертого элемента ИЛИ, выход которого соединен с входами счетчиков группы и триггеров первой группы, выходы которых соединены с входами элементов И первой группы, формирователь импульсов сброса, выход которого соединен с входами четвертого элемента ИЛИ и через второй элемент И с выходом второго элемента ИЛИ, пятый и шестой элементы ИЛИ, выходы которых соединены с входами второго триггера, первый регистр, выход которого соединен с входом памяти, второй регистр, вторую группу триггеров, четвертую группу элементов И, первую группу формирователей, вторые выходы

счетчиков группы соединены через соответствующие элементы НЕ группы с входами элементов И второй группы, отличают, е е с я тем, что, с целью повышения достоверности, в него введены распределитель импульсов, вторая группа формирователей, счетчик, мультиплексор, демультиплексор, второй шифратор, пятая группа элементов И, два коммутатора, три элемента ИЛИ, эле0 мент ЗАПРЕТ, два элемента И, элемент ИЛИ-НЕ, причем выход формирователя импульсов сброса соединен с входами триггера второй группы, второго регистра, шестого и седьмого элементов ИЛИ, выходы

5 формирователей первой группы соединены с входами пятого элемента ИЛИ и соответствующих элементов И четвертой группы, выходы которых соединены с входами соответствующих триггеров первой группы, вы0 ходы формирователей второй груп-пы соединены с входами элементов И пятой группы, выходы которых соединены с входами соответствующих триггере в второй группы, выходы которых соединены с входами

5 второго шифратора и через элемент ИЛИ- НЕ с входами элементов И пятой группы, выход второго триггера соединен с входами элементов И четвертой группы, вторые выходы счетчиков группы соединены с входа0 ми третьего элемента ИЛИ, выходы которого, генератора и шестого элемента ИЛИ соединены с входами распределителя импульсов, выходы элементов И второй группы через восьмой элемент ИЛИ соеди5 нен с входом третьего элемента И, выход которого соединен с входами первого коммутатора, четвертого элемента И, второго регистра, выходы памяти соединены с входами первого и второго коммутаторов,

0 третьего триггера, элемента ЗАПРЕТ, де- мультиплексора и пятого элемента И, выход первого шифратора соединены с входом первого коммутатора, выход которого соединен с входом счетчика, выход которого

5 соединен с входом второго коммутатора, выход которого соединен с входом первого регистра, выход второго регистра соединен с входами мультиплексора и демультиплек- сора, выходы которого являются выходами

0 устройства, входы которого соединены с входами мультиплексора, выход которого соединен с входом первого регистра, выходы распределителя импульсов соединены с входами первого регистра, счетчика демуль5 типлексора, элемента ЗАПРЕТ и пятого элемента И, выход которого соединен с входом шестого элемента ИЛИ, выход которого соединен с входами первого регистра и счетчика, выход элемента ЗАПРЕТ соединен с входами седьмого и девятого элементов

ИЛИ. выход седьмого элемента ИЛИ - с ход генератора соединен с входом четверто- входом третьего триггера, выход которого го элемента И, выход которого соединен с соединен с входом элемента ЗАПРЕТ, вы- входом девятого элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Устройство для программного управления | 1982 |

|

SU1057925A1 |

| Устройство для контроля и восстановления вычислительного процесса | 1988 |

|

SU1605233A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для обучения операторов | 1986 |

|

SU1411801A1 |

| Устройство для программного управления | 1982 |

|

SU1067470A1 |

| Устройство для программного управления | 1991 |

|

SU1800445A1 |

| Двухканальное устройство для контроля и восстановления процессорных систем | 1986 |

|

SU1397917A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

Изобретение относится к области автоматики и вычислительной.техники, в частности к устройствам для управления выдачей команд, и может быть использовано при построении устройств выдачи команд и программного контроля их исполнения в специализированных вычислительных и многофункциональных управляющих системах. Цель изобретения т повышение достоверности выдачи команд за счет исключения возможности набора последующей команды до окончания выдачи предыдущей и дискретного исполнения команды с контролем и корректировкой ее выполнения. Устройство позволяет в процессе выдачи команды объекту корректировать ее исполнение в случае отклонения от нормы. Обеспечивается блокировка устройства на время передачи команды. 5 ил.

т гщ

«(О

л О«ACV

li «& «l.t ч tl lit «л l.t « «л

JЛJПJЯЛJlJПJlJTГLЛJlJTJaЛJ IЛ

Фиг./

О ч

О(

t.

54

(.1

Л.4

It

.4

$,«

)1

to

il

Ik

to

го t

4M

a.

з

, JL

f

П

TJnj J4J LnJTJnJTJ4J l

п

л

„ :ц

) мми CXX fcwx 0.1 A

Л

V

Л

fcos

/ .MwT

У MMK

/Q

КО, &ткfa stftK X

T4

тг

Ti

A.

m

ja

m

.R

JU

сЬиг 1

X fcwx 0.1

V

Л

fcos

У MMK

КО, &ткfa stftK X

A.

m

.R

JU

| Устройство для управления процессом передачи сигналов управления в иерархической автоматизированной системе управления | 1985 |

|

SU1295369A1 |

| Устройство для передачи информации | 1987 |

|

SU1492360A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1992-12-15—Публикация

1990-01-17—Подача