Изобретение относится к вычислительной технике, в частности к технологии изготовления полупроводниковых интегральных микросхем. Оно может быть использовано для изготовления матричного накопителя электрически программируемого постоянного запоминающего устройства (СППЗУ) на лавинно-инжекционньгх транзисторах с плавающими и управляющими затворами, нашедшими применение в блоках вычислительных машин, в устройствах автоматики.

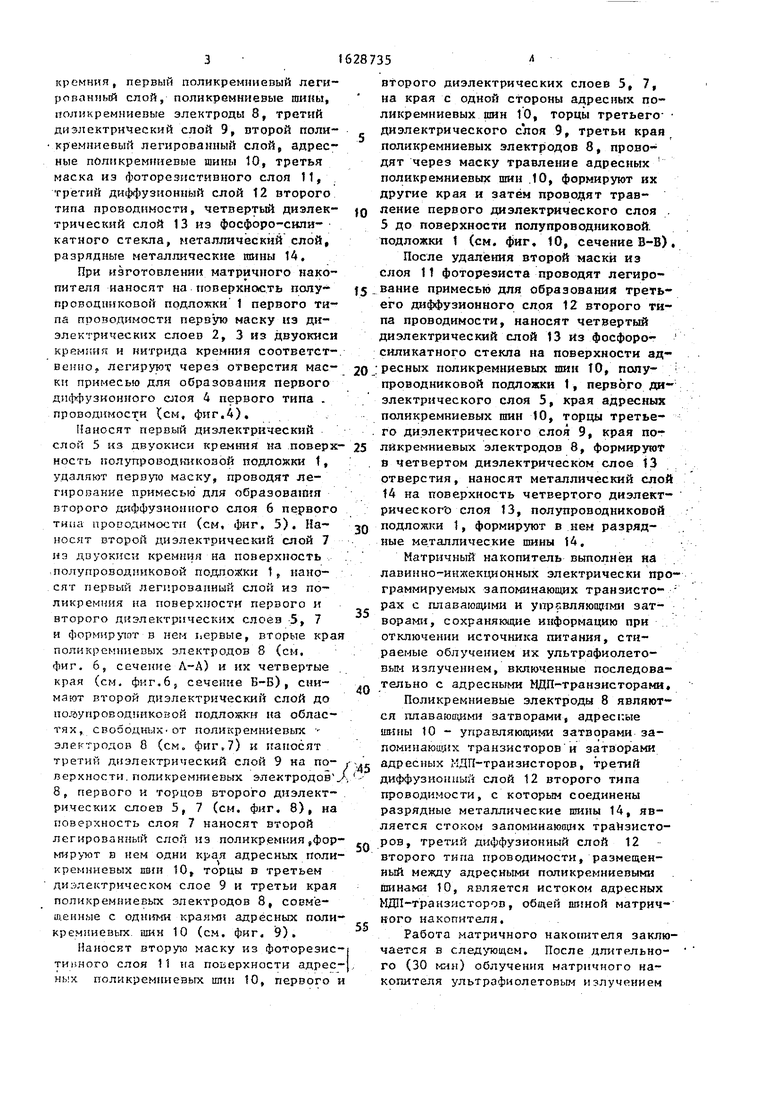

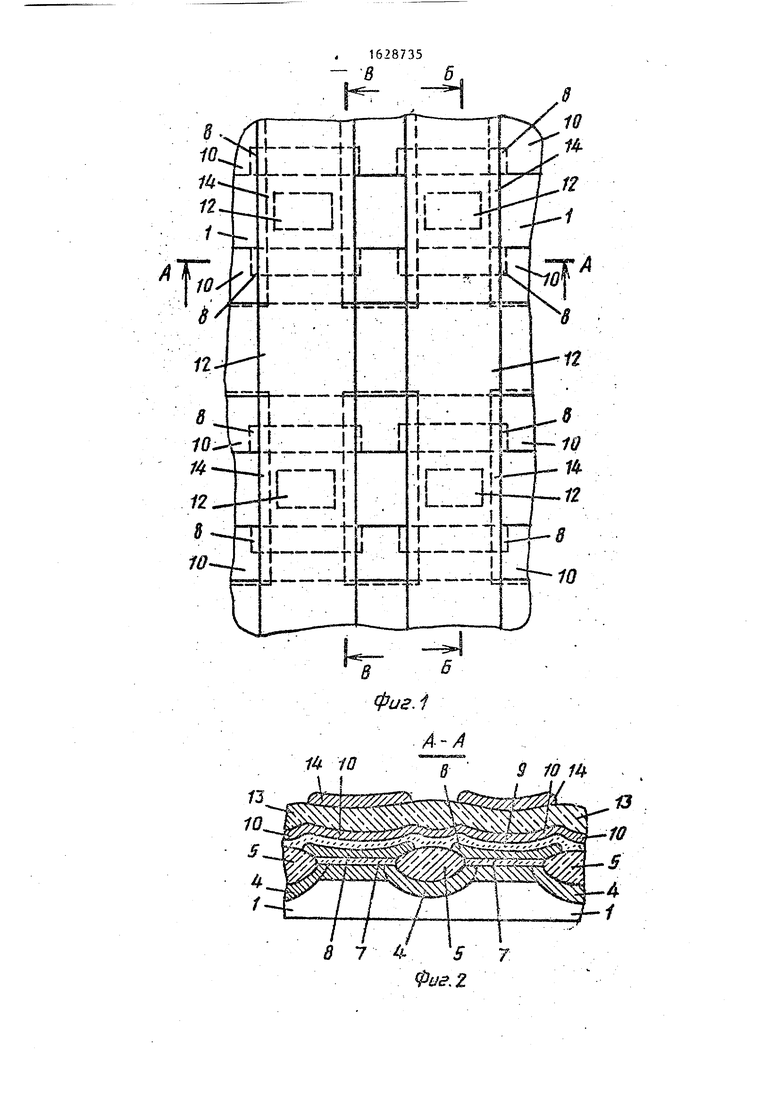

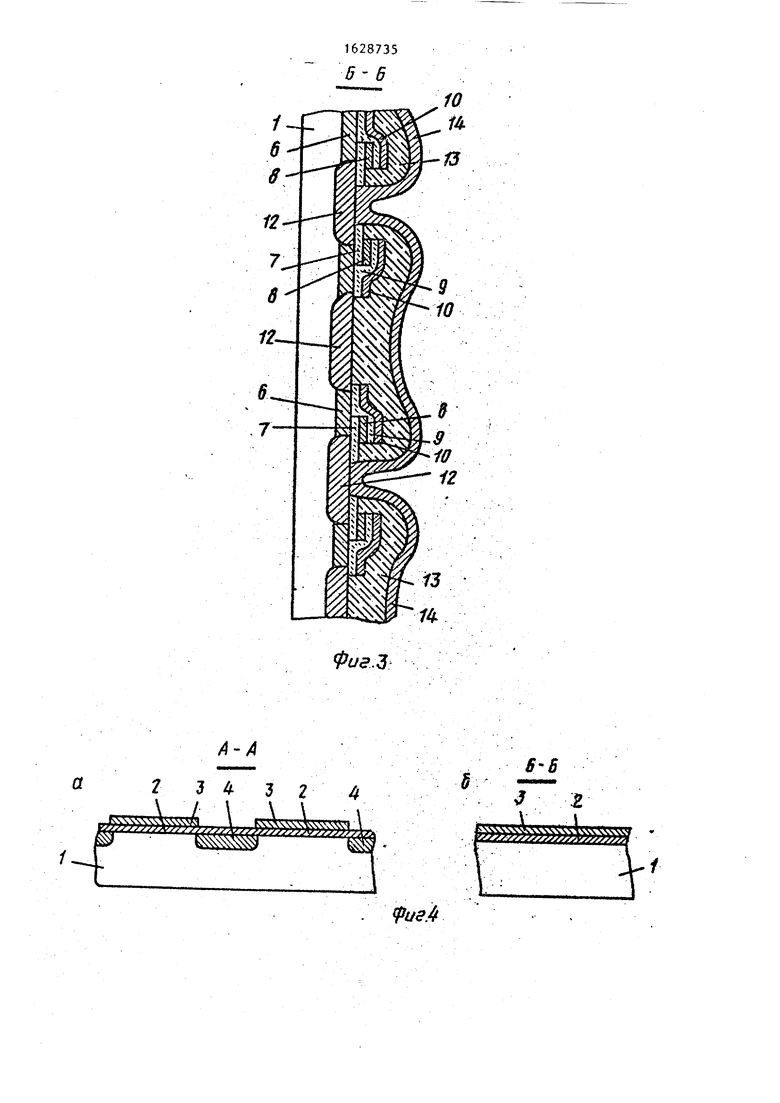

Целью изобретения является повышение выхода годных за счет уменьшения подтравливзния второго и третьего диэлектрических слоев под и над краями поликремниевых электродов. На фнг.t схематически изображен матричный накопитель на восьми запоминающих элементах; па фиг.2 - сечение А-А на фиг.1, на фнг.З - сечение Б--Б на фнг.; на фиг.4-Ю - различные стадия изготовления этого матричного накопителя.

На чертежах использованы следующие условные обозначения: полупроводниковая подложка 1 первого типа проводимости, диэлектрический слон 2 из двуокиси кремния первом маски,диэлектрический слой 3 из нитрида кремния первой маски, первый диффузионный слой 4 первого типа проводимости,первый диэлектрический слой 5 из двуокиси кремния, второй диффузионный слой 6 первого типа проводимости, второй диэлектрический слой 7 из двуокиси

кремния, первый поликремнневый легированный слой, поликремниевые шины, поликремниевые электроды 8, третий диэлектрический слой 9, второй поли- кремниевый легированный слой, адресные поликремниевые шины 10, третья маска из фоторезистивного слоя 11, третий диффузионный слой 12 второго типа проводимости, четвертый диэлектрический слой 13 из фосфоро-сили- катного стекла, металлический слой, разрядные металлические шины 14.

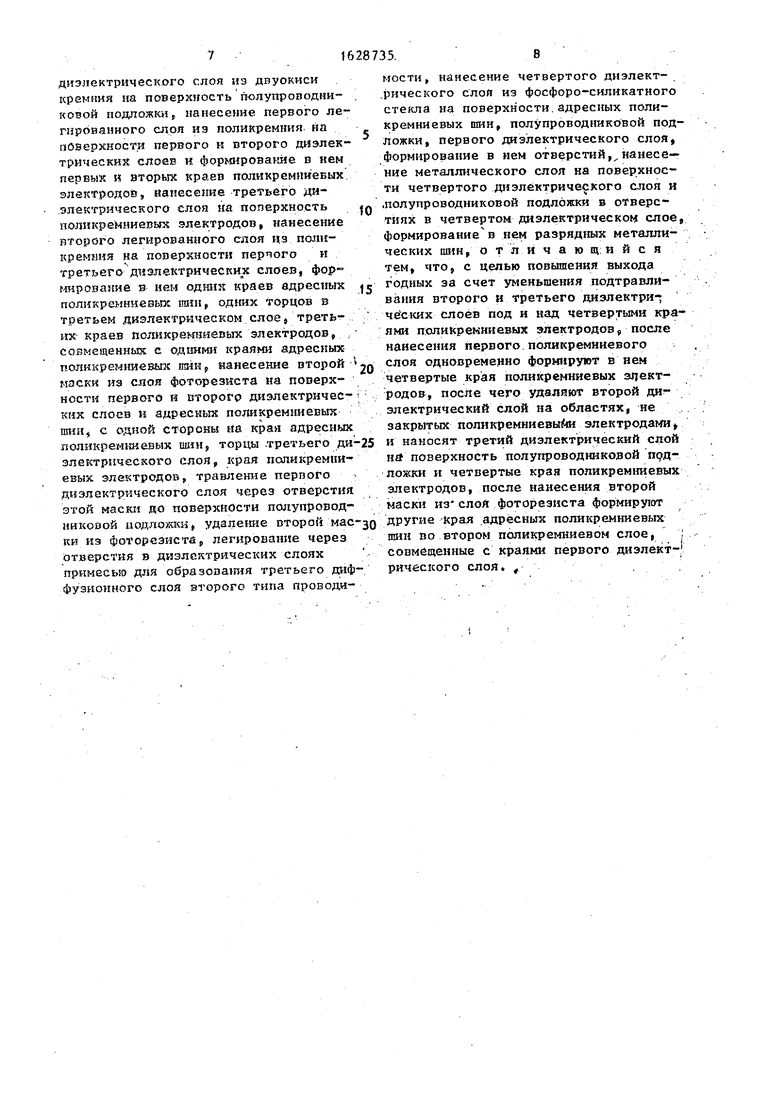

При изготовлении матричного накопителя наносят на поверхность полупроводниковой подложки 1 первого типа ПРОВОДИМОСТИ первую маску из диэлектрических слоев 2, 3 из двуокиси кргмиия и нитрида кремния соответственно, легируют через отверстия маски примесью для образования первого диффузионного слоя 4 первого типа . проводимости . фиг.4).

Наносят первый диэлектрический слой 5 из двуокиси кремния на поверхность полупроводниковой подложки 1, удаляют первую маску, проводят легирование примесью для образования второго диффузионного слоя 6 первого типа проводимости (см, фиг, 5). Наносят второй диэлектрический слой 7 ит двуокиси кремния на поверхность полупроводниковой подложки 1, нанося г первый легированный слой из по- ликремния на поверхности первого и второго диэлектрических слоев 5, 7 и формирупт в нем первые, вторые кра поликремниевых эпектродов 8 (см, фиг. 6, сечение А-А) и их четвертые края (см. фиг.б., сечение Б-Б), снимают второй диэлектрический слой до полупроводниковой подложки на областях, свободных-от поликремниевьгх электродов 8 (см. ) и наносят третий диэлектрический слой 9 на по- верхности полнкремниевых электродов 8, первого и торцов второго диэлектрических слоев 5, 7 (сн, фиг, 8), на поверхность слоя 7 наносят второй легированный слон из полнкремния,формируют в нем одни края адресных поликремниевых шин 10, торцы в третьем диэлектрическом слое 9 и третьи края поликремниевых электродов 8, совмещенные с одними краями адресных поли кречниевнх шин 10 (см. фиг. 9).

Наносят вторую маску из фоторезис тииного слоя 11 на поверхности адрес нь х поликремниевых шли 10, первого

5

0

5

0

5

0

5

0

S

второго диэлектрических слоев 5, 7, на края с одной стороны адресных поликремниевых шин 10, торцы третьего- диэлектрического слоя 9, третьи края поликремниевых электродов 8, проводят через маску травление адресных поликремниевых шин 10, формируют их другие края и затем проводят травление первого диэлектрического слоя 5 до поверхности полупроводниковой подложки 1 (см. фиг. 10, сечение В-В).

После удаления второй маски из слоя 11 фоторезиста проводят легирование примесью для образования третьего диффузионного слоя 12 второго типа проводимости, наносят четвертый диэлектрический слой 13 Из фосфоро- силикатного стекла на поверхности ад- ресных поликремниевых шин ТО, полупроводниковой подложки 1, первого диэлектрического слоя 5, края адресных поликремниевых шин 10, торцы третьего диэлектрического слоя 9, края поликремниевых электродов 8, формируют в четвертом диэлектрическом слое 13 отверстия, наносят металлический слой 14 на поверхность четвертого диэлектрического слоя 13, полупроводниковой подложки 1, формируют в нем разрядные металлические шины 14.

Матричный накопитель выполнен на лавинно-инжекционных электрически программируемых запоминающих транзисто- pax с плавающими и управляющими затворами, сохраняющие информацию при отключении источника питания, стираемые облучением их ультрафиолетовым излучением, включенные последовательно с адресными ЭДЩ-транзисторами.

Поликремниевые электроды 8 являются плавающими затворами, адресные mum 10 - управляющими затворами запоминающих транзисторов и затворами адресных МДП-тракзисторов, третий диффузионный слой 12 второго типа проводимости, с которым соединены разрядные металлические шины 14, является стоком запоминающих транзисторов, третий диффузионный слой 12 второго типа проводимости, размещенный между адресными поликремниевыми тинами 10, является истоком адресных МДП-транзнсторов, общей шиной матричного накопителя.

Работа матричного накопителя заключается в следующем. После длительного (30 мин) облучения матричного накопителя ультрафиолетовым излучением

пороговые напряжения всех запоминаю- щих транзисторов низкие (1-2 В),так как с поликремниевых электродов удален заряд электронов.

Дпя программирования выбранных запоминающих транзисторов на выбранную адресную поликремниевую шину 10 подают высокое положительное импульсное напряжение (12 В, 10 мс), на остальные адресные поликремниевые шины 10 - нулевое напряжение.

На выбранные разрядные металлические шины 14 подают через нагрузки i аналогичные положительные высокие импульсные напряжения, на невыбранные разрядные металлические шины 14 - нулевое напряжение.

На общую диффузионную шину (12) второго типа проводимости подают нулевое или низкое положительное напряжение (1-2 В) относительно полупроводниковой подложки 1.

За счет подачи высоких положительных напряжений на управляющие затворы и стоки выбранных запоминающих транзисторов (низкое - на истоки адресных МДП-транзисторов) через них протекают токи, инжектируя горячие электроны в запоминающих транзисторах, которые захватываются поликрем- ииевыми электродами, увеличивая величину порогового напряжения запоминающих транзисторов до величины 6 - 9 В и более.

Состояния остальных запоминающих транзисторов сохраняются неизменными из-за нулевого напряжения или на адресных поликремниевых шинах 10 или разрядных металлических шинах 14.

В режиме считывания информации на выбранные и невыбранные запоминающие транзисторы подается положительное импульсное напряжение аналогично, как при программировании, но малой величины и длительности (+5 В, 300 не).

Если напряжение на управляющем затворе выбранного запоминающего транзистора не превышает (превышает) величины порогового напряжения, то через них и выбранные разрядные шины 14 ток не протекает (протекает), что эквивалентно нулевому (единичному)

5

годных за счет исключения иодтравлн- вания второго н третьего диэлектрических слоев под и над четвертыми краями поликремнневых электродов, так как четвертые края поликремниевых электродов сформированы до формирования адресных поликремнневых шпп и удалены от их краев, и кроме того, повышение быстродействия при считывании информации за счет включения адресного МДП-транзнстора последовательно с запоминающим транзистором. В результате этого обеспечивается повышение т.ока ячейки памяти в 2-3 раза в режиме считывания информации, увеличение напряжения отпирания по стоку при более высокой передаче напряжения со стока на поликремниевый электрод 0 для запоминающего транзистора, что позволяет улучшить программирующие и маскирующие свойства запоминающего транзистора, также приводящие к увеличению выхода годных.

В настоящее время отрабатывается схемотехника н технология изготовления по предлагаемому способу СППЗУ с информационной емкостью 65 кбит с площадью ячейки памяти 36 мкм при 2 мкм норме проектирования, разрабатываются дополнительные фотошаблоны вместо имеющихся для экспериментального подтверждения улучшения технических характеристик, в том числе- быстродействия при считыяанин информации, -улучшения программирующих и маскирующих свойств, обеспечивающих повышение выхода годных и надежности работы.

5

0

5

40

Формула изобретения

Способ изготовления матричного накопителя для постоянного запоминающего устройства, включаю1ций нанесение первой маски из диэлектрических слоев из двуокиси кремния н нитрида кремния на поверхность полупроводниковой подложки первого типа прово- димоети, легирование через отверстия маски примесью для образования первого диффузионного слоя первого типа проводимости, нанесение первого диэлектрического слоя из двуокиси крем

Изобретение относится к вычислительной технике, в частности к технологии изготовления полупроводниковых интегральных микросхем. Целью изобретения является повышение выхода годных за счет уменьшения подтрзп- ливакия второго и третьего диэлектрических слоев и над краями поликремниевых электродов. За счет подачи высоких положительных напряжений на управляющие затворы и стоки выбранных запоминающих транзисторов (низкое - на истоки адресных ЩЦ1- транзисторов) через них протекают токи, инжектируя горячие электроны в запоминающих транзисторах, которые захватываются поликремниевыми электродами, увеличивал величину порогового напряжения запоминающих транзисторов до величины 6-9 В ч более. 10 ил. Ш

состоянию выбранных запоминающих тран- ее ния на поверхность полупроводниковой зисторов.подложкл, удаление первой маски, леОсновным преимуществом предложен-гированке примесью для образования

ного способа изготовления матричноговторого диффузионного слоя первого

накопителя является повышение выходатипа проводимости, нанесение второго

диэлектрического слоя нз двуокиси кремния па поверхность полупроводниковой подложки, нанесение первого легированного слоя из поликремния на поверхности первого и второго диэлектрических слоев и формирование в нем первых и вторых краев поликремниевых электродов, нанесение третьего диэлектрического слоя на поверхность поликремниепых электродов, нанесение второго легированного сдоя из поли- кремиия на поверхности первого и третьего диэлектрических слоев, фор- мнрование в нем одних краев адресных поликрешшеэых тин, одних торцов в тоетьем диэлектрическом слое третьих краев поликремниевых электродов, совмещенных с одними краями адресных роликремниевых шин ианесение второй мэски из спая фоторезиста на поверхности первого и второго диэлектрических слоев и адресных поликремниевых шин, с оцяой стороны на края адресных полшфешЕиевых шин, торцы третьего ди электрического слоя, края поликремниевых электродов, травление первого диэлектрического слоя через отверстия згой маски до поверхности полупроводниковой подложки I удаление второй мас ки из фоторезиста,, легирование через отверстия в диэлектрических слоях примесью для образования третьего диффузионного слоя второго типа проводимости, нанесение четвертого диэлектрического слоя из фосфоро-силикатного стекла на поверхности адресных поликремниевых шин, полупроводниковой подложки, первого диэлектрического слоя, формирование в нем отверстий нанесение металлического слоя на поверхности четвертого диэлектрического слоя и полупроводниковой подложки в отверстиях в четвертом диэлектрическом слое формирование нем разрядных металлических шин, отличающийся тем, что, с целью повышения выхода годных за счет уменьшения подтравли- вания второго и третьего диэлектрических слоев под и над четвертыми краями поликреыниевых электродов, после нанесения первого поликремниевого слоя одновременно формируют в нем четвертые края поликремниевых электродов, после чего удаляют второй диэлектрический слой на областях, не закрытых поликремниевыми электродамиt и наносят третий диэлектрический слой на поверхность полупроводниковой прД- ложки и четвертые края попикремииевых электродов, после нанесения второй маски из слой фоторезиста формируют другие края адресных поликремниевых шин во втором поликремниевом слое, совмещенные с краями первого диэлектрического слоя. ,

074

Фиг. 2

ш&ттщшщ С

ДД&Л.УЧУЧгазгеЧ

г

9-9

I ИО У У УЧ-У

г Ј ъ Ј

V-V

Г)

ргпф

Г- о

Ч&

i

«

СО Cvl ЧС

«о

I

«JCS

I Vd

ч «

| Технический отиет предприятия п.я | |||

| Система глазных линз | 1926 |

|

SU5936A1 |

Авторы

Даты

1992-09-23—Публикация

1989-06-19—Подача