И;обретение относится к автомати- зиро анным системам контроля и может быть применено при контроле больших интегральных схем (БИС) и сверхбольших Iнтегральных схем (СБИС) на МОП- CTpyi Typax..

изобретения - расширение функциональных возможностей путем

контроля.объектов с про- временем выполнения опера-.

Ц€ЛЬ

:к1 И01: обесг ечения

изводьным .ции.

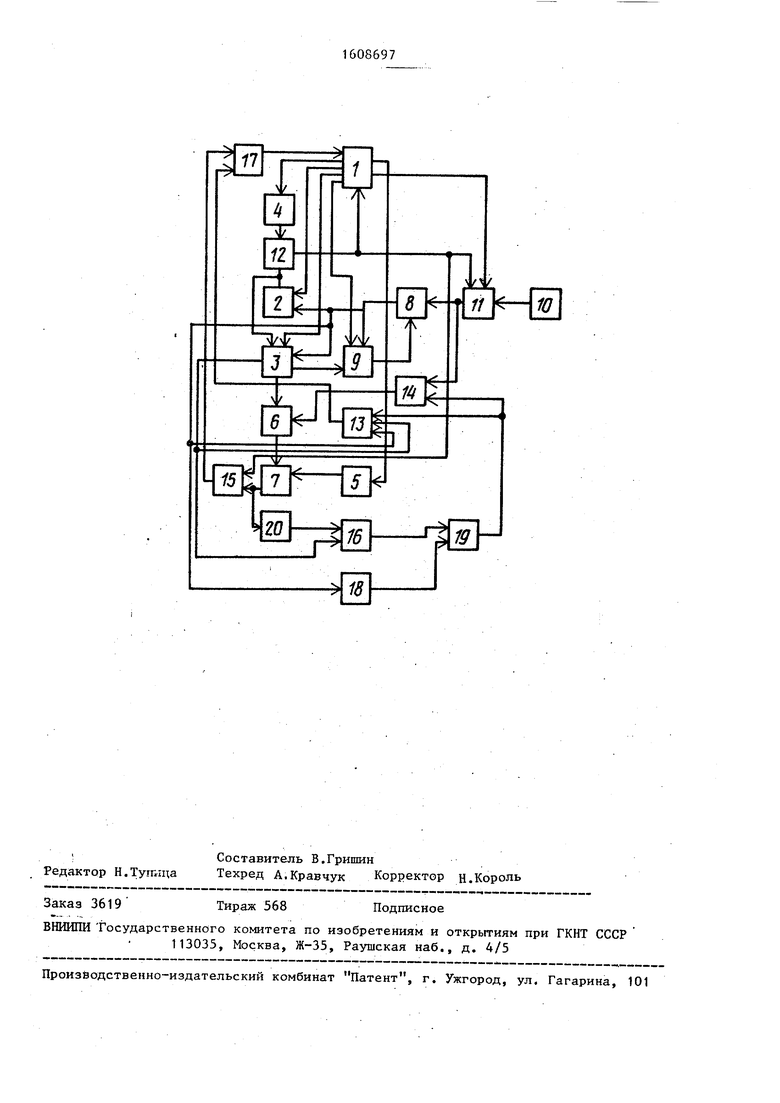

На чертеже приведена функциональ- ная схема устройства.

Устройство содержит управляюпщй . вычислительный блок 1, счетчик 2 адреса памяти, блок 3 памяти тестов, регистр 4 адреса тестовой комбинации, регистр 5 выходной тестовой комбинации, контролируемый объект 6, многоканальный амплитудный дискриминатор 7, счетчик 8 числа повторения тестовых комбинаций, группу 9 элементов ЗИ, генератор 10 тактовой частоты, первый элемент ЗИ 11, схему 12 сравнения, : второй элемент ЗИ 13, три элемента И 14-16,, элемент ИЛИ 17, формирователь

о:

О 00

о: со

импульса, триггер 19 и элемент ; НЕ 20.

Устройство работает следующим образом.I 5

В исходное состояние устройство устанавливается сигналом Сброс (не показан), при этом в исходное состояние устанавливаются счетчики 2 и 8, триггер 19 и управляю1ций вычислитель- ю ный блок 1..

Управляющий вычислительный блок 1 по команде Пуск передает в счетчик 2 адреса памяти начальный адрес ячейки блока 3, в которой хранится первая 15 тестовая комбинация для контролируе- мого типа объекта 6.-В регистр 4 адреса тестовой комбинации записьшает- ся адрес тестовой комбинации,.на которой требуется зафиксировать выходные 20 сигналы контролируемого объекта 6. В регистр 5 выходной тестовой комбинации из запоминающего устройства выходных тестовых комбинаций, входящего в состав управляющего вычисли- 25 тельного блока 1, поступает выходная тестовая комбинация, соответствующая выходным сигналам контролируемого объекта 6 на указанном в регистре

мент ЗИ 11. При заполнении счетчика 8 наращивается на 1 счетчик 2 и через формирователь 18 импульса по заднему фронту импульса устанавливается в исходное состояние триггер 19.

При этом запрашивается блок 3 по еледующему адресу и открывается элемент И для записи в счетчик 8 следующей тестовой комбинации. На требуемом номере цикла (при равенстве адресов в счетчике 2 и регистре 4) схема 12 сравнения запрещаё т прохождение тактовых импульсов на счетчик 8, закрывая элемент ЗИ 11, и подает стробирую щий импульс на элемент И 15, разрешая поступление сигнала неисправности контролируемого объекта б на управляющий вычислительный блок 1 с выхода многоканального амплитудного дискриминатора 7.

При необходимости исследований выходных сигналов следующей тестовой комбинации указанный цикл повторяется. Если контролируемый объект 6 является объектом с произвольным временем выполнения операции, то в дополнительный разряд необходимой ячейки блока 3 записывается сигнал разреше

| название | год | авторы | номер документа |

|---|---|---|---|

| Система для автоматического контроля больших интегральных схем | 1976 |

|

SU664178A1 |

| Система для автоматического контроля больших интегральных схем | 1983 |

|

SU1124331A2 |

| ОПИСАНИЕ ИЗОБРЕТЕНИЯ | 1973 |

|

SU377738A1 |

| Устройство для контроля интегральных схем | 1978 |

|

SU744579A1 |

| Система контроля параметров интегральных схем | 1977 |

|

SU746437A1 |

| Система автоматического контроля параметров | 1977 |

|

SU746435A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

| Устройство для автоматического контроля больших интегральных схем | 1981 |

|

SU1027735A1 |

| Многоканальное устройство для автоматического контроля микропроцессоров | 1982 |

|

SU1104519A1 |

| Устройство для контроля цифровых объектов | 1983 |

|

SU1160373A1 |

Изобретение относится к автоматизированным системам контроля и может быть использовано при контроле больших и сверхбольших интегральных схем на МОП-структурах. Цель изобретения - расширение функциональных возможностей путем обеспечения контроля объектов с произвольным временем выполнения операции. Устройство содержит генератор тактовых импульсов, управляющий вычислительный блок, группу элементов, блок памяти тестов, счетчик адреса памяти, регистр адреса тестовой комбинации, схему сравнения, регистр выходной тестовой комбинации, многоканальный амплитудный дискриминатор, счетчик числа повторения тестов комбинации, два элемента ЗИ, три элемента И, элемент НЕ, элемент ИЛИ, формирователь импульса, триггер. Принцип действия устройства состоит в блокировке синхроимпульсов, поступающих на вход синхронизации объекта контроля в тот момент, когда его состояние достигает значения, записанного в регистре выходной тестовой комбинации. Объект считается годным, если он достигает заданного состояния за время, меньшее указанного в счетчике числа повторений тестовых комбинаций. 1 ил.

.4 адреса контролируемой тестовой ком- 30 автоматической синхронизации высобинации номере комбинации. Регистр 5 выходной тестовой комбинации соединен с многоканальным амплитудным дискриминатором 7 для задания порога каждого канала дискриминатора.

На блок 3 из управляющего вычислительного блока 1 поступает импульс запроса. В каждой ячейке блока 3 выделены: один ряд разрядов, в котором записывается число циклов генератора 10, в течение которых на проверяемую схему должна поступать данная тестовая комбинация входных воздействий; дополнительный разряд, в котором за35

40

кого логического уровня. При считывании данной ячейки блока 3 на входы контролируемого объекта 6 подаются заданные входные воздействия, а максимальное число циклов (максимальное необходимое количество тактовых импульсов генератора 10, поступающее на вход объекта 6 для установки объекта в исходное состояние) переписывается в обратном коде в счетчик 8 числа повторения тестовых комбинаций через группу 9 элементов ЗИ. На счетный вход счетчика 8 подаются импульсы с генератора 10 через эле-

писывается сигнал разрешения для вклю-., мент ЗИ 11. Кроме того, эти импульсы чения режима автоматической синхро- через элемент И 14 поступают на второй вход контролируемого объекта 6. При совпадении выходной тестовой комбинации объекта 6 с записанной исходной тестовой комбинацией в регистре 5 с выхода многоканального амплитудного дискриминатора 7 через элемент НЕ 20 и элемент И 16 на триг- гер 19 поступает сигнал, изменяющий по переднему фронту его состояние. При этом сигналом низкого уровня с выхода триггера 19 запрещается поступление импульсов генератора 10 на синхровход контролируемого объекнизации работы контролируемого объекта 6 с системой контроля.

При считьтании ячейки блока 3 на входы контролируемого объекта 6 подаются заданные входные воздействия, а число циклов, в течение которых данные воздействия должны подаваться на контролируемый объект, переписываются в обратном коде в счетчик 8 числа повторения тестовых комбинаций через группу 9 элементов ЗИ. На счетный вход счетчика 8 подаются импульсы с генератора 10 через эле автоматической синхронизации высо

кого логического уровня. При считывании данной ячейки блока 3 на входы контролируемого объекта 6 подаются заданные входные воздействия, а максимальное число циклов (максимальное необходимое количество тактовых импульсов генератора 10, поступающее на вход объекта 6 для установки объекта в исходное состояние) переписывается в обратном коде в счетчик 8 числа повторения тестовых комбинаций через группу 9 элементов ЗИ. На счетный вход счетчика 8 подаются импульсы с генератора 10 через эле-

мент ЗИ 11. Кроме того, эти импульсы через элемент И 14 поступают на вто

рой вход контролируемого объекта 6. При совпадении выходной тестовой комбинации объекта 6 с записанной исходной тестовой комбинацией в регистре 5 с выхода многоканального амплитудного дискриминатора 7 через элемент НЕ 20 и элемент И 16 на триг- гер 19 поступает сигнал, изменяющий по переднему фронту его состояние. При этом сигналом низкого уровня с выхода триггера 19 запрещается поступление импульсов генератора 10 на синхровход контролируемого объекТА 6, так как последний выполнил заданную операцию. При заполнении с :етчика 8 наращивается на 1 счет- 41 :к 2 и через формирователь 18 импульса триггер 19 устанавливается в исходное состояние.

Если при заполнении счетчика 8

иггер 19 не изменил своего состоя- я (т.е., находится в исходном сос- янии), то сигнал с выхода счетчика через элемент ЗИ 13 и элемент -ИЛИ

поступает на вход управляющего В1 числительного блока 1 , сигнализиTIHI

тс

8

Г

Р of

я о неисправности

ъекте

Ф

ормулаиз обретения

Устройство для контроля цифровых объектов, содержащее управляющий вы- Ч1 слительный блок, счетчик адреса памяти, блок памяти тестов, регистр адреса тестовой комбинации, регистр . вьходной тестовой комбинации, многоканальный амплитудный дискриминатор, етчик числа повторения тестовых комбинаций, первьй элемент ЗИ, групэлементов ЗИ, генератор тактовой

стоты и схему сравнения, первый.

п

Ч

второй ВХОДЫ и выход которой соединены соответственно с выходом pert стра адреса тестовой комбинации, вьходом счетчика адреса памяти, сое- Д1- ненными с первым входом первого элемента ЗИ, первым входом прерыва- тя управляющего вычислительного бло- кг, первый, второй и третий инфор- м ционные выходы которого соединены

информационными входами регистра тестовой комбинации, счетчика ajpeca памяти, регистра выходной тесКС

pi ДС

B i П В5 Пс Т(

вой комбинации, первый,-второй и етий управляющие выходы управляютс

TI

щ€ ГО вычислительного блока соединены

ответственно с первым входом вы- бсра блока памяти тестов, первым входе м группы элементов ЗИ, вторым входе м первого элемента ЗИ, третий вход торого соединен с выходом генерато- тактовой частоты, а выход - с вхом.суммирования счетчика числа по- орения тестовой комбинации, выход реполнения которого соединен, с :одом суммирования счетчика адреса .мяти, вторым входом группыэлемен- iB ЗИ, вторым входом выбора блока

10

086976

памяти тестов, первая информационная группа выходов которого соединена . с третьими входами группы элементов ЗИ, вторая информационная группа выходов является выходом устройства, подключенного к информационным входам контролируемого объекта, адресный вход блока памяти тестов соединен с выходом счетчика адреса памяти, информационный вход счетчика числа ..

повторения тестовой комбинации соединен с выходами группы элементов ЗИ, первая и вторая группы входов ампли15 тудного дискриминатора соединены соответственно с входами устройства, к которым подключены .выходы контролируемого объекта и выходы регистра выходной тестовой комбинации, о т20личающееся тем, что, с целью расширения функциональных возможностей путем обеспечения контроля объектов с произвольным временем выполнения операции, в него введены вто25 рой элемент ЗИ, первый, второй, третий элементы И, элемент НЕ, формирователь импульса, триггер и элемент ИЛИ, первый, второй входы и выход которого соединены соответственно с выходом

30 второго элемента И, выходом второго элемента ЗИ, вторым входом прерывания управляющего вычислитель ного блока, первый и второй входы и выход первого элемента И соединены соответственно с выходом первого элемента ЗИ, первым входом второго элемента ЗИ и выходом триггера, синхровыходом устройства, который подключается к синхро- входу контролируемого объекта, первый и второй входы второго элемента И подключены соответственно к выходу схемы сравнения, выходу амплитудного дискриминатора и входу элемента НЕ, выход которого соединен с первым входом третьего элемента И, второй вход которого соединен с вторым входом второго элемента И и третьим информационным выходом блока памяти, вход фор- гдарователя импульса соединен с трет-ь- им входом второго элемента ЗИ и выходом переполнения счетчика числа повторения тестовой комбинации, вход сброса и вход установки триггера соединены соответственно с выходом треть - его элемента И и выходом формирова- теля импульса.

35

40

45

50

55

| Устройство для контроля дискретных объектов | 1978 |

|

SU711543A1 |

| ОПИСАНИЕ ИЗОБРЕТЕНИЯ | 0 |

|

SU377738A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| ПОРТСИГАР С ПРИСПОСОБЛЕНИЕМ ДЛЯ СКРУЧИВАНИЯ ПАПИРОС | 1922 |

|

SU621A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство | |||

Авторы

Даты

1990-11-23—Публикация

1988-08-01—Подача