1- . Изобретение относится к области автоматгйзированных систем контроля и может быть применено при контроле больших интегральных схем (БИС) и сверхбольших интегральных схем (СВИС на МОП-структурах. Известна система для автоматического контроля БИС, содержащая буферный быстродействующий запоминающий блок для хранения входных тестовых комбинаций и запоминания выходных сигналов, снимаемых с контролируемой схемы, в котором в качестве буферного запоминающего блока используется сдвиговый регистр 1. Недостатком цзвестной систем Я:вляется большой объем буферных запоминающих блоков и связанная с этим высркая стоимость систем контроля. Наиболее близким техническим решением к данному изобретению является система для автоматического контроля БИС, содержащая регистр конечного адреса, управляющую вычислитель ную машину (УВМ), регистр выходной тестовой комбинации, многоканальный амплитудный дискриминатор, схему сравнения, блок памяти, счетчик адреса памяти, счетчик числа повторени тестовых комбинаций, генератор такто ; -, / ВОЙ частоты и элементы И иНЕ - И, прйче МГ выходй УВМ соединены соответственно с входами регистра конечного адреса, счетчика,адреса памяти и блока памяти, выход регистра конечного адреса соединен с первым входом схемы сравнения, выход которой соединен с первыми входами УВМ и элемента И, выходы блока памяти соединены соответственно со входами регистра выходной тестовой комбинации и с первыми входами многоканального амплитудного дискриминатора, контролируемой БИС и элемента НЕ - И, выход которого соединен с первым входом счетчика числа повторений тестовых комбинаций, выход регистра выходной тестовой комбинации соединен со вторым входом многоканального амплитудного дискриминатора, третий вход которого соединен с выходом контролируемой БИС, а выход - со вторым входом УВМ, выход генератора тактовой частоты соединен со вторыми входами контролируемой БИС- и элеМента И, выход которого соединен со вторым входом счетчика числа псэвторений тестовых комбинаций, выход счетчика числа повторений тестовых комбинаций соединен со вторым входом счетчика

. адреса памяти, выход которого соединен со вторыми входамисхемы сравнения и блока памяти 2.

Недостаток этой системы в следующем.

В целом ряде случаев возникает неЪбходимость многократного повторения какой-либо группы входных тестовых комбинаций при контроле БИС, Известная система позволяет повторять одну тестовую комбинацию в течение какого-то числа циклов контроля БИС. При Ю повторяющихся группах тестов в буферны эапрминаиощий блок приходится записывать одинаковую информацию в разные адреса ЗУ.

Целью изобретения является расши- 15 рение функь иональных возможностей системы за счет учета регулярности тестОв.

Поставленная цель достигается тем, что в систему введены счетчик 20 циклов, счетчик признака циклов, триггер признака циклов, регистр восстановления адресаи четыре дополнительных элемента И, причем соответствующие выходы (5лока памяти соёди- 05 яены с первым и вторым входами первого дополнительного элемента И, с первыми входами триггера признака циклов, второго дополнительного эле1 ё;нта И ийчетчика признака циклов, .Выходы которого соединены соответственнр с третьим входом первого Дополнительного элемента И, со вторыми входами второго дополнительного элемента И l. эл(емейта НЕ - И и с первым входом третьего дополнительного эле- 35 мента И, выход второго допрлнительяргс элемента И соединен с первым входом сче тчика циклов, второй вход которого соединен с выходом первого ЯОП€Й1ниуельного элемента И, а выход -40 со вторым входом триггера признака циклов, йыходы триггера признака цик- лов соединены соответственно со вторым :вход6м Третьего дополнительного , элемента И и с первым входом четвер-45 того дополнительного элемента И, вход которого соединён с выходом счетчика адреса памяти, а выход - со входом регистра восстановления памяти, выход регистра восстановления па-д мятй соединен с третьим входом третьего дополнительного элемента И, выход которого соединен со вторьои входом счетчика адреса памяти.

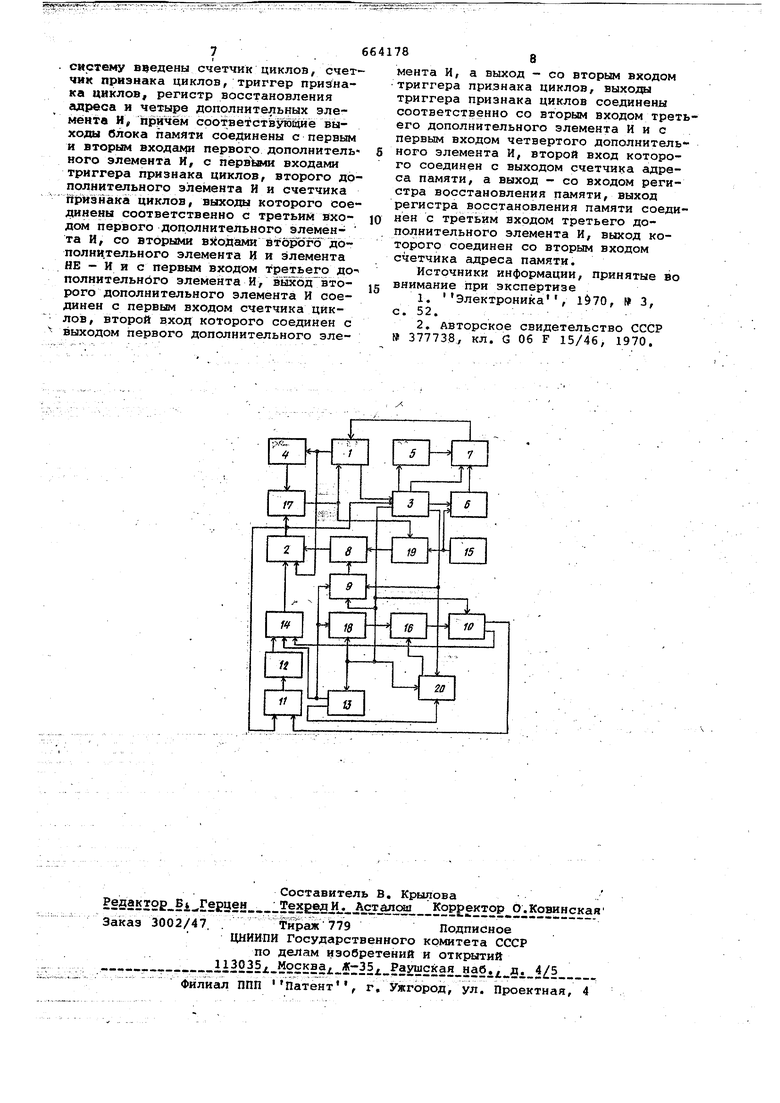

На чертеже представлена блок-схе- 55 ма предлагаемой системы для автомат Гйческого контроля БИС.

Предложенная система содержит: УВМ 1, счетчик 2 адреса памяти, блок 3 памяти, регистр 4 конечного CQ адреса, регистр 5 йыходной тестовой комбинации, контролируемая БИС 6, ногоканальный амплитудный дискриминатор 7, счетчик 8 числа повторений TectoBHX комбинаций, элемент НЕ - И 9, риггер 10 признака циклов, четвер- оЗ

тый лополнительный элемент И И, регистр 12 восстановления адреса, счетчик 13 признака циклов третий дополнительный элемент И 14, генератор 15 тактовой частоты, счетчик 16 циклов, схему 17 сравнения, второй дополнительный элемент И 18, элемент И 19, первый дополнительный элемент И 20, УВМ I соединена с многоканальным амплитуднцм дискриминатором 7, который соединен с выходом контролируемой большой интегральной ВИС б. Вход БИС 6 соединен с выходом блока 3 памяти, соединенного со счетчиком 2 адреса памяти. Вход регистра 4 конечного адреса соединен с УВМ 1. Входы схемы 17 сравнения соединены с регистром 4 конечного адреса и счетчиком 2 адреса памяти. Выход счетчика 8 Числа повторений тестовых комбинаций соединен со счетчиком 2 адреса памяти. Вход регистра 12 восстановления адреса соединен с выходом элемента И 11, один вход которого соединен с выходом счетчика 2 адреса памяти, а второй - с выходом триггера 10 признака циклов. Один вход триггера 10 признака соединен с выходом счетчика 16 циклов, а другой - с выходом блока 3 памяти,Один вход элемента И 18 соединен с вь1(ходом счетчика 13 признака циклов, а другой его вход и вход счетчика 13 признака циклов соединены с выходом блока 3 памяти. Выход регистра 12 восстановления адреса соединен с одним входом элемента И 14, другой вход которого соединен с выходом счетчика 13 признака циклов, третий - с выходом триггера 10 циклов, а выход - со входом счетчика 2 адреса памяти. Один вход счетчика 16 циклов соединен с выходом элемента И 18, второй - с выходом элемента И 20.

УВМ 1 передает, в счетчик 2 адреса памяти начальный адрес тестовых комбинаций, записанных в блоке 3 памяти, а в регистр 4 конечного адреса - последний адрес тестовых комбинаций для данного типа БИС, В регистр 5 выходной тестовой комбинации из блока 3 памяти поступает выходная тестовая комбинация каждого контролируемого теста исследуемой большой интегральной схемы 6, Регистр 5 соединен с многоканальным амплитудным дискриминатором 7 для задания порога каждого канала дискриминатора. В блок 3 памяти из УВМ 1 поступает импульс запроса. В каждой ячейке блока 3 памяти выделен ряд разрядов,в которых записывается число циклов тактового генератора, в течение которых на БИС б должна поаваться Данная тестовая комбинация входных воздействий и один разряд, в котором записывается признак циклов ля повторения группы тестов. При считывании из ячейки блока 3 памяти на рходы контролируемой БИС 6 подаются входные воздействия, а число циклов, в течение которых данные воздействия должны подаваться на контролируемую БИС 6, переписываются в обратном коде в счетчик 8 числа повторений тестовых комбинаций через элемент НЕ-И управляемый одноразрядным счетчиком 13 признака циклов. В этом случае, если в разряде блока 3 памяти, управ ляющем одноразрядным счетчиком 13 признака циклов, записан О, счет чик 13 находится в состоянии О, При этом открыт элемент НЕ-И 9 для заИиси числа повторений тестовых ком бинаций в счетчик 8. При этом импуль сы генератора 15 через элемент И 19 поступают на вход счетчика 8, при его заполнении наращивается на i значение счетчика 2 адреса памяти, и блок 3 памяти запрашивается по сле дующему адресу. В случае, если в раз ряде блока 3 памяти появляется первая единица (начало цикла), в од норазрядный счетчик 13 признака цикИнформация, лов записывается записанная в разрядах числа повторений блока 3 памяти, переписывается в счетчик 16 циклов через .элемент И 20. Одновременно перебрасывается триггер 10 признака циклов закрывает ся элемент И 11, и в регистре восста новления адреса 12 остается адрес начала цикла, который поступил со счетчика 2 адреса памяти через элемент И 11, при этом элемент И 14 зак рыт, Дсшее в ячейках блока 3 памяти в разряде, управляющем триггером 10 признака цикла, записываются О и контроль БИС 6 осуществляется, как описано вьиие. При появлении в одной из следующих ячеек блока 3 памяти . в разряде признака циклов, на вход одноразрядного счётчика 13 из блока 3 памяти поступает i и переводит счетчик 13 признака циклов Элемент И 14, в состояние управляемый триггером 10 признака цикла и счетчиком 13 признака циклов открывается, разрешая перепись инфор мации из регистра 12 восстановления адреса в счетчик 2 адреса памяти. При этом следующий запрос в блок 3 памяти прйизойдет по адресу счетчика 2 адреса памяти, т.е. целая группа тестов подаегся на БИС 6 из тех же ячеек 3 памяти, что и в пре дыдущем цикле. При этом в счетчик 16 циклов через открытый элемент И 18 добавляется . Повторение циклов работы блока памяти с одной и той же группой тестов будет происходить до тех пор, пока не произойдет переполнение счетчика 16 циклов. Импульс пе реполнения счетчики 16 сбросит триггер 10 признака циклов в исходное состояние. При появлении в разряде блока памяти признака окончания цикла закрывается элемент И 14, разреша щий перепись информации из регистра 6 g 12.восстановления адреса в счетчик 2 адреса памяти. Тогда в счетчик 2 адреса памяти добавится i с выхода счетчика, 8 повторений, и система контроля выйдет из цикла до появления признака начала следующего цикла. При совпадении информации в счетчике 2 адреса памяти и регистра 4 конечного адреса схема 17 сравнения закрывает элемент И 19, прекращается подача импульсов тактового генератора 15 и контроль БИС 6 заканчивается. При реализации данного устройства дпя контроля БИС возможна экономия объема буферного ЗУ, Объем ЗУ сокра2-6 раз и соответ-: тится примерно в стоимость ЗУ конственно снизится зависимости типа троля, которая в применяемого ЗУ может достигать значительных размеров. Формула изобретения Система для автоматического контроля больших интегральных схем (БИС), содержащая регистр конечного адреса, управляющую вычислительную машину (УВМ), регистр выходной тестовой комбинации, многоканальный амплитудный дискриминатор, схему сравнения, блок памяти, счетчик адреса памяти, счетчик числа повторений тестовых комбинаций, генератор тактовой частоты и элементы И к НЕ-И, причем выходы УВМ соединены соответственно с входами регистра конечного адреса, счетчика адреса памяти и блока памяти, выход регистра конечного адреса соединен с первы л входом схемы сравнения, выход которой соединен с первыми входами УВМ и элемента И, выходы блока памяти ,соединены соответственно со входами регистра выходной тестовой комбинации и с первыми вхо- дами многоканального амплитудного дискриминатора, контролируемой БИС и элемента НЕ-И, выход которого соединен с первым входом счетчика числа повторений тестовых комбинаций, выход регистра выходной тестовой комбинации соединенсо вторым входом многоканального амплитудного дискриминатора, третий вход которого соединен с выходом контролируемой БИС, а выход - со вторым входом УВМ, выход генератора тактовой частоты соединен со вторыми входами контролируемой БИС и элемента И, выход которого соединен со вторым входом счетчика числа повторений тестовых комбинаций, выход счетчика числа повторений тестовых комбинаций соединен со вторым входом счетчика адреса памяти, выход которого соединен со вторыми входами схемы сравнения и блока памяти, отличающаяся тем, что, р целью расширения функциональных воз-, можностей за счет обеспечения возможности учета регулярности тестов, в

систему введены счетчик циклов, счетчик признака циклов, триггер признака циклов, регистр восстановления адреса и четыре дополнительных элементе И, п рнчём соответствутаЩё выходы блока памяти соединены с первым и вторым аходам1И первого дополнительного элемента И, с первьвш входами триггера признака циклов, второго дополнительного элемента И и счетчика признака циклов, выходы которого соединены соответственно с третьим входом первого дополнительного элемента И, со вторыми в5содг1Ми второго дополни.тельного элемента И и элемента НЕ - И и с первым входом третьего до-i полнительнЬго элемента И выход второго дополнительного элемента И соединен с первым входом счетчика циклов, второй вход которого соединен с выходом первого дополнительного эле8

мента И, а выход - со вторым входом триггера признака циклов, выходы триггера признака циклов соединены соответственно со вторым входом третего дополнительного элемента И и с первым входом четвертого дополнитель ного элемента И, второй вход которого соединен с выходом счетчика адреса памяти, а выход - со входом регистра восстановления памяти, выход регистра восстановления памяти соединен с третьим входом третьего дополнительного элемента И, выход которого соединен со вторым входом счетчика адреса памяти.

Источники информации, принятые во внимание при экспертизе

1.Электроника , , 3, с. 52.

2.Авторское свидетельство СССР 377738, кл. G 06 F 15/46, 1970.

| название | год | авторы | номер документа |

|---|---|---|---|

| Система для автоматического контроля больших интегральных схем | 1983 |

|

SU1124331A2 |

| ОПИСАНИЕ ИЗОБРЕТЕНИЯ | 1973 |

|

SU377738A1 |

| Система контроля параметров интегральных схем | 1977 |

|

SU746437A1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1608697A1 |

| Система автоматического контроля параметров | 1977 |

|

SU746435A1 |

| Устройство для контроля интегральных схем | 1978 |

|

SU744579A1 |

| Устройство для контроля больших интегральных схем | 1986 |

|

SU1348835A1 |

| Система автоматического контроля параметров электронных схем | 1989 |

|

SU1700538A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU957279A1 |

| Устройство для контроля цифровых объектов | 1983 |

|

SU1160373A1 |

Авторы

Даты

1979-05-25—Публикация

1976-08-09—Подача