1

Изобретение относится к области автоматизированных систем контроля и может быть применено при контроле больших интегральных схем (БИС) и сверхбольших интегральных схем (СБИС) на МОП-структурах.

Известны системы автоматического контроля больших интегральных схем, содержаш;ие генератор тактовой частоты, управляющую вычислительную машину, соединенную с многоканальным амплитудным дискриминатором, запоминаюшим устройством, счетчиком адреса памяти, регистром выходной тестовой комбинации, соединенным с многоканальным амплитудным дискриминатором, который соединен с выходом контролируемой большой интегральной схемы, вход которой соединен с выходом запоминаюшего устройства, соединенного со счетчиком адреса памяти.

Однако для контроля больших интегральных схем на МОП-структурах с динамической логикой требуются быстродействующие управляющие цифровые вычислительные машины (ЦВМ) с большим объемом .памяти, которые могут обеспечить подачу на схему входных тестовых комбинаций и снятие выходных сигналов с контролируемой схемы с частотой, превышаюшей определенную величину для динамических схем. Кроме того, в известных системах отсутствует возможность контроля и

анализа результатов каждой произвольно выбранной тестовой комбинации.

С целью сокращения объема памяти быстродействующего запоминающего устройства входных тестовых комбинаций, а также обеспечения возможности контроля и исследования выходных сигналов любой тестовой комбинации в предлагаемую систему введены регистр адреса контролируемой комбинации,

вход которого соединен с управляющей вычислительной мащиной, схема сравнения, входы которой соединены с регистром адреса контролируемой комбинации и счетчиком адреса памяти, а выход с многоканальным амплитудным дискриминатором, счетчик числа повторений тестовых комбинаций, выход которого соединен со счетчиком адреса памяти и запоминающим устройством, два элемента «И, входы одного из которых соединены с запоминающим устройством, управляющей вычис лительной мащиной и выходом счетчика числа повторений тестовых комбинаций, а выход соединен со входами записи счетчика числа повторений тестовых комбинаций, входы другого

элемента «И соединены с генератором тактовой частоты, ВЫХОДОМ схемы сравнения и выходом управляющей вычислительной машины, а выходы соединены с контролируемой большой интегральной схемой и счетным входом

счетчика числа повторений тестовых комбинаций.

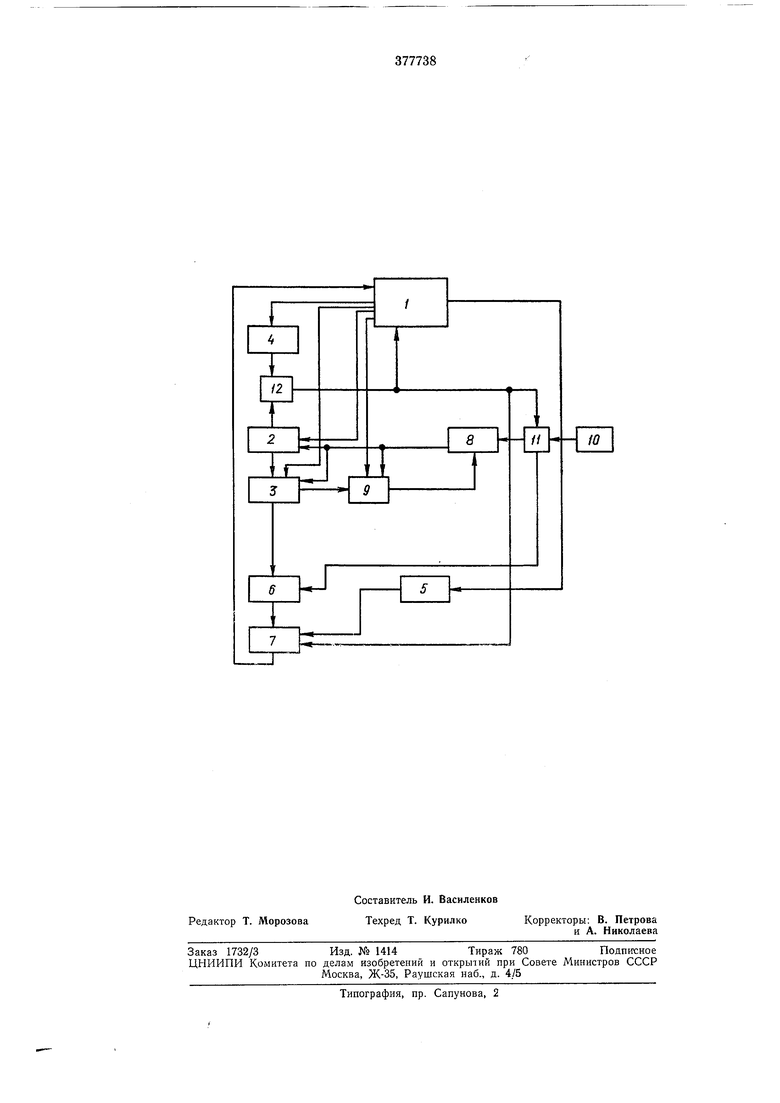

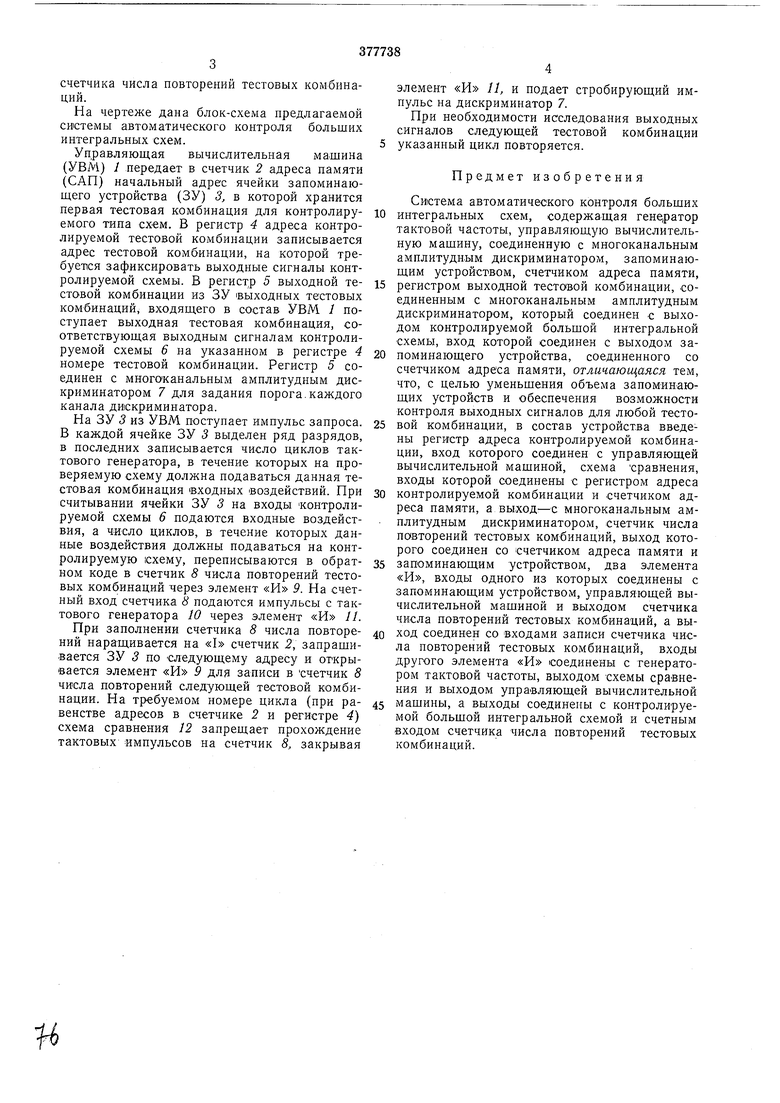

На чертеже дана блок-схема иредлагаемой системы автоматического контроля больших интегральных схем.

Унравляющая вычислительная машина (УВМ) 1 .передает в счетчик 2 адреса намяти (САП) начальный адрес ячейки запоминающего устройства (ЗУ) 3, в которой хранится первая тестовая комбинация для контролируемого типа схем. В регистр 4 адреса контролируемой тестовой комбинации записывается адрес тестовой комбинации, на которой требует1ся зафиксировать выходные сигналы контролируемой схемы. В регист,р 5 выходной тестовой комбинации из ЗУ выходных тестовых комбинаций, входящего в состав УВМ / поступает выходная тестовая комбинация, соответствующая выходным сигналам контролируемой схемы 6 на указанном в регистре 4 номере тестовой комбинации. Регистр 5 соединен с многоканальным амплитудным дискриминатором 7 для задания порога.каждого канала дискриминатора.

На ЗУ 3 из УВМ поступает импульс запроса. В каждой ячейке ЗУ 3 выделен ряд разрядов, в последних записывается число циклов тактового генератора, в течение которых на проверяемую схему должна подаваться данная тестовая комбинация сходных воздействий. При считывании ячейки ЗУ 3 на входы контролируемой схемы 6 подаются входные воздействия, а число циклов, в течение которых данные воздействия должны подаваться на контролируемую схему, переписываются в обратном коде в счетчик 8 числа повторений тестовых комбинаций через элемент «И 9. На счетный вход счетчика 8 подаются импульсы с тактового генератора 10 через элемент «И //.

При заполнении счетчика 8 числа повторений наращивается на «I счетчик 2, запрашивается ЗУ 3 по -следующему адресу и открывается элемент «И 9 для записи в счетчик 8 числа повторений следующей тестовой комбинации. На требуемом номере цикла (при равенстве адресов в счетчике 2 и регистре 4) схема сравнения 12 запрещает прохождение тактовых импульсов на счетчик 8, закрывая

элемент «И 11, и подает стробирующий импульс на дискриминатор 7.

При необходимости исследования выходных сигналов следующей тестовой комбинации указанный цикл повторяется.

Предмет изобретения

Система автоматического контроля больших

интегральных схем, содержащая гене ратор тактовой частоты, управляющую вычислительную машину, соединенную с многоканальным амплитудным дискриминатором, запоминающим устройством, счетчиком адреса памяти,

регистром выходной тестовой комбинации, соединенным с многоканальным амплитудным дискриминатором, который соединен с выходом контролируемой большой интегральной схемы, вход которой соединен с выходом запоминающего устройства, соединенного со счетчиком адреса памяти, отличающаяся тем, что, с целью уменьшения объема запоминающих устройств и обеспечения возможности контроля выходных сигналов для любой тестовой комбинации, в состав устройства введены регистр адреса контролируемой комбинации, вход которого соединен с управляющей вычислительной мащиной, схема сравнения, входы которой соединены с регистром адреса

контролируемой комбинации и счетчиком адреса памяти, а ВЫХОД:-с многОканальным амплитудным дискриминатором, счетчик числа повторений тестовых комбинаций, выход которого соединен со счетчиком адреса памяти и

запоминающим устройством, два элемента «И, входы одного из которых соединены с запоминающим устройством, управляющей вычислительной машиной и выходом счетчика числа повторений тестовых комбинаций, а выход соединен со входами записи счетчика числа повторений тестовых комбинаций, входы другого элемента «И соединены с генератором тактовой частоты, выходом -схемы сравнения и выходом упра-вляющей вычислительной

машины, а выходы соединены с контролируемой большой интегральной схемой и счетным входом счетчика числа повторений тестовых комбинаций.

| название | год | авторы | номер документа |

|---|---|---|---|

| Система для автоматического контроля больших интегральных схем | 1976 |

|

SU664178A1 |

| Система автоматического контроля параметров | 1977 |

|

SU746435A1 |

| Система контроля параметров интегральных схем | 1977 |

|

SU746437A1 |

| Система для автоматического контроля больших интегральных схем | 1983 |

|

SU1124331A2 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1608697A1 |

| Устройство для контроля интегральных схем | 1978 |

|

SU744579A1 |

| Устройство для контроля радиотехническихОб'ЕКТОВ | 1979 |

|

SU796859A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Устройство для контроля блоков памяти | 1978 |

|

SU717668A1 |

| Система автоматического контроля параметров электронных схем | 1989 |

|

SU1700538A1 |

Ц

Авторы

Даты

1973-01-01—Публикация