20

25

Изобретение относится к вычислительной технике и предназначено для использования во входных цепях систем сбора и отработки информации и я-вля- ется усовершенствованием устройства по авт.св. № 1238129.

Цель изобретения - повьппение по мехоустойчивости путем периодического обнуления счетчика во время отсутст-«Q ВИЯ входных сигналов.

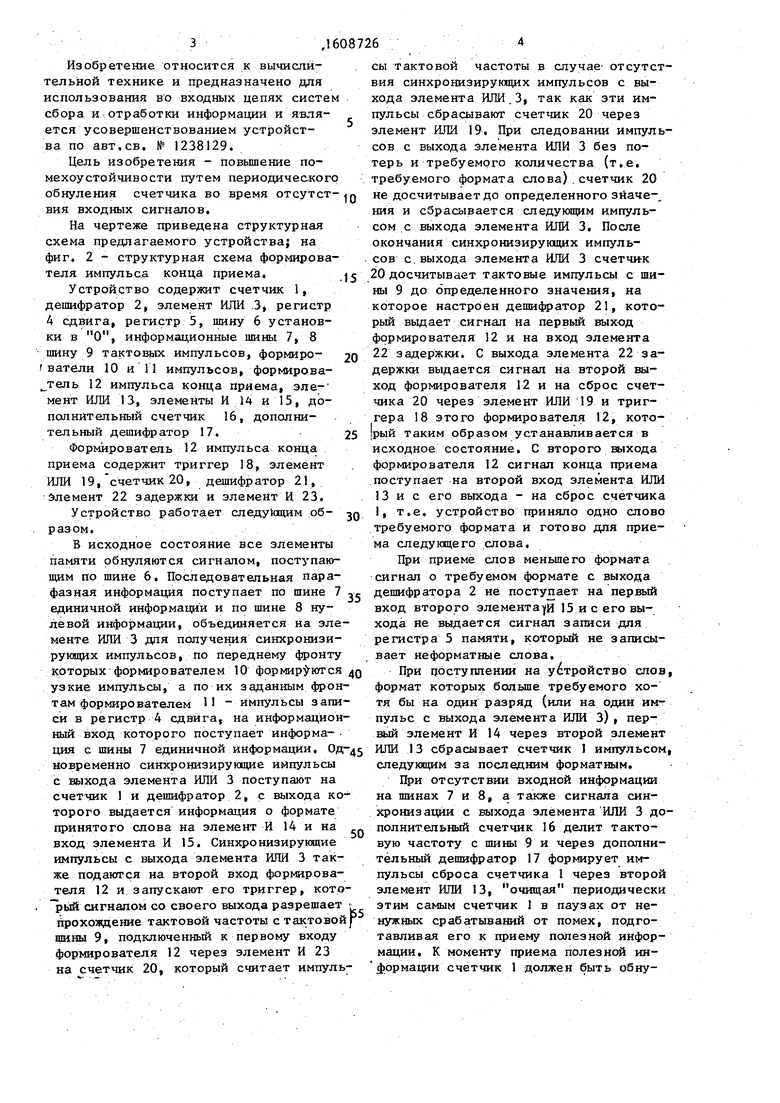

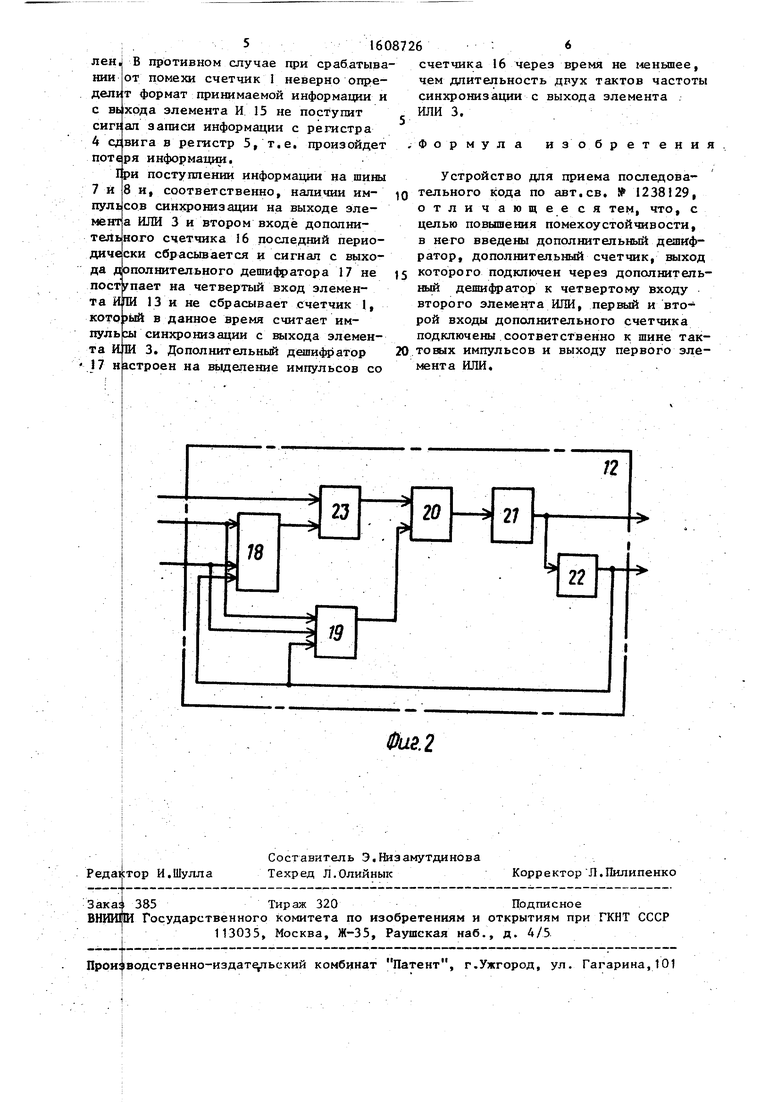

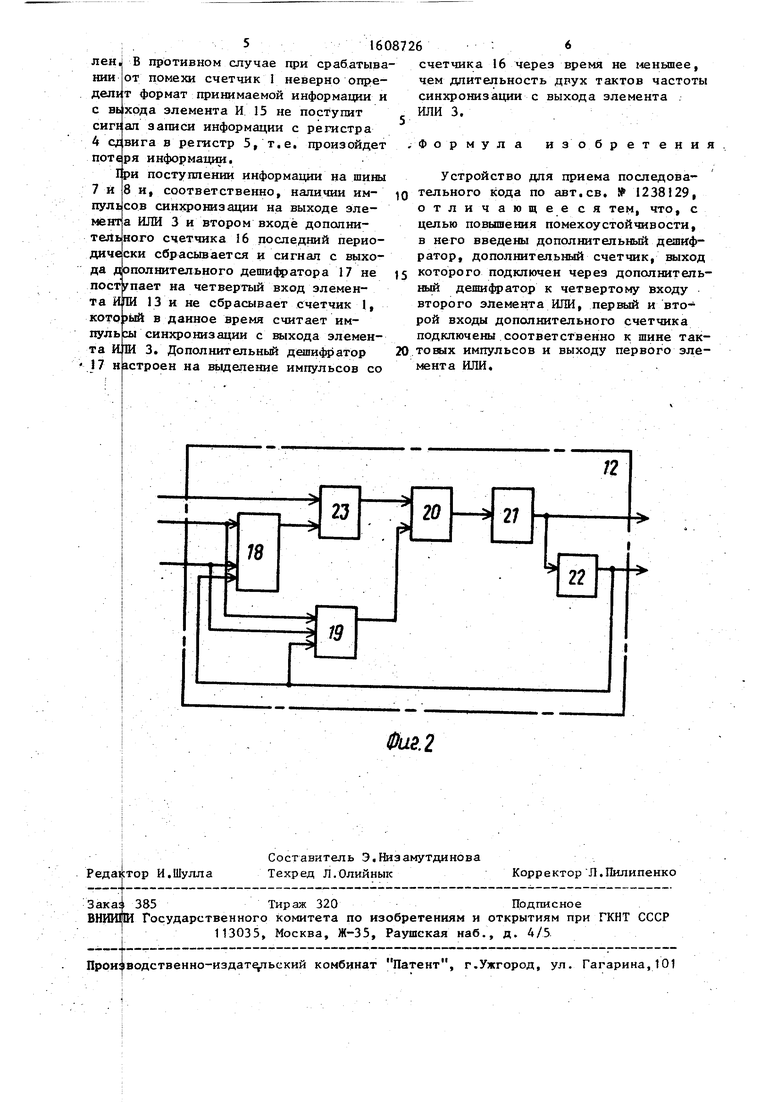

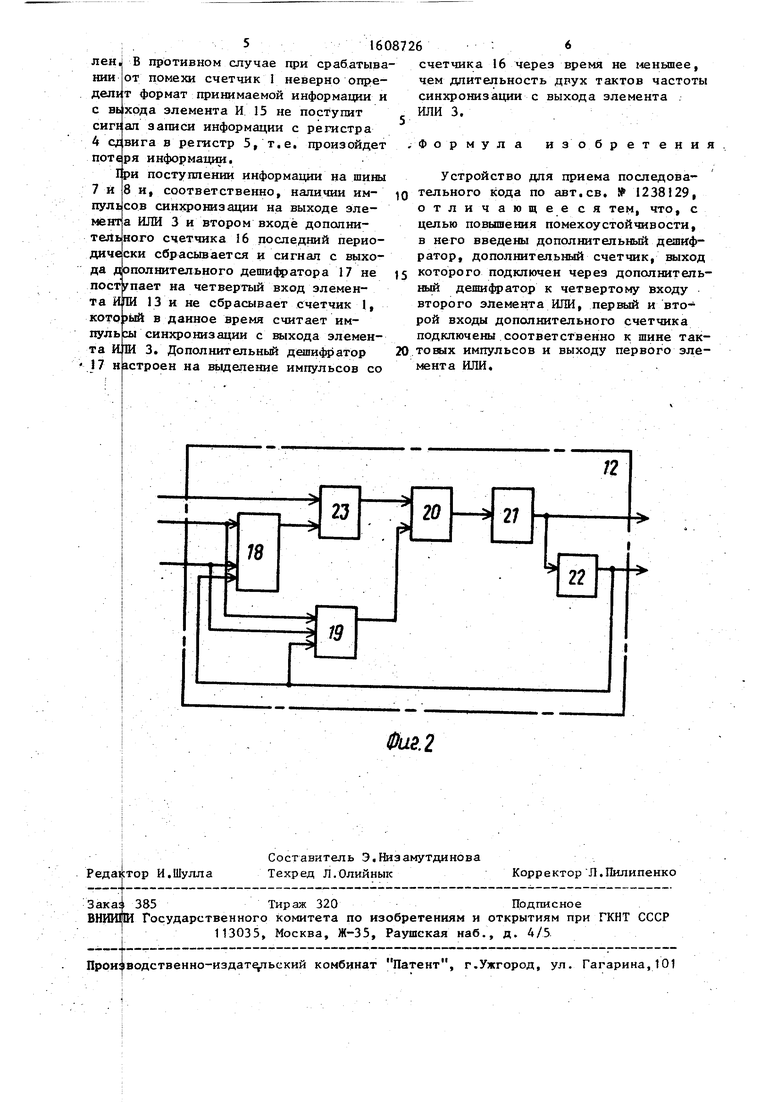

На чертеже приведена структурная схема предлагаемого устройства} на фиг. 2 - структурная схема формирователя импульса конца приема.

Устройство содержит счетчик 1, дешифратор 2, элемент ИЛИ .3, регистр 4 сдвига, регистр 5, ишну 6 установки в О, информационные шины 7, 8 шину 9 тактовых импульсов, формиро- ватели 10 и 11 импульсов, формирова- тель 12 импульса конца приема, эле- мент ИЛИ 13, элементы И 14 и 15, дополнительный счетчик 16, дополнительный дешифратор 17.

Формирователь 12 импульса конца приема содержит триггер 18, элемент ИЛИ 19, счетчик 20, дешифратор 21, Элемент 22 задержки и элемент И 23.

Устройство работает следуКщим образом.

В исходное состояние все элементы памяти обнуляются сигналом, поступающим по шине 6. Последовательная пара- фазная информация поступает по шине 7 единичной информации и по шине 8 нулевой инфо рмации, объединяется на элементе ИЛИ 3 для получения синхронизирующих импульсов, по переднему фронту которых формирователем 10 формир: ются до узкие импульсы, а по их заданным фронтам формирователем 11 - импульсы записи в регистр 4 сдвига, на информационный вход которого поступает информа- ция с шины 7 единичной информации. Од-дз новременно синхронизирующие импульсы с выхода элемента ИЛИ 3 поступают на счетчик 1 и дешифратор 2, с выхода которого выдается информация о формате принятого слова на элемент И 14 и на - вход элемента И 15. Синхронизируняцие импульсы с выхода элемента ИЛИ 3 также подаются на второй вход формирова,16087264

сы тактовой частоты в случае- отсутствия синхронизирующих импульсов с выхода элемента ИЛИ.З, так как эти импульсы сбрасывают счетчик 20 через элемент ИЛИ 19. При следовании импульсов с выхода элемента ИЛИ 3 без потерь и требуемого количества (т.е. требуемого формата слова) счетчик 20 не досчитывает до определенного зйаче- ния и сбрасывается следующим импульсом с выхода элемента ИЛИ 3. После окончания синхронизиругацих импульсов с.выхода элемента ИЛИ 3 счетчик J5 20 досчитывает тактовые импульсы с шины 9 до определенного значения, на которое настроен дешифратор 21, который вьщает сигнал на первый выход фсэрмирователя 12 и на вход элемента 22 задержки. С выхода элемента 22 задержки выдается сигнал на второй выход формирователя 12 и на сброс счетчика 20 через элемент ИЛИ 19 и триггера 18 этого формирователя 12, кото- 1рый т аким обр аз ом уст анавлив ает ся в исходное состояние. С второго выхода формирователя 12 сигнал конца приема поступает на второй вход элемента ИЛИ 13 и с его выхода - на сброс счетчика I, т.е. устройство приняло одно слово требуемого формата и готово дпя приема следующего слова.

При приеме слов меньшего формата сигнал о требуемом формате с выхода эс дешифратора 2 не поступает на первый вход второго элементами 15 и с его выхода не выдается сигнал записи для регистра 5 памяти, который не записывает неформатные слова.

При поступлении на устройство слов, формат которых больше требуемого хотя бы на один разряд (или на один импульс с выхода элемента ИЛИ З), первый элемент И 14 через второй элемент ИЛИ 13 сбрасывает счетчик 1 импульсом, следуютщм за последним форматным.

При отсутствии входной информации на шинах 7 и 8, а также сигнала синхронизации с выхода элемента ИЛИ 3 дополнительный счетчик 16 делит тактовую частоту с шины 9 и через дополнительный дешифратор 17 формирует импульсы сброса счетчика 1 через второй элемент ИЛИ 13, очищая периодически

30

теля 12 и запускают его триггер, котр- рый сигналом со своего выхода разрешает ,. этим самым счетчик I в паузах от не- йрохождение тактовой частоты с тактовойр нужных срабатываний от помех, подго- щины 9, подключенный к первому входу формирователя 12 через элемент И 23

тавливая его к приему полезной информации. К моменту приема полезной инна счетчик 20, который считает импуль- формации счетчик 1 должен быть обнуэтим самым счетчик I в паузах от не- нужных срабатываний от помех, подго-

тавливая его к приему полезной информации. К моменту приема полезной инлен, В противном случае при срабатываниидели с вь

СИГН

4 ср

счетчика 16 через время не меныпее, чем длительность двух тактов частоты синхронизации с выхода элемента ИЛИ 3.

от помехи счетчик 1 неверно формат принимаемой информации и

хода элемента И 15 не поступит

ал записи информации с регистра

вига в регистр 5, т.е. произойдет .Фор мул а изобр ет ения

потеря информации.

1ри поступлении информации на шины 7 и 8 и, соответственно, наличии импульсов син ф01шзации на выходе элемента ИЛИ 3 и втором входе дополнительного счетчика 16 последний периодически сбрасывается и сигнал с выхода дополнительного дешифратора 17 не пост| пает на четвертый вход элемента И ТИ 13 и не сбрасывает счетчик 1, который в данное время считает им- цульсы синхронизации с выхода элемента ИШ 3. Дополнительный дешифратор 17 настроен на вьщеление импульсов со

Устройство для приема последова- 0 тельного кода по авт.св. 1238129, отличающее ся тем, что, с целью повышения помехоустойчивости, в него введены дополнительный дешифратор, дополнительный счетчик, выход J5 которого подключен через дополнитель- нь1й дешифратор к четвертому входу . второго элемента ИЛИ, первый и второй входы дополнительного счетчика подключены.соответственно к шине так- 20 товых импульсов и выходу первого элемента ИЛИ..

счетчика 16 через время не меныпее, чем длительность двух тактов частоты синхронизации с выхода элемента ИЛИ 3.

Устройство для приема последова- 0 тельного кода по авт.св. 1238129, отличающее ся тем, что, с целью повышения помехоустойчивости, в него введены дополнительный дешифратор, дополнительный счетчик, выход J5 которого подключен через дополнитель- нь1й дешифратор к четвертому входу . второго элемента ИЛИ, первый и второй входы дополнительного счетчика подключены.соответственно к шине так- 20 товых импульсов и выходу первого элемента ИЛИ..

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема последовательного кода | 1984 |

|

SU1238129A1 |

| Приемник последовательного кода | 1988 |

|

SU1674378A1 |

| Устройство для приема последовательного кода | 1986 |

|

SU1354232A1 |

| Процессор программируемого контроллера | 1985 |

|

SU1406595A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для сопряжения двух ЭВМ | 1989 |

|

SU1681307A1 |

| СЕЛЕКТОР ИМПУЛЬСОВ ЗАДАННОЙ КОДОВОЙ КОМБИНАЦИИ | 1994 |

|

RU2076455C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Селектор импульсов заданной кодовой комбинации | 1987 |

|

SU1457169A1 |

| Процессор программируемого контроллера | 1988 |

|

SU1550515A2 |

Изобретение относится к вычислительной технике и предназначено для использования во входных цепях систем сбора и обработки информации. Цель - повышение помехоустойчивости. Устройство содержит регистр сдвига 4, регистр 5, счетчики 1, 16, дешифраторы 2, 17, элементы ИЛИ 3, 13, элементы И 14, 15, формирователи 10, 11, формирователь 12 импульса конца приема, шину 6 установки в нуль, шины 7, 8 информации и тактовую шину 9. Формирователь 12 формирует импульс, по которому происходит запись информации из регистра 4 сдвига в регистр 5 только в случае поступления информации нужного формата. Формат поступающей информации определяют счетчик 1 и дешифратор 2, разрешая прохождение импульса записи на регистр 5 через элемент И. Дополнительный счетчик 16 и дополнительный дешифратор 17 осуществляют периодическое обнуление счетчика 1 через элемент ИЛИ 13 при отсутствии информации, защищая этим самым счетчик 1 от ложных срабатываний от помех. 1 ил.

2J

18

Е

20

27

HIT

Фиг. 2

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

Авторы

Даты

1990-11-23—Публикация

1988-11-10—Подача