фигЛ

Изобретение отпоемте к импульсной технике, а именно к устройствам обработки информации, и может быть использовано в дешифраторах время-импузьеных кодов и позволяет задерживать регулярно поступающие сигналы, длительностью rn S 2T, с высокой точностью,

Целью изобретения является расширение функциональных возможностей за счет осуществления задержки сигналов, поступающих по двум входам при заданной точности.

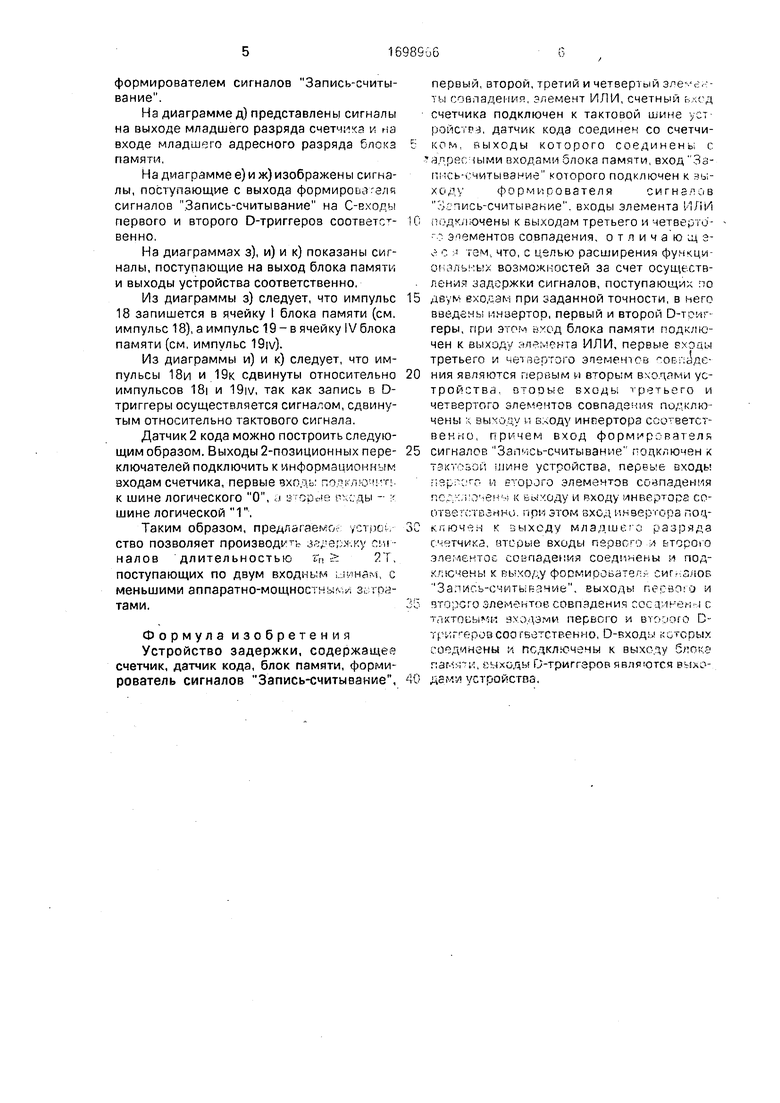

На фиг, 1 изображена структурная схема устройства задержки; на фиг. 2 - диаграммы, поясняющие работу устройства задержки.

Устройство задержки содержит сметчик 1, датчик 2 кода, блок 3 памяти, формирователь 4 сигналов Запись-считывание, первый 5, второй 6, третий 10 и четвертый 11 элементы совпадения, инвертор 7, первый 8 и второй 9 D-триггеры, элемент ИЛИ 12, входные шины 13,14, выходные шины 15, 16 и тактовую шину 17, при этом счетный вход счетчика 1 является тактовым входом устройства, датчик 2 кода соединен со счетчиком 1, выходы которого соединены с адресными входами блока 3 памяти, вход Запись-считывание которого подключен к выходу формирователя 4 сигналов Запись- счичывание входи - емента ИЛИ 12 подключены к выходам „етьего 10 и четвеото- О 11 элементов ссврь- емя, вход блока 3 памяти подключен к выход/ элемента У1Л1/1 12, первые входы -.ретьего 10 л четвертого 11 элементов совпадения явпяются входами устройства, Б горче входы rpcf -ern 10 А четвертого 11 элементов совпадения подключены к инвертору 7, вход формирователя 4 сигналов Запись-считывание подключен к тактовому входу устройства, первые входы первого Ь и второго 6 элементов совпадения подключены к инвертору 7, вход которого подключен к младшему разряду счетчика 1, вторые входы первого 5 и второго 6 элементов совпадения соединены и подключены к выходу формирователя 4 си налов Запись- считывание, выходы первого 5 и второго 6 элементов совпадения соединены с тактовыми входами первого 8 и второго 9 D-триг- геров соответственно, D-входы которых соединены и подключены к выходу блока 3 памяти, а выходы D-триггеров 8 и 9 являются выходами устройства.

зом.

Устройство работает следующим обраНа счетный вход счетчика 1 который соединен тактовой шиной 17 устройства,

поступают тактовые импульсы. Датчик 2 кода и соединенный с ним счетчик 1 форми у- ют задержку, величину Т которой мп -ic определить по формуле

,

где К - код, задаваемый датчиков 2 коде,

т-период следования тактовых импульсов.

Одновременно счетчик 1, выходы которого соединены с адресными входами блока 3 памяти, перебирает ячейки последнего Режим обоащ.,мя к б т,ку 3 памяти опреде ляется в завьиип/юсти от состояния входа Запись-считывание, который подключен к

выходу формирователя 4 сигналов Запись- считывание, вход которого подключен к тактовой шине 17 устройства. На вход блока 3 памяти, -оторый подключен к выходу элемента ИЛИ 12, поступают сигналы с первой или

второй входных шин 3,14устройства. Приэтом выбор одного из входов произвоаится при по мощи третьего 10 и четвертого 11 элементов совпадения, на первые входы которых поступают входные сигналы, а на вторые входы прямой и инверсный сигналы с младшего разряда счетчика 1. С выходов третьего 10 и четвертого 11 элементов совпадения сигналы поступают на входы элемента ИЛИ 12. ha первые входы первого 5 и второго 6 элеменSGBсовпадения поступают сигналы с инвертора 7, вход которого подключен к младшему разряду счетчика 1. На вторые ачоды аеового 5 i второго б элеменюв совпадем „ подаются сигналы с выхода фсрмировагелч 1 сигналов Запись-считывание. На выходах первого 5 и оторого 6 элементов совпадения формируется сигналы Запись, частота следований которых в два раза меньше частоты следования сигнааов

Запись-считывание Эти сигналы поступают на тактовые входы первого 8 и второго 9 D-триггеоов соответственно и одним из фронтов производят запись состояния выбранной з данный момент времени 1чейки

блока 3 памяти в D-триггеры, D-входы которых соединены и подключены к выходу блока 3 памяти. С выходов D-триггеров 8 и 9 задержанные сигналы поступают на выходные шины 15, 16 устройства.

На диаграммах а) и б) представлены входные сигналы длительностью гп 2Т, поступающие соответственно на первую и вторую входные шины 13.

На диаграмме в) показаны тактовые импульсы, поступающие на тактовый вход устройства.

На диаграмме г) изображены сигналы Запись-считывание, вырабатываемые

формирователем сигналов Запись-считывание.

На диаграмме д) представлены сигналы на выходе младшего разряда счетчика и из входе младшего адресного разряда блокз памяти.

На диаграмме е) и ж) изображены сигналы, поступающие с выхода формирователи сигналов Запись-считывание на С-входы первого и второго D-триггероз соответст- венно.

На диаграммах з), и) и к) показаны сигналы, поступающие на выход блока памяти и выходы устройства соответственно.

Из диаграммы з) следует, что импульс 18 запишется в ячейку I блока памяти (см. импульс 18), а импульс 19-в ячейку IV блока памяти (см. импульс 19iv).

Из диаграммы и) и к) следует, что импульсы 18и и 19к сдвинуты относительно импульсов 18| и 19iv, так как запись в D- триггеры осуществляется сигналам, сдвинутым относительно тактового сигнала.

Датчик 2 кода можно построить следующим образом. Выходы 2-позиционных пере- ключателей подключить к информационным входам счетчика, первые входы подключить к шине логического О, L ооые пхс-ды - шине логической 1.

Таким образом, предлагаемое устрсд,- ство позволяет производить задержку сигналов длительностью гп 27, поступающих по двум входным шинам, с меньшими аппаратно-мощностны.г, затратами.

Формула изобретения Устройство задержки, содержащее счетчик, датчик кода, блок памяти, формирователь сигналов Запись-считывание.

тз;г. пзр

первый, второй, третий и четвертый зле -- с.-:- ты совпадения, элемент ИЛИ, счетный ьлод счетчика подключен к тактовой шине уст- ройсггч, датчик кода соединен со счетчиком, выходы которого соединены с адрес (ыми входами блока памяти, вход Зз- ппсьч читывэние которого подключен к ны- формирователя сигналов о гшсь-считывание. входы элемента ИЛИ подключены к выходам третьего и четверто- о элементов совпадения, о т л и ч а ю щ э- . с тэм, что, с целью расширения фум-сци- оь ль - btx возможностей за счет осуществления задержки сигналов, поступающих по деу ехо.сам при заданной точности, в него введены инвертор, первый и второй D-триг- геры, при этом вход блока памяти подключен к выходу элемента ИЛИ, первые третьего и четвертого элементов ОЕпаде- ния являются первым и вторым входами устройства, вторые входы третьего и четвертого элементов совпадения подключены ч выходу и входу инвертора ссотеетст- венно, причем вход формирователя сигналов Запись-считывание подключен к и тине устройства, первые входы n9p. и второго элементов совпадения г.с:. :,.-1 : выходу и входу инвертора со- отоегствзино. при этом вход инвертора поц- кпючен к выходу младшего разряда с -«тчикэ, нтсоые входы первсго и &TOPOIO злепентос совпадения соединены и лод- кг;Ю - ены с выходу фоомироьйтел С.ИП-.ЗЛОБ Зались-очитыБЗние, выходы первого и второго элементов совпадения соединена г ыктоиыми зходами первого и второго D- Т(. 1;ггеровсоогБетствен - 0, D-вход:-.1 которых соодмнены и подключены к выходу блока rsat-v-n-u D-триггэров являются еыло- аму устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство задержки | 1989 |

|

SU1767696A1 |

| Устройство для телеизмерения давления скважинных штанговых насосов | 1990 |

|

SU1711218A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Программируемый формирователь управляющих воздействий микропроцессорной системы | 1989 |

|

SU1725210A1 |

| Логический анализатор | 1988 |

|

SU1654822A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

| Устройство задержки | 1990 |

|

SU1750036A1 |

| Система управления многопозиционной индукционной нагревательной установкой | 1983 |

|

SU1121789A1 |

Изобретение относится к импульсной технике, в частности к устройствам обработки информации, и может быть использовано в дешифраторах время-импульсных кодов. Цель - расширение функциональных возможностей за счет осуществление задержки сигналов, поступающих по двум входам. Устройство задержки содержит счетчик 1, датчик 2 кода, блок 3 памяти, формирователь 4 сигналов Запись-считывание, первый 5, второй 6, третий 10 и четвертый 11 элементы совпадения, элемент ИЛИ 12, инвертор 7, первый 8 и второй 9 D-триггеры, входные шины 13, 14, выходные шины 15, 16 и тякто- вую шину 17. Наличие инвертора 7 обеспечивает поочередное формирование управляющих сигналов, с помощью которых D-триггеры 8, 9 записывают разделенную информацию, поступающую с выхода блока 3 памяти. Поочередное подключение входных шин 13, 14 обеспечивает поочередное выполнение задержки. 2 ил.

s

ла&жвсаЕиы а jmcmKaetauzq р ™га дуг-дд ддрьдхтлаиамв длшшии и mr «пююмвм

ЛГЛ,.ПГТГТ LT

т JTin JlinJLJ lzn /.

жжпя.г.шлойгакз1 1-QfrarrmMl ттг imiJinn 111 ran i J1 i «имя f

U LT

/с

Г

Л II IIJI 1Р1.1.И IIII.J..HIIII«

SCC8U

tbff«w J

ZLJnLJT

-f

и

-%е

| Авторское свидетельство СССР № 1182647, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-12-15—Публикация

1989-10-02—Подача