jj.r |4.г JJ.2|4.2 J3.y|4.r OLA7 ) А7 Ат 5.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1989 |

|

SU1688238A1 |

| Устройство для умножения | 1989 |

|

SU1714592A1 |

| Матричный умножитель по модулю чисел Ферма | 1990 |

|

SU1783513A1 |

| Устройство для умножения | 1988 |

|

SU1603379A1 |

| Вычислительное устройство | 1987 |

|

SU1509872A1 |

| Вычислительное устройство | 1983 |

|

SU1117635A1 |

| Матричное вычислительное устройство | 1982 |

|

SU1034032A1 |

| Матричное устройство для вычисления тригонометрических функций | 1984 |

|

SU1226448A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU938282A1 |

| Устройство для умножения | 1989 |

|

SU1697078A1 |

Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных арифметических узлах. Цель изобретения - повышение достоверности вычислений матричного умножителя. Умножитель содержит матрицу 1 элементов И и матрицу 2 одноразрядных сумматоров. Умножитель содержит К+1 избыточный столбец и позволяет исключить из работы область неисправных узлов умножителя, ограниченную К столбцами матрицы. Множимое и множитель подаются на входы 4,5 матричного умножителя, округленный результат снимается с выходов групп 6,7 матричного умножителя. При обнаружении неисправной области матрицы она включается в нерабочую зону, изменяется подключение разрядов множимого к разрядам входа 4 умножителя, а на разряды входа 3 отключения столбца умножителя соответствующие столбцам нерабочей зоны, подается нулевой сигнал. 4 ил.

&

7

л.

Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных арифметических узлах.

Целью изобретения является повышение достоверности вычислений матричного умножителя.

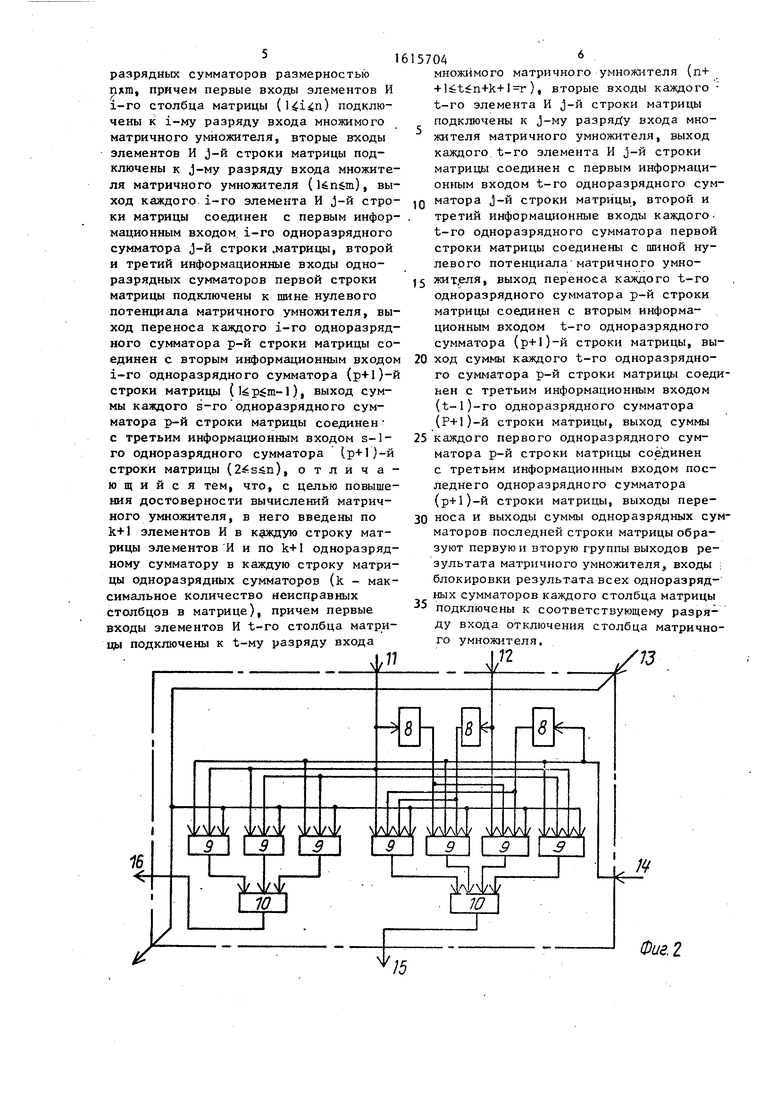

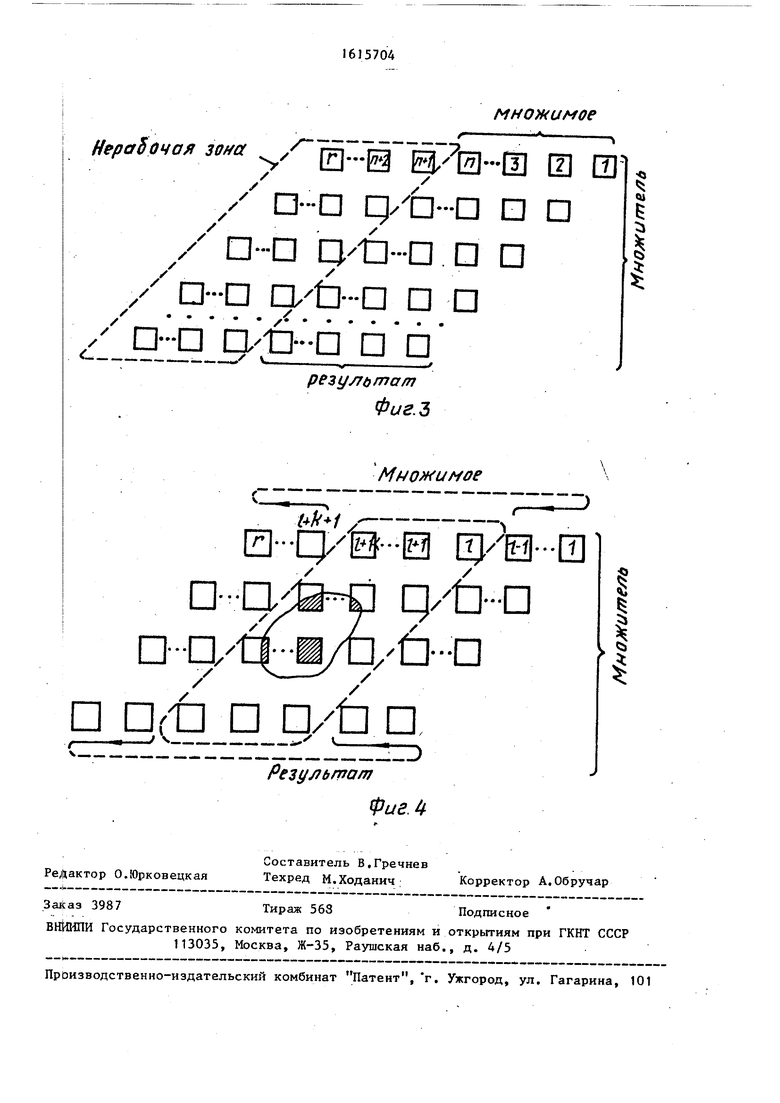

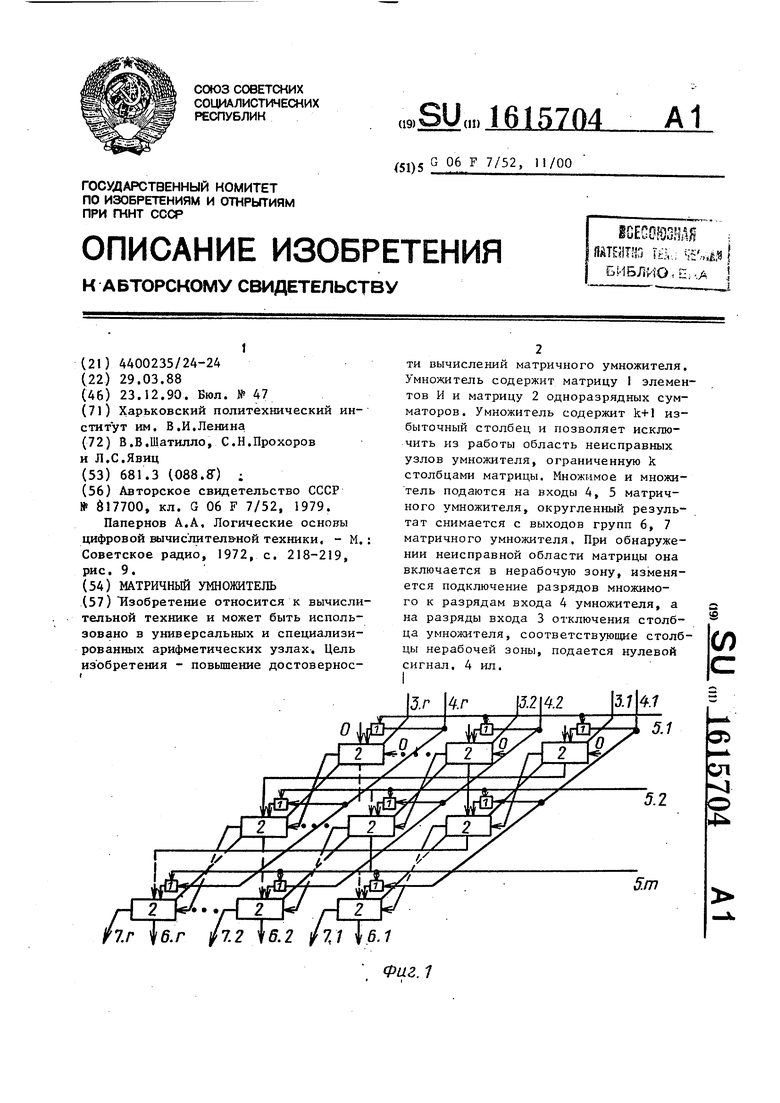

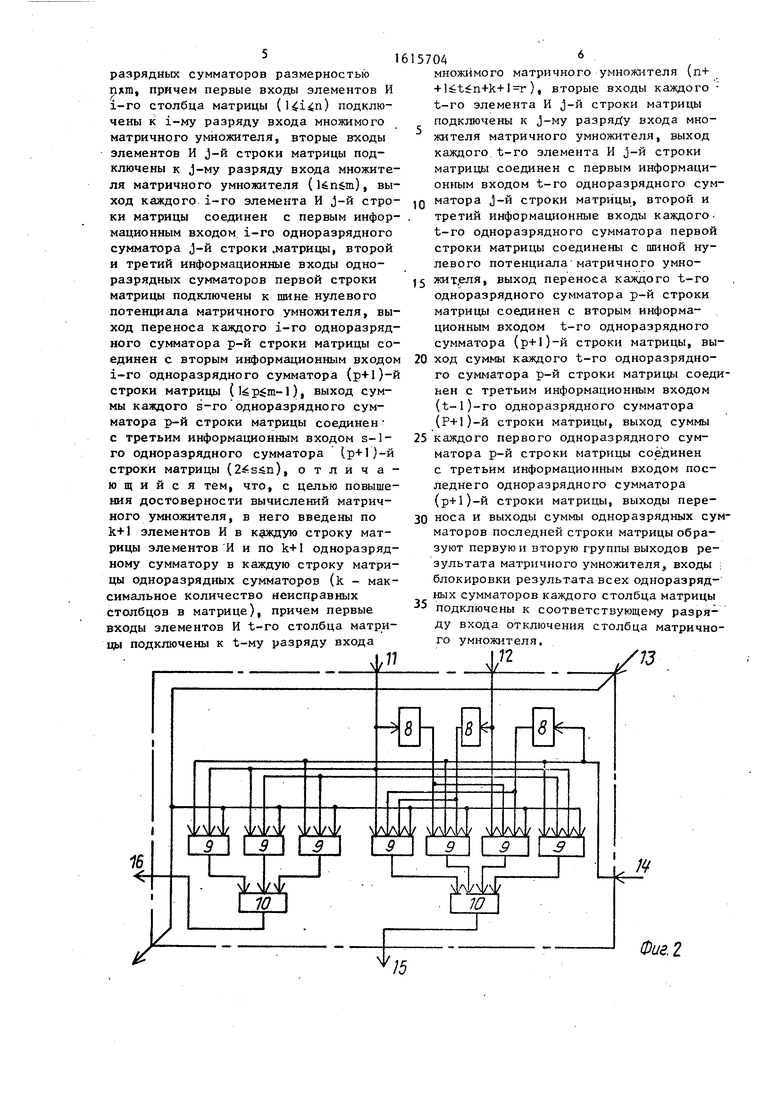

На фиг. 1 приведена функциональная схема матричного умножителя; на фиг. 2 - функциональная схема одноразрядного сумматора матричного умножителя; на фиг. 3 и 4 - положение рабочей и нерабочей зон матричного умножителя при отсутствии и наличии неисправности соответственно.

Матричный умножитель содержит матрицу 1 элементов И, матрицу 2 одноразовых сумматоров, вход 3 отключения столбцов матричного умножителя, входы 4 и 5 множимого и множителя матричного умножителя соответственно, вторую и первую группы 6 и 7 выходов результата матричного умножителя.

Одноразовый сумматор матрицы 2 (фиг. 2) содержит группу элементов НЕ 8, группу элементов И 9, группу элементов ИЛИ 10, третий и первый информационные входы 11 и 12 одноразрядного сумматора матрицы 2, вход 13 блокировки результата одноразрядного сумматора матрицы 2, второй информационный вход 14 одноразрядного сумматора матрицы 2, выходы 15 и 16 суммы и переноса одноразрядного сумматора: матрицы 2.

Матричный умножитель позволяет получить правильный результат вычислений при наличии в матричном умножителе области неисправных ячеек, ограниченной k столбцами матричного умножителя. Это достигается за счет введения аппаратной избыточности в виде (k+l) столбцов матричного умножителя и за счет замыкания матричного умножителя в кольцо. Область матричного умножителя, ограниченную столбцами, в которой пр оисходят вычисления, называют рабочей зоной матричного умножителя, оставшуюся избыточную часть, ограниченную (k+l) столбцами, - нерабочей зоной матричного умножителя.

Матричный умножитель работает следующим образом.

Работу матричного умножителя рассмотрим при отсутствии в ней неисправных узлов и при исправных входах 4 и 5 множимого и множителя.

Положение рабочей и нерабочей зон произвольное, т.е. рабочая зона ограничивается столбцами либо с первого по п-й, либо с второго по (п+1)-й, либо с (k+l)-ro по (n+k+l)-й, либо с (k+l)-ro по первый и т.д.

Пусть рабочая зона ограничена столбцами с первого по п-й (фиг. 3).

В исходном состоянии разряды с (п+1)- го по (n+k+l)-й входа 3 отключения столбца матричного умножителя подключаются к шине нулевого потенциала, разряды с первого по п-й входа 3 подключены к шине единичного потенциала.

Подача нулевого сигнала на соответствующий разряд вхЬда 3 приводит к тому, что на выходах переноса и суммы одноразрядных сумматоров матриЦы 2 этого столбца будут нулевые сигналы независимо от того, какие сигналы поступают на их информационные входы.

Таким образом, исключается влияние нерабочей зоны на рабочую. На входы 4 и 5 подаются множимое и мно- житель. Через некоторое время, определяемое переходными процессами, на выходах результата групп 6 и 7 появляется результат умножения. Результат получается округленным, так как (m-il) младших разрядов, результата j отбрасываются (т - разрядность множителя).

При наличии неисправных узлов матричный умножитель работает следующим образом.

Будем полагать, что область неисправных узлов определена, например, путем тестирования. Нерабочая зона,

ограниченная (k+l) столбцами, совмещается с локализованной областью неисправных узлов, ограниченной k столбцами, таким образом, чтобы крайний справа столбец нерабочей зоны не содержал неисправных узлов. Работа матричного умножителя в данном случае отличается от рассмотренного случая положением рабочей и нерабочей зон и разрядами входа 3 множимого, на которые подается множимое, и выходами групп 6 и 7, с которых снимается результат (фиг. 4).

Формула изобретения

Матричный умножитель, содержащий матрицу элементов И размерностью nxm (п - разрядность множимого, m - раз- рядност ь множителя) и матрицу одно51

разрядных сумматоров размерностью nxm, причем первые входы элементов И i-ro столбца матрицы () подключены к i-му разряду входа множимого матричного умножителя, вторые входы элементов И j-й строки матрицы подключены к j-му разряду входа множителя матричного умножителя (), выход каждого i-ro элемента И j-й строки матрицы соединен с первым информационным входом, i-ro одноразрядного сумматора j-й строки .матрицы, второй и третий информационные входы одноразрядных сумматоров первой строки матрицы подключены к шине нулевого потенциала матричного умножителя, выход переноса каждого i-ro одноразрядного сумматора р-й строки матрицы соединен с вторым информационным входом i-ro одноразрядного сумматора (р+1)-й строки матрицы (), выход суммы каждого з-го одноразрядного сумматора р-й строки матрицы соединен с третьим информационным входом s-1- го одноразрядного сумматора (р+1)-й строки матрицы (.n), отличающийся тем, что, с целью повышения достоверности вычислений матричного умножителя, в него введены по k+1 элементов И в каждую строку матрицы элементов И и по k+1 одноразрядному сумматору в каждую строку матрицы одноразрядных сумматоров (k - максимальное количество неисправных столбцов в матрице), причем первые входы элементов И t-ro столбца матрицы подключены к t-му разряду входа

0

5704

МНОЖ1ЖОГО матричного умножителя (п+

+ l t n+k+l T), вторые входы каждого t-ro элемента И j-й строки матрицы подключены к j-му разряду входа множителя матричного умножителя, выход каждого t-ro элемента И j-й строки матрицы соединен с первым информационным входом t-ro одноразрядного сумматора j-й строки матрицы, второй и третий информационные входы каждого, t-ro одноразрядного сумматора первой строки матрицы соединены с шиной нулевого потенциала матричного умно5 жит,еля, выход переноса каждого t-ro одноразрядного сумматора р-й строки матрицы соединен с вторым информационным входом t-ro одноразрядного сумматора (р+1)-й строки матрицы, вы0 ход суммы каждого t-ro одноразрядного сумматора р-й строки матрицы соединен с третьим информационным входом (t-l)-ro одноразрядного сумматора (Р+1)-й строки матри-цы, выход суммы

5 каждого первого одноразрядного сумматора р-й строки матрицы соединен с третьим информационным входом последнего одноразрядного сумматора (р+1)-й строки матрицы, выходы пере0 носа и выходы суммы одноразрядных сумматоров последней строки матрицы образуют первую и вторую группы выходов результата матричного умножителя, входы , блокировки результата всех одноразрядных сумматоров каждого столбца матрицы подключены к соответствующему разряду входа отключения столбца матричного умножителя.

5

НераЬочоя soffd /

/ п-п D D /п-п р-б-п п п

/ D-D а 6-П п п

X

crl.Qi -S- &S.-Q

результат Фие.Ъ

D-O

D-g

/гЧ

П

ru

S. V.

PnyjJbrrjam

множимое

D D п

(U

Мн осиное

7J

| Видоизменение лесов | 1929 |

|

SU17700A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Папернов А.А, Логические осноны цифровой вычис лител&ной техники, - М | |||

| : Советское радио, 1972, с | |||

| Прибор для измерения силы звука | 1920 |

|

SU218A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1990-12-23—Публикация

1988-03-29—Подача