сл

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Широкодиапазонный логарифмический аналого-цифровой преобразователь | 1988 |

|

SU1580557A1 |

| Устройство для сопряжения микро-ЭВМ с табло индикации | 1986 |

|

SU1376090A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ СЛОЖНЫХ СИГНАЛОВ | 1988 |

|

SU1841042A1 |

| Устройство для передачи и приема информации по двупроводной линии связи | 1990 |

|

SU1836709A3 |

| Устройство для контроля аналоговых объектов | 1986 |

|

SU1397941A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1676103A1 |

| Преобразователь последовательного кода в параллельный | 1987 |

|

SU1481901A1 |

| Анализатор экстремумов | 1984 |

|

SU1196810A1 |

| ДИСКРЕТНО-АНАЛОГОВЫЙ СИНУС-ГЕНЕРАТОР | 1995 |

|

RU2108657C1 |

| Интегрирующий преобразователь напряжения в код | 1986 |

|

SU1410275A1 |

Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах контроля аналоговых электрических схем и для ввода аналоговой информации в ЭВМ. Цель изобретения - расширение области применения устройства путем автоматической подстройки шага квантования при изменении частоты исследуемого сигнала. Устройство содержит АЦП 1, регистр 2, блок оперативной памяти 3, генератор импульсов 5, счетчики 4 и 18, компаратор 6, элементы И-НЕ, шесть триггеров, элемент ИЛИ, элемент ИЛИ-НЕ, элементы И, элемент НЕ 7. 4 ил.

а vi к

Јь

со

Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах контроля аналоговых электрических схем и для обработки на ЭВМ аналоговых сигналов.5

Целью изобретения является расширение области применения устройства за счет автоматической подстройки шэо квантования при изменении частоты исследуемого сигнала.10

В течение первого периода входного аналогового сигнала на выходах второго счетчика накапливается код

ЛА КТ0

где ТА - период входного аналогового сигнала;

То - период сигнала тактового генерато- ра;

К - двоичный код, установленный на входах СО, С1С(К-1) устройства.

В течение второго периода входного сигнала работа первого и второго счетчиков запрещается, а число кодов выборок входного аналогового сигнала, записанных в ОЗУ, следующее:

2 ТА

Тг

ТА

Как видно из равенства (2), число кодов выборок входного сигнала не зависит от периода этого сигнала, а шаг квантования, с которым коды выборок заносятся в ОЗУ, прямо пропорционален периоду сигнала

Ткв 2 Tn L 2 Тс

2 ТА 4п.

(3)

где Ткв - период квантования.

Таким образом,устройство автоматически подстраивает период квантования под частоту входного аналогового сигнала так, что в ОЗУ всегда записывается К выборок за один период, где число К задается входным кодом. Отсюда видно, что устройство может работать в широком диапазоне частот, что и определяет расширение области примене- ния устройства.

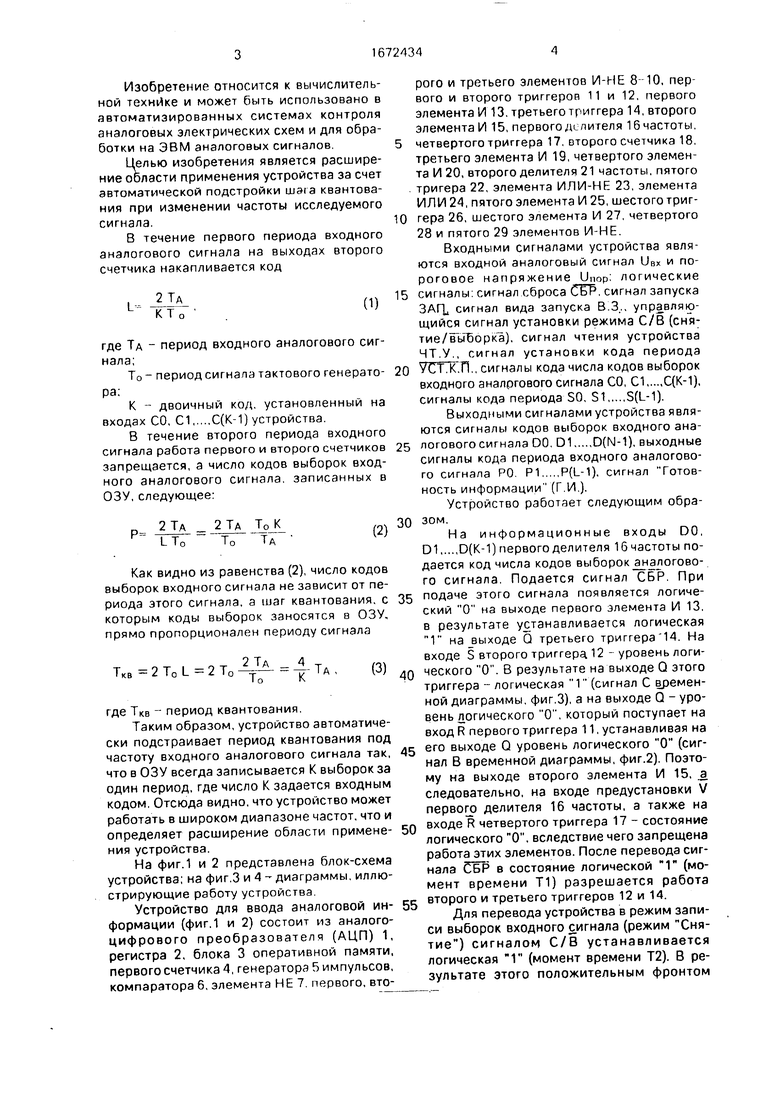

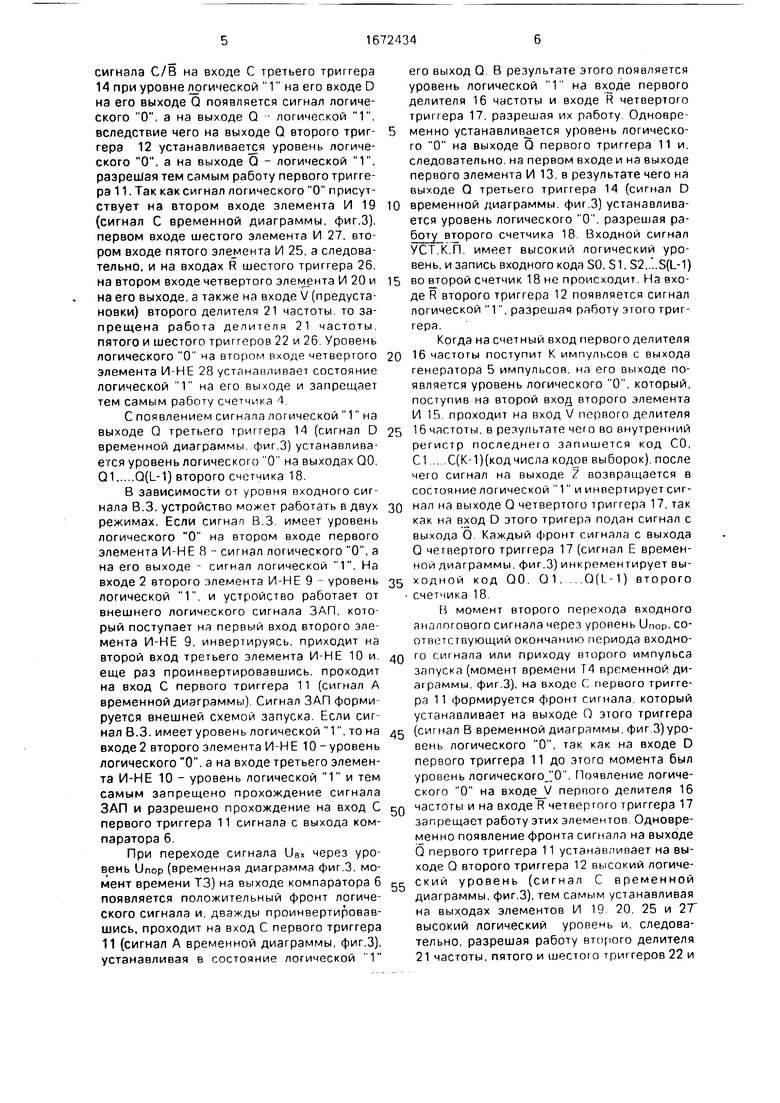

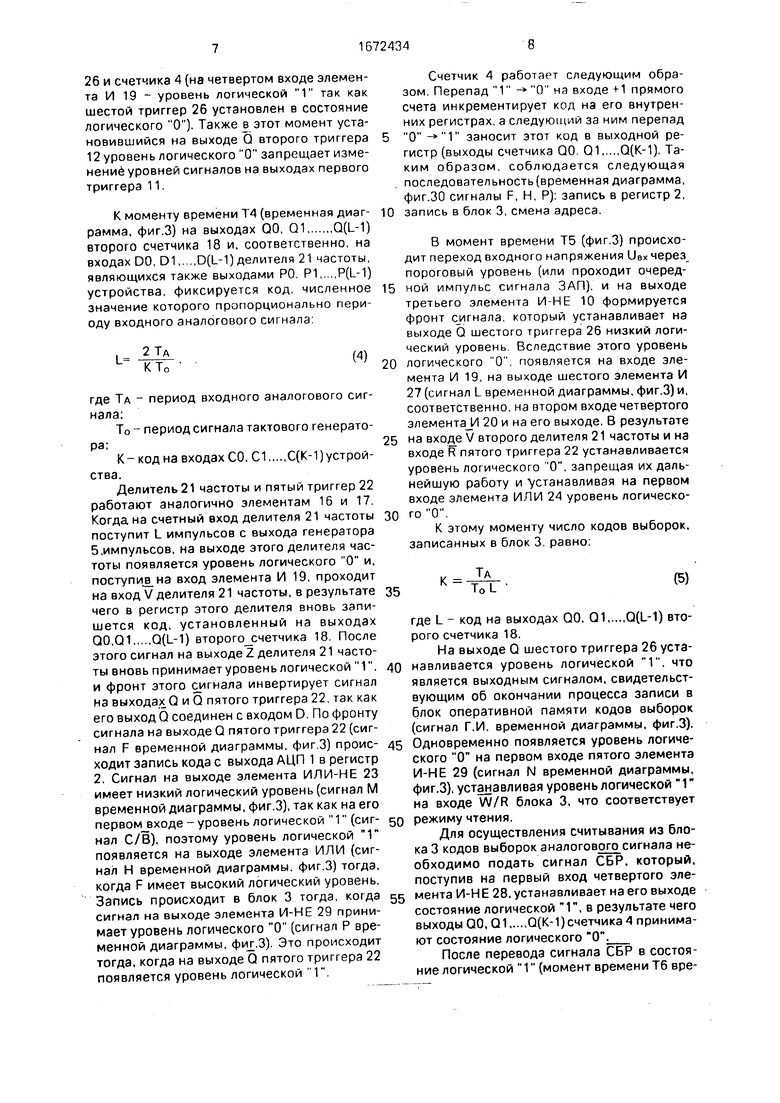

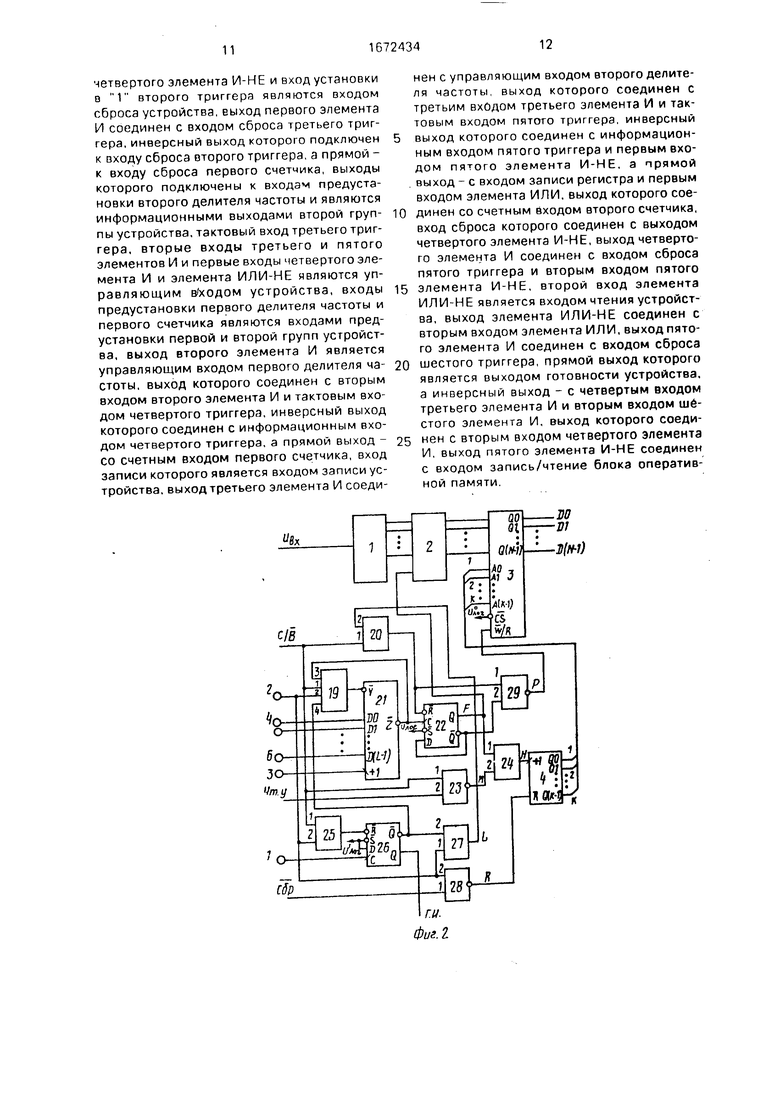

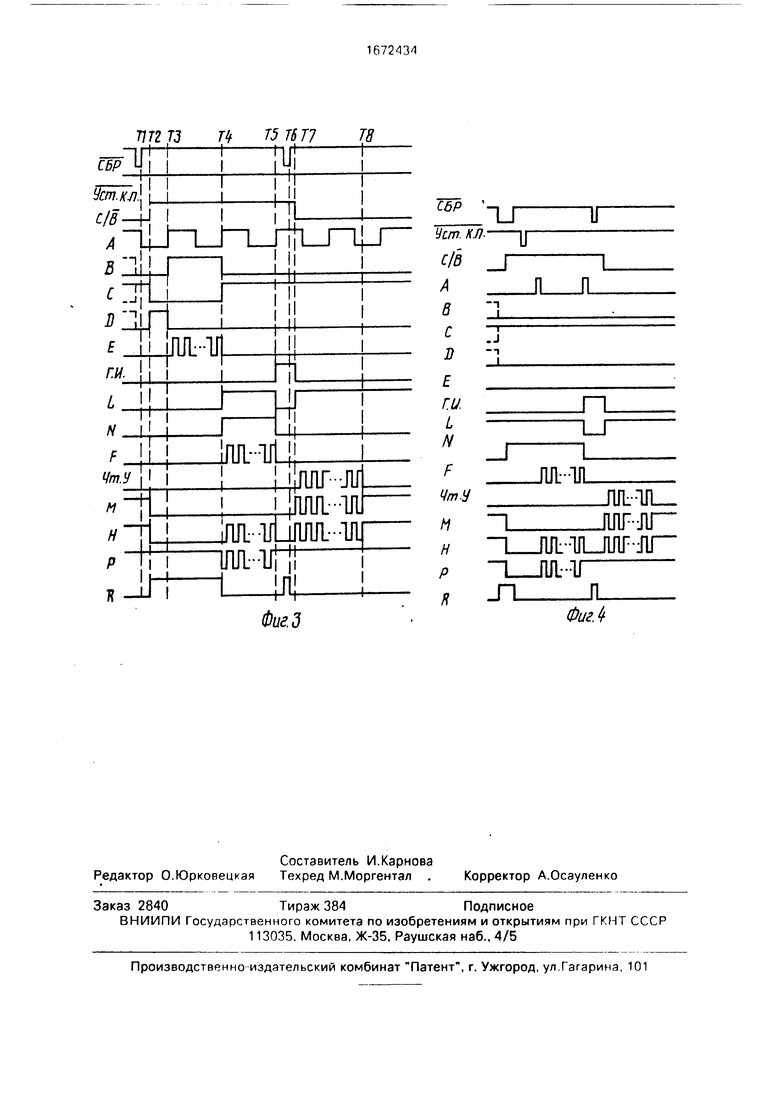

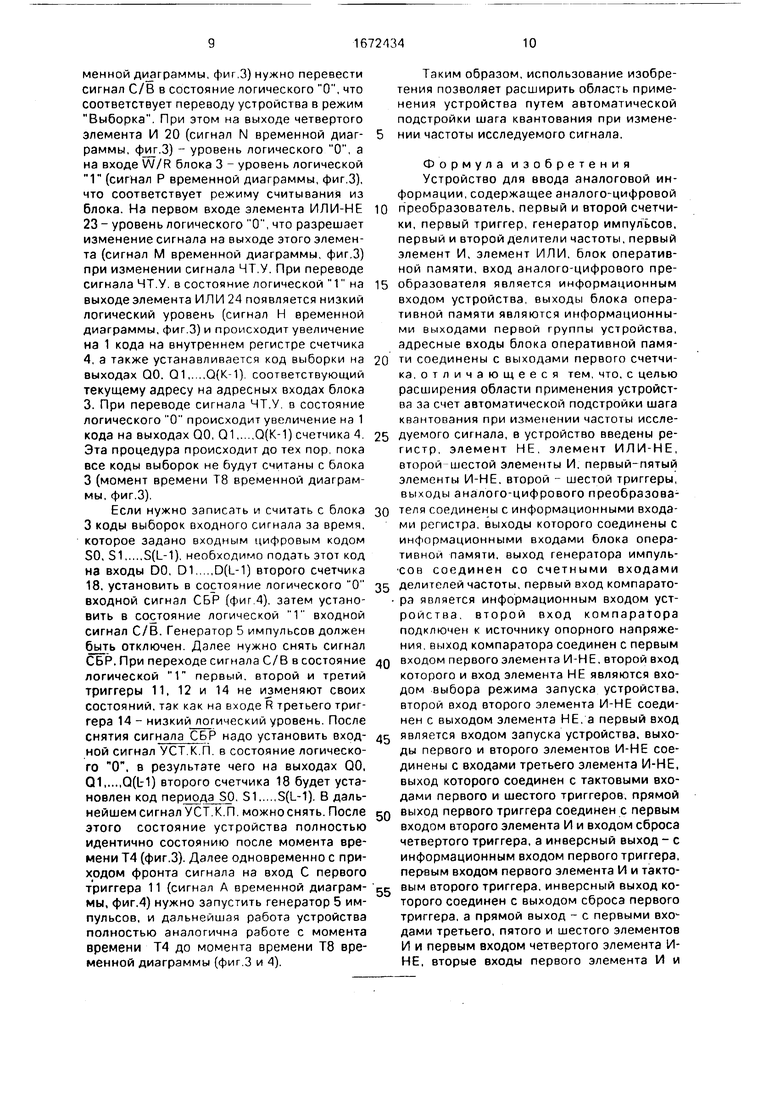

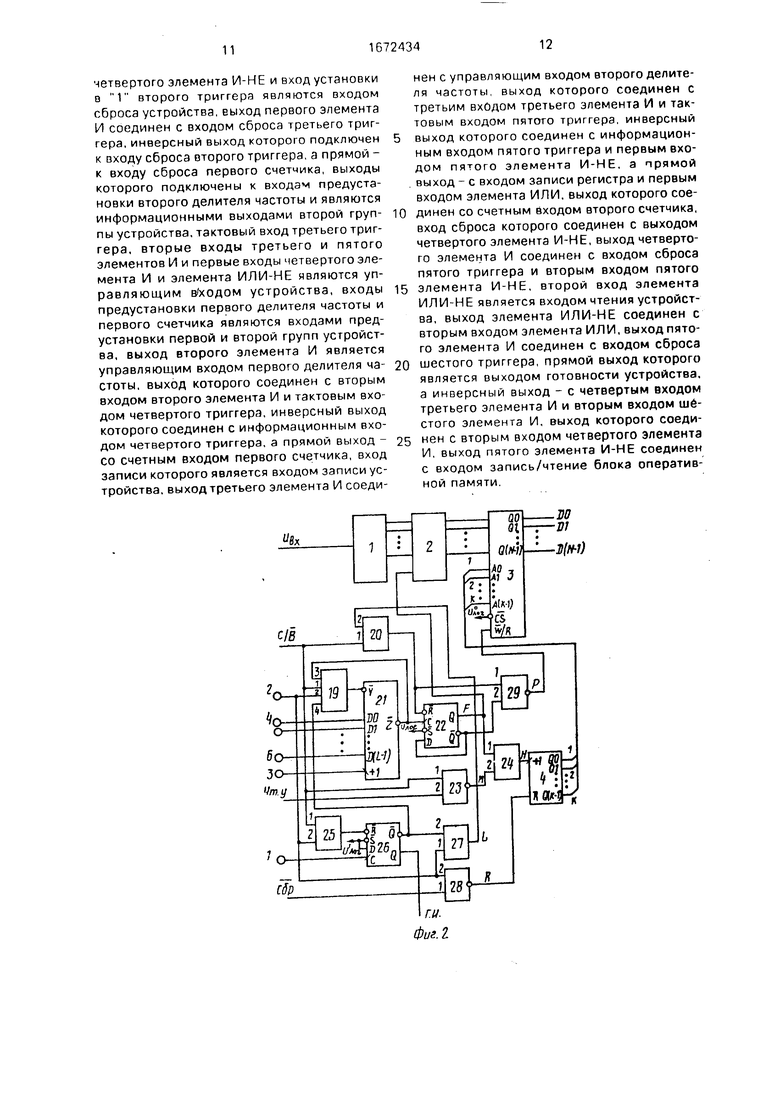

На фиг.1 и 2 представлена блок-схема устройства; на фиг.З и 4 - диаграммы, иллюстрирующие работу устройства.

Устройство для ввода аналоговой ин- формации (фиг.1 и 2) состоит из аналого- цифрового преобразователя (АЦП) 1, регистра 2, блока 3 оперативной памяти, первого счетчика 4, генератора 5 импульсов, компаратора 6, элемента НЕ 7. первого, вто5

10

15

20

25

30

35

40

45 50

55рого и третьего элементов И-НЕ 8-10, первого и второго триггеров 11 и 12, первого элемента И 13. третьего триггера 14, второго элемента И 15, первого делителя 16 частоты. четвертого триггера 17. второго счетчика 18. третьего элемента И 19, четвертого элемента И 20, второго делителя 21 частоты, пятого тригера 22, элемента ИЛИ-НЕ 23, элемента ИЛИ 24, пятого элемента И 25, шестого триггера 26, шестого элемента И 27, четвертого 28 и пятого 29 элементов И-НЕ.

Входными сигналами устройства являются входной аналоговый сигнал UBX и пороговое напряжение Unop; логические сигналы, сигнал сброса СБР, сигнал запуска ЗАГ сигнал вида запуска В.З., управляющийся сигнал установки режима С/В (снятие/вьГборка), сигнал чтения устройства ЧТ.У., сигнал установки кода периода УСТ.К.П., сигналы кода числа кодов выборок

входного аналогового сигнала СО, С1С(К-1),

сигналы кода периода SO, S1S(L-1).

Выходными сигналами устройства являются сигналы кодов выборок входного аналогового сигнала DO, D1D(N-1), выходные

сигналы кода периода входного аналогового сигнала РО Р1P(L-1), сигнал Готовность информации (Г.И,).

Устройство работает следующим образом.

На информационные входы DO, D1D(K-1) первого делителя 16 частоты подается код числа кодов выборок налогового сигнала. Подается сигнал СВР. При подаче этого сигнала появляется логический О на выходе первого элемента И 13. в результате устанавливается логическая 1 на выходе Q третьего триггера 14. На входе S второго триггера. 12 - уровень логического О. В результате на выходе Q этого триггера - логическая 1 (сигнал С временной диаграммы, фиг.З), а на выходе Q - уровень догического О, который поступает на вход R первого триггера 11, устанавливая на его выходе Q уровень логического О (сигнал В временной диаграммы, фиг.2). Поэтому на выходе второго элемента И 15, а следовательно, на входе предустановки V первого делителя 16 частоты, а также на входе R четвертого триггера 17 - состояние логического О, вследствие чего запрещена работа этих элементов. После перевода сигнала СБР в состояние логической 1 (момент времени Т1) разрешается работа второго и третьего триггеров 12 и 14.

Для перевода устройства в режим записи выборок входного сигнала (режим Снятие) сигналом С/В устанавливается логическая 1 (момент времени Т2). В результате этого положительным фронтом

сигнала С/В на входе С третьего триггера 14 при уровне логической 1 на его входе D на его выходе Q появляется сигнал логического О, а на выходе Q - логической 1, вследствие чего на выходе Q второго триггера 12 устанавливается уровень логического О, а на выходе Q - логической 1. разрешая тем самым работу первого триггера 11. Так как сигнал логического О присутствует на втором входе элемента И 19 (сигнал С временной диаграммы, фиг.З), первом входе шестого элемента И 27. втором входе пятого элемента И 25, а следовательно, и на входах R шестого триггера 26, на втором входе четвертого элемента И 20 и на его выходе, а также на входе V (предустановки) второго делителя 21 частоты, то запрещена работа делителя 21 частоты, пятого и шестого триггеров 22 и 26. Уровень логического О на втором входе четвертого элемента И-НЕ 28 устанавливает состояние логической 1 на его выходе и запрещает тем самым работу счетчика 4,

С появлением сигнала логической на выходе Q третьего триггера 14 (сигнал D временной диаграммы. фиг.З) устанавливается уровень логического О на выходах QO, Q1Q(L-1) второго счетчика 18.

В зависимости от уровня входного сигнала В.З. устройство может работать в двух режимах. Если сигнал В.З. имеет уровень логического О на втором входе первого элемента И-НЕ 8 - сигнал логического О, а на его выходе - сигнал логической 1. На входе 2 второго элемента И-НЕ 9 - уровень логической 1. и устройство работает от внешнего логического сигнала ЗАП, который поступает на первый вход второго элемента И-НЕ 9, инвертируясь, приходит на второй вход третьего элемента И-НЕ 10 и. еще раз проинвертировавшись. проходит на вход С первого триггера 11 (сигнал А временной диаграммы). Сигнал ЗАП формируется внешней схемой запуска. Если сигнал В.З. имеет уровень логической 1, то на входе2 второго элемента И-НЕ 10 -уровень логического О, а на входе третьего элемента И-НЕ 10 - уровень логической 1 и тем самым запрещено прохождение сигнала ЗАП и разрешено прохождение на вход С первого триггера 11 сигнала с выхода компаратора 6.

При переходе сигнала UBx через уровень Unop (временная диаграмма фиг.З, момент времени ТЗ) на выходе компаратора 6 появляется положительный фронт логического сигнала и. дважды проинвертировавшись, проходит на вход С первого триггера 11 (сигнал А временной диаграммы, фиг.З), устанавливая в состояние логической 1

его выход Q. В результате этого появляется уровень логической 1 на входе первого делителя 16 частоты и входе R четвертого триггера 17, разрешая их работу. Одновременно устанавливается уровень логического О на выходе Q первого триггера 11 и, следовательно, на первом входе и на выходе первого элемента И 13, в результате чего на выходе Q третьего триггера 14 (сигнал D

0 временной диаграммы. фиг.З) устанавливается уровень логического О, разрешая ра- боту второго счетчика 18. Входной сигнал УСТ.К.П. имеет высокий логический уровень, и запись входного кода SO. S1, S2,...S(L-1)

5 во второй счетчик 18 не происходит. На входе R второго триггера 12 появляется сигнал логической 1, разрешая работу этого триггера.

Когда на счетный вход первого делителя 16 частоты поступит К импульсов с выхода генератора 5 импульсов, на его выходе появляется уровень логического О, который, поступив на второй вход второго элемента И 15. проходит на вход V первого делителя 16 частоты, в результате чего во внутренний регистр последнего запишется код СО,

С1С(К-1)(код числа кодов выборок), после

чего сигнал на выходе Z возвращается в состояние логической инвертирует сигнал на выходе Q четвертого триггера 17. так как на вход D этого тригера подан сигнал с выхода О. Каждый фронт сигнала с выхода О четвертого триггера 17 (сигнал Е временной диаграммы, фиг.З) инкрементирует выходной код QO, 01, ...Q(L-1) второго счетчика 18.

К момент второго перехода входного аналогового сигнала через уровень Unop, соответствующий окончанию периода входного сигнала или приходу второго импульса запуска (момент времени Т4 временной диаграммы, фиг.З). на входе С первого триггера 11 формируется фронт сигнала, который устанавливает на выходе Q этого триггера

5 (сигнал В временной диаграммы, фиг.3)уро- вень логического О, так как на входе D первого триггера 11 до этого момента был уровень логического 1 0. Появление логического О на входе у первого делителя 16 частоты и на входе R четвертого триггера 17 запрещает работу этих элементов. Одновременно появление фронта сигнала на выходе Q первого триггера 11 устанавливает на выходе Q второго триггера 12 высокий логический уровень (сигнал С временной диаграммы, фиг.З), тем самым устанавливая на выходах элементов И 19 20. 25 и 27 высохни логический уровень и, следовательно, разрешая работу второго делителя 21 частоты, пятого и шестого триггеров 22 и

0

5

0

5

0

0

5

26 и счетчика 4 (на четвертом входе элемента И 19 - уровень логической 1 так как шестой триггер 26 установлен в состояние логического О). Также в этот момент установившийся на выходе Q второго триггера 12 уровень логического О запрещает изменение уровней сигналов на выходах первого триггера 11.

К моменту времени Т4 (временная диаг-

рамма, фиг.З) на выходах QO, Q1Q(L-1)

второго счетчика 18 и, соответственно, на

входах DO, D1D(L-1) делителя 21 частоты,

являющихся также выходами РО. Р1P(L-1)

устройства, фиксируется код, численное значение которого пропорционально периоду входного аналогового сигнала:

I -

2 Тд К То

где ТА - период входного аналогового сигнала:

Т0 - период сигнала тактового генератора;

К- код на входах СО, С1С(К-1)устройства.

Делитель 21 частоты и пятый триггер 22 работают аналогично элементам 16 и 17. Когда на счетный вход делителя 21 частоты поступит L импульсов с выхода генератора Б.импульсов, на выходе этого делителя частоты появляется уровень логического О и, поступив на вход элемента И 19, проходит на вход V делителя 21 частоты, в результате чего в регистр этого делителя вновь запишется код, установленный на выходах

QO.Q1Q(L-1) второго счетчика 18. После

этого сигнал на выходе Z делителя 21 частоты вновь принимает уровень логической 1, и фронт этого сигнала инвертирует сигнал на выходах Q и Q пятого триггера 22, так как его выход Q соединен с входом D. По фронту сигнала на выходе Q пятого триггера 22 (сигнал F временной диаграммы, фиг.З) проис- ходит запись кода с выхода АЦП 1 в регистр 2, Сигнал на выходе элемента ИЛИ-НЕ 23 имеет низкий логический уровень (сигнал М временной диаграммы, фиг.З), так как на его первом входе - уровень логической 1 (сиг- нал С/В), поэтому уровень логической 1 появляется на выходе элемента ИЛИ (сигнал Н временной диаграммы, фиг.З) тогда, когда F имеет высокий логический уровень. Запись происходит в блок 3 тогда, когда сигнал на выходе элемента И-НЕ 29 принимает уровень логического О (сигнал Р временной диаграммы, фиг.З). Это происходит тогда, когда на выходе Q пятого триггера 22 появляется уровень логической 1.

5

Ю

15

20

25

30 35

Счетчик 4 работает следующим образом. Перепад 1 - О на входе +1 прямого счета инкрементирует код на его внутренних регистрах, а следующий за ним перепад О заносит этот код в выходной регистр (выходы счетчика QO. Q1Q(K-1). Таким образом, соблюдается следующая последовательность (в ременная диаграмма, фиг.30 сигналы F, Н, Р): запись в регистр 2, запись в блок 3, смена адреса.

В момент времени Т5 (фиг.З) происходит переход входного напряжения UBx через пороговый уровень (или проходит очередной импульс сигнала ЗАП). и на выходе третьего элемента И-НЕ 10 формируется фронт сигнала, который устанавливает на выходе Q шестого триггера 26 низкий логический уровень. Вследствие этого уровень логического О, появляется на входе элемента И 19, на выходе шестого элемента И 27 (сигнал L временной диаграммы, фиг.З) и, соответственно, на втором входе четвертого элементами 20 и на его выходе. В результате на входе V второго делителя 21 частоты и на входе R пятого триггера 22 устанавливается уровень логического О, запрещая их дальнейшую работу и устанавливая на первом входе элемента ИЛИ 24 уровень логического О.

К этому моменту число кодов выборок, записанных в блок 3, равно:

К

ТА ToL

(5)

где L - код на выходах QO, Q1Q(L-1) второго счетчика 18.

На выходе Q шестого триггера 26 устанавливается уровень логической 1. что является выходным сигналом, свидетельствующим об окончании процесса записи в блок оперативной памяти кодов выборок (сигнал Г.И. временной диаграммы, фиг.З). Одновременно появляется уровень логического О на первом входе пятого элемента И-НЕ 29 (сигнал N временной диаграммы, фиг.З), устанавливая уровень логической Г на входе W/R блока 3, что соответствует режиму чтения.

Для осуществления считывания из блока 3 кодов выборок аналогового сигнала необходимо подать сигнал СВР. который, поступив на первый вход четвертого элемента И-НЕ 28, устанавливает на его выходе состояние логической 1, в результате чего выходы QO, Q1Q(K-1) счетчика 4 принимают состояние логического О.

После перевода сигнала СВР в состояние логической 1 (момент времени Т6 временной диаграммы, фиг.З) нужно перевести сигнал С/В в состояние логического О, что соответствует переводу устройства в режим Выборка. При этом на выходе четвертого элемента И 20 (сигнал N временной диаграммы, фиг.З) - уровень логического О, а на входе W/R блока 3 - уровень логической 1 (сигнал Р временной диаграммы, фиг.З), что соответствует режиму считывания из блока. На первом входе элемента ИЛИ-НЕ 23 - уровень логического О, что разрешает изменение сигнала на выходе этого элемента (сигнал М временной диаграммы, фиг.З) при изменении сигнала ЧТ.У. При переводе сигнала ЧТ.У. в состояние логической 1 на выходе элемента ИЛИ 24 появляется низкий логический уровень (сигнал Н временной диаграммы, фиг.З) и происходит увеличение на 1 кода на внутреннем регистре счетчика 4, а также устанавливается код выборки на выходах QO. Q1,. .,Q(K-1) соответствующий текущему адресу на адресных входах блока 3. При переводе сигнала ЧТ.У. в состояние логического О происходит увеличение на 1

кода на выходах QO, Q1Q(K-1) счетчика 4.

Эта процедура происходит до тех пор, пока все коды выборок не будут считаны с блока 3 (момент времени Т8 временной диаграммы, фиг.З).

Если нужно записать и считать с блока 3 коды выборок входного сигнала за время, которое задано входным цифровым кодом

SO, S1S(L-1). необходимо подать этот код

на входы DO, D1D(L-1) второго счетчика

18, установить в состояние логического О входной сигнал СВР (фиг 4). затем установить в состояние логической 1 входной сигнал С/В. Генератор 5 импульсов должен быть отключен. Далее нужно снять сигнал СВР. При переходе сигнала С/В в состояние логической 1 первый, второй и третий триггеры 11, 12 и 14 не изменяют своих состояний, так как на входе R третьего триггера 14 - низкий логический уровень. После снятия сигнала СБР надо установить входной сигнал УСТ.К.П. в состояние логического О, в результате чего на выходах QO, Q1О(Ы) второго счетчика 18 будет установлен код , S1S(L-1). В дальнейшем сигнал УСТ.К.П. можноснять. После этого состояние устройства полностью идентично состоянию после момента времени Т4 (фиг.З). Далее одновременно с приходом фронта сигнала на вход С первого триггера 11 (сигнал А временной диаграммы, фиг.4) нужно запустить генератор 5 импульсов, и дальнейшая работа устройства полностью аналогична работе с момента времени Т4 до момента времени Т8 временной диаграммы (фиг.З и 4).

Таким образом, использование изобретения позволяет расширить область применения устройства путем автоматической подстройки шага квантования при измене- нии частоты исследуемого сигнала.

Формула изобретения Устройство для ввода аналоговой информации, содержащее аналого-цифровой

преобразователь, первый и второй счетчики, первый триггер, генератор импульсов, первый и второй делители частоты, первый элемент И, элемент ИЛИ. блок оперативной памяти, вход аналого-цифрового преобразователя является информационным входом устройства, выходы блока оперативной памяти являются информационными выходами первой группы устройства, адресные входы блока оперативной памяти соединены с выходами первого счетчика, отличающееся тем, что. с целью расширения области применения устройства за счет автоматической подстройки шага квантования при изменении частоты исследуемого сигнала, в устройство введены регистр, элемент НЕ, элемент ИЛИ-НЕ, второй шестой элементы И. первый-пятый элементы И-НЕ. второй - шестой триггеры, выходы аналого-цифрового преобразователя соединены с информационными входами регистра, выходы которого соединены с информационными входами блока оперативной памяти, выход генератора импуль- сов соединен со счетными входами

делителей частоты, первый вход компарато- ра является информационным входом устройства, второй вход компаратора подключен к источнику опорного напряжения, выход компаратора соединен с первым

входом первого элемента И-НЕ, второй вход которого и вход элемента НЕ являются входом выбора режима запуска устройства. второй вход второго элемента И-НЕ соединен с выходом элемента НЕ, а первый вход

является входом запуска устройства, выходы первого и второго элементов И-НЕ соединены с входами третьего элемента И-НЕ, выход которого соединен с тактовыми входами первого и шестого триггеров, прямой

выход первого триггера соединен с первым входом второго элемента И и входом сброса четвертого триггера, а инверсный выход - с информационным входом первого триггера, первым входом первого элемента И и тактовым второго триггера, инверсный выход которого соединен с выходом сброса первого триггера, а прямой выход - с первыми вхо дами третьего, пятого и шестого элементов И и первым входом четвертого элемента И- НЕ, вторые входы первого элемента И и

четвертого элемента И-НЕ и вход установки в 1 второго триггера являются входом сброса устройства, выход первого элемента И соединен с входом сброса третьего триггера, инверсный выход которого подключен к входу сброса второго триггера а прямой - к входу сброса первого счетчика, выходы которого подключены к входам предустановки второго делителя частоты и являются информационными выходами второй группы устройства, тактовый вход третьего триггера, вторые входы третьего и пятого элементов И и первые входы четвертого элемента И и элемента ИЛИ-НЕ являются управляющим входом устройства, входы предустановки первого делителя частоты и первого счетчика являются входами предустановки первой и второй групп устройства, выход второго элемента И является управляющим входом первого делителя ча стоты, выход которого соединен с вторым входом второго элемента И и тактовым входом четвертого триггера, инверсный выход которого соединен с информационным входом четвертого триггера, а прямой выход - со счетным входом первого счетчика, вход записи которого является входом записи устройства, выход третьего элемента И соедиi-

нен с управляющим входом второго делителя частоты выход которого соединен с третьим входом третьего элемента И и тактовым входом пятого триггера, инверсный

5 выход которого соединен с информационным входом пятого триггера и первым входом пятого элемента И-НЕ, а прямой выход - с входом записи регистра и первым входом элемента ИЛИ, выход которого сое10 динен со счетным входом второго счетчика, вход сброса которого соединен с выходом четвертого элемента И-НЕ, выход четвертого элемента И соединен с входом сброса пятого триггера и вторым входом пятого

15 элемента И-НЕ, второй вход элемента ИЛИ-НЕ является входом чтения устройства, выход элемента ИЛИ-НЕ соединен с вторым входом элемента ИЛИ, выход пятого элемента И соединен с входом сброса 20 шестого триггера, прямой выход которого является выходом готовности устройства, а инверсный выход - с четвертым входом третьего элемента И и вторым входом шестого элемента И, выход которого соеди25 пен с вторым входом четвертого элемента И, выход пятого элемента И-НЕ соединен с входом запись/чтение блока оперативной памяти

Фи&З

Фиг Л

| Устройство для ввода аналоговой информации | 1987 |

|

SU1425645A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для ввода аналоговой информации | 1986 |

|

SU1425644A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-08-23—Публикация

1989-09-18—Подача