Изобретение относится к вычислительной технике и может быть использовано при построении быстродействую- щих процессоров цифровой обработки сигналов и арифметических устройств быстродействующих цифровых к комбинированных вычислительных машин.

Целью изобретения является сокращение аппаратурных; затрат и повышение быстродействия.

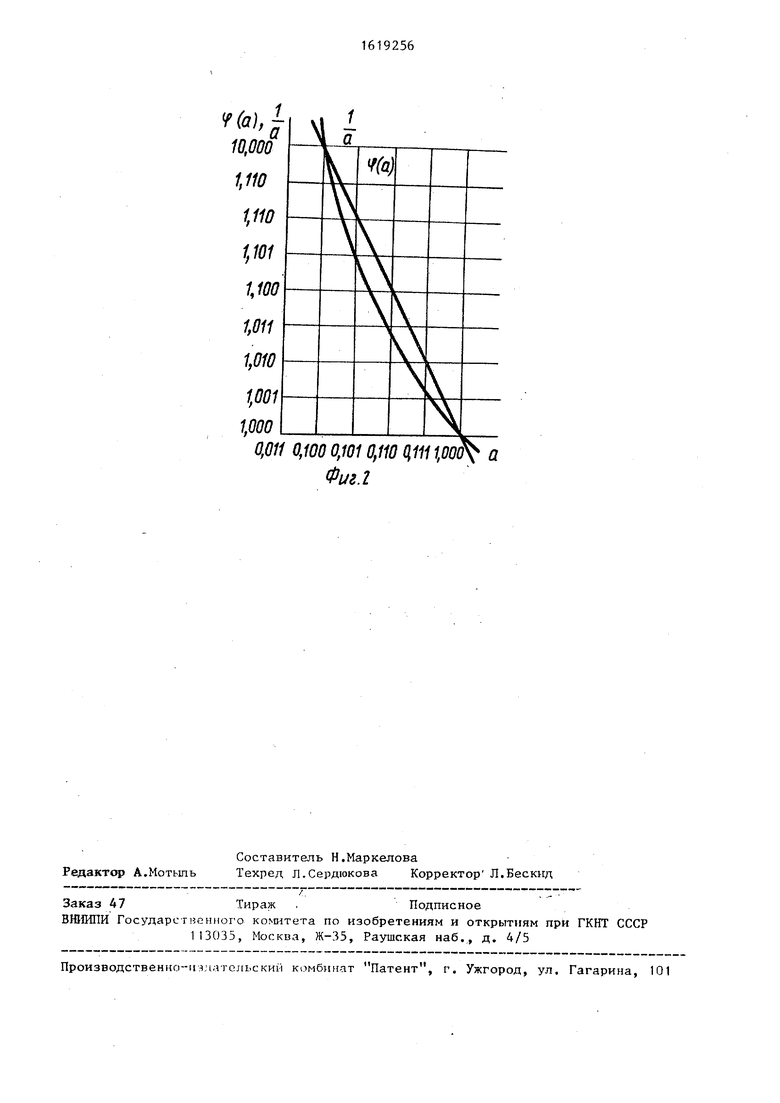

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - график функции ср(а) .

Устройство для деления содержит регистр 1, матричнме умножители 2 - 4 сумматоры 5,6, группы 7,8 элементов НЕ, входы 9,10 делимого и делителя устройства и выходы 11 устройства, а также вход 12 синхронизации уст- ройства, генератор 13 импульсов, вход 4 логической единицы устройства вход 15 логического нуля устройства.

В качестве матричных умножителей 2, 3 могут быть применены микросхемы

КР 1802BP3 или КР 1802ВР4. В качестве третьего матричного умножителя 4 также можно применить ту же микросхему, однако в этом случае на вход его синхронизации необходимо подавать сиг налы от внешнего или внутреннего генератора 13, частота которого определяется временем завершения операций умножения в умножителе 4 и суммирования в сумматоре 6. Для достижения же наивысшего быстродействия для данного устройства целесообразно применение в качестве умножителя 4 асинхронного модуля.

В качестве сумматоров 5,6 могут быть применены сумматоры комбинацион- ного типа, например микросхемы серии 155 ИМЗ,

В устройстве реализуется интеради- очный процесс, соответствующий урав- нению

х(К b(a)(a)-l,xk ,

где а - делитель; b - делимое;

ЦСа)1.

Устройство работает следующим образом.

Двоичные коды делимого b и делите- ля а в нормализованной форме подаются соответственно на входы 9 и 10 устройства, а код делителя запоминается в регистре 1. Сигналы кода де

$

„

5

0

лителя а с выходов регистра 1 поступают на входы первого сомножителя умножителя 2, а сигналы младших (п-1) разрядов его поступают еще и на входы элементов НЕ группы 7. Сигнал старшего разряда кода делителя поступает на вход старшего разряда первого слагаемого сумматора 5. На входы (п-1) младших разрядов первого слагаемого сумматора 5 поступают сигналы с выходов элементов НЕ группы 7. С учетом того, что входы второго слагаемого сумматора 5 соединены с шиной логического нуля устройства, а вход переноса сумматора 5 соединен с шиной логической единицы, на выходе сумматора 5 установится код приближенного значения обратной величины Ср(а)3-2а 1/а (фиг. 2), который поступает на входы одного из сомножителей умножителей 2 и 3.

Через время, достаточное для прохождения сигналов с входа 10 до выходов сумматора 5, подается стартовый синхроимпульс на вход 12 устройства. Вследствие этого коды, поступившие на входы, будут умноженыв умножителях 2,3, а на их выходах образуются коды произведений а-Ц(а) и Ь-(Л(а) соответственно, которые сохраняют свое значение до прихода следующего сигнала на вход 12.

С выходов (п-1) младших разрядов из п старших (без сигнала старшего разряда, равного единице, так как для нормализованных чисел а(р(а)ь1) умножителя 2 на входы первого сомножителя умножителя 4 поступают сигналы кода a-0f(a)-lj.

Сигналы кода b-cf(a) с выхода умножителя 3 поступают на входы первого слагаемого сумматора 6, на входы второго слагаемого которого поступают сигналы дополнительного кода от результата умножения в умножителе 4. Дополнительный код образуется путем инверсии сигналов умножителя 4 в элементах НЕ группы 8 и поступления инверсионных сигналов на входы (п-1) младших разрядов второго слагаемого сумматора, а также соединением входа переноса и входа старшего разряда второго слагаемого сумматора 6 с шиной логической единицы.

В исходном состоянии устройства на его выходах 11 устанавливаемся нулевой код 0,00,..0.

После поступления кодов ) на входы первого слагаемого сумма ора 6

и с учетом того, что на входах его второго слагаемого еще сохранился нулевой код, так как a- ty(a)-fj. x 0,00...О, на выходах сумматора 6 образуется код первого приближения частного хсл b-y(a)-fa Cj)(a)-l. хга) b-tp(a).

Сигналы кода х с выходов сумматора поступают на входы второго сомно- жителя умножителя 4, вследствие чего на выходе умножителя 4 образуется код произведения a-tp (a)-lj- x (1 , который в дополнительной форме поступает на входы второго слагаемого для очередного вычитания Ъ -(| (а)Ја s(a)-fi- x ft . На выходе сумматора 6 образуется код очередного (второго) приближения частного

X

{г

Ъ.(а)(а)- Очх

«1

Процесс изменения кодов в блоках 4 6,8 будет интерационно повторяться до тех пор, пока устройство не придет в устойчивое состояние при х x ki когда исчезнет причина продолжения интерационного процесса. Если х1 х(, из интерационного уравнения получают (J(a) (а) х, откуда следует . Таким образом, после прекращения (завершения) чнтера ционного процесса в блоках 4,6,8 на выходах 11 устройства установится значение кода частного , вычисленное в точностью младшего разряда.

Если умножитель 4 синхронизируемый то его вход синхронизации должен быть соединен с выходом внешнего или внутреннего генератора импульсов, период которых должен быть нескрлько больше общего времени умножителя, суммирования и задержки в блоках 4,6, 8 соответственно.

Формула изобретения

Устройство для деления, содержащее три матричных умножителя, два сумматора и регистр, входы которого соеди$

0

5

0

5

0

5

нены с входами делителя устройства, выходы регистра соединены с входами первого сомножителя первого матричного умножителя, входы второго сомножителя которого соединены с выходами первого сумматора и с входами первого сомножителя второго матричного умножителя, выходы которого соединены с входами первого слагаемого второго сумматора, выходы которого соединены с выходами устройства и с входами первого сомножителя третьего матричного умножителя, отличающееся тем, что, с целью сокращения аппаратурных затрат и повышения быстродействия, устройство содержит две группы элементов НЕ и генератор импульсов, выход которого соединен с синхровходом третьего матричного умножителя, входы вчорого сомножителя которого соединены с выходами п-1 младших разрядов первого матричного умнокктеля, вход синхронизации которого соьдинен с входами синхронизации устройства и второго матричного умножителя, входы второго сомножителя которого соединены с входами делимого устройства, выходы п-1, где п - разрядность операндов, младших разрядов регистра соединены с входами элементов НЕ первой группы, выходы которых соединены с входами п-1 младших разрядов первого слагаемого первого сумматора, вход старшего разряда первого слагаемого которого соединен с выходом старшего разряда регистра, вход логической единицы устройства соединен с входами переноса и старшего разряда второго слагаемого второго сумматора и входом переноса первого сумматора, вход второго слагаемого которого соединен с входом логического нуля устройства, выходы третьего матричного умножителя соединены с входами элементов НЕ второй группы, выходы которых соединены с входами п-1 младших разрядов второго слагаемого второго сумматора.

Vto,l

10,000

0,0110,100 0,1010,110 (1111 /,шу а

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1988 |

|

SU1517026A1 |

| Устройство для деления | 1985 |

|

SU1317432A1 |

| Интерполятор функций двух аргументов | 1984 |

|

SU1247893A1 |

| Цифровое множительно-делительное устройство | 1990 |

|

SU1730623A1 |

| Устройство для умножения | 1986 |

|

SU1399729A1 |

| Устройство для вычисления функций | 1985 |

|

SU1280391A1 |

| Устройство для деления | 1989 |

|

SU1619255A1 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| Устройство для деления | 1987 |

|

SU1441389A1 |

| Устройство для деления | 1986 |

|

SU1354186A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих процессоров цифровой обработки сигналов и арифметических устройств быстродействующих цифровых и комбинированных вычиспительных машин. В устройстве деление двоичных нормализованных чисел осуществляется путем аппаратурной реализации итерационного алгоритма. Целью изобретения является сокращение аппаратурных затрат и повышение быстродействия для устройств итерационного типа. Для достижения цели в устройство, содержащее три матричных умножителя 2-4, два сумматора 5,6 и регистр 1, дополнительно введены две группы элементов НЕ /,8 и генератор 13 импульсов, связи между блоками организованы таким образом, что при обеспечении высокого быстродействия прототипа возможно сокращение аппаратурных затрат на 15% по сравнению с прототипом. 7. ил. Ј

| Авторское свидетельство СССР по заявке 4400180/24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления | 1986 |

|

SU1354186A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-01-07—Публикация

1989-03-20—Подача