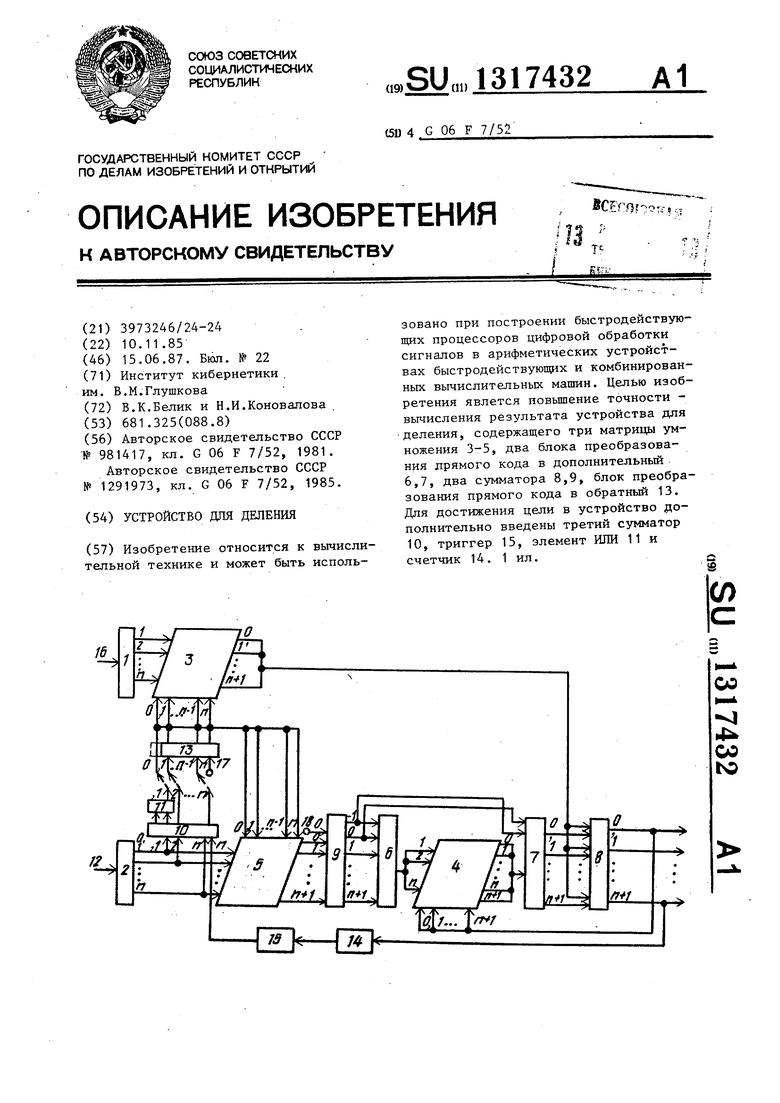

Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих процессоров цифровой обработки сигналов и в арифметических устройст- вах быстродействующих цифровых и комбинированных вычислительных машин.

Целью изобретения является повышение точности вычисления результата устройства для деления.

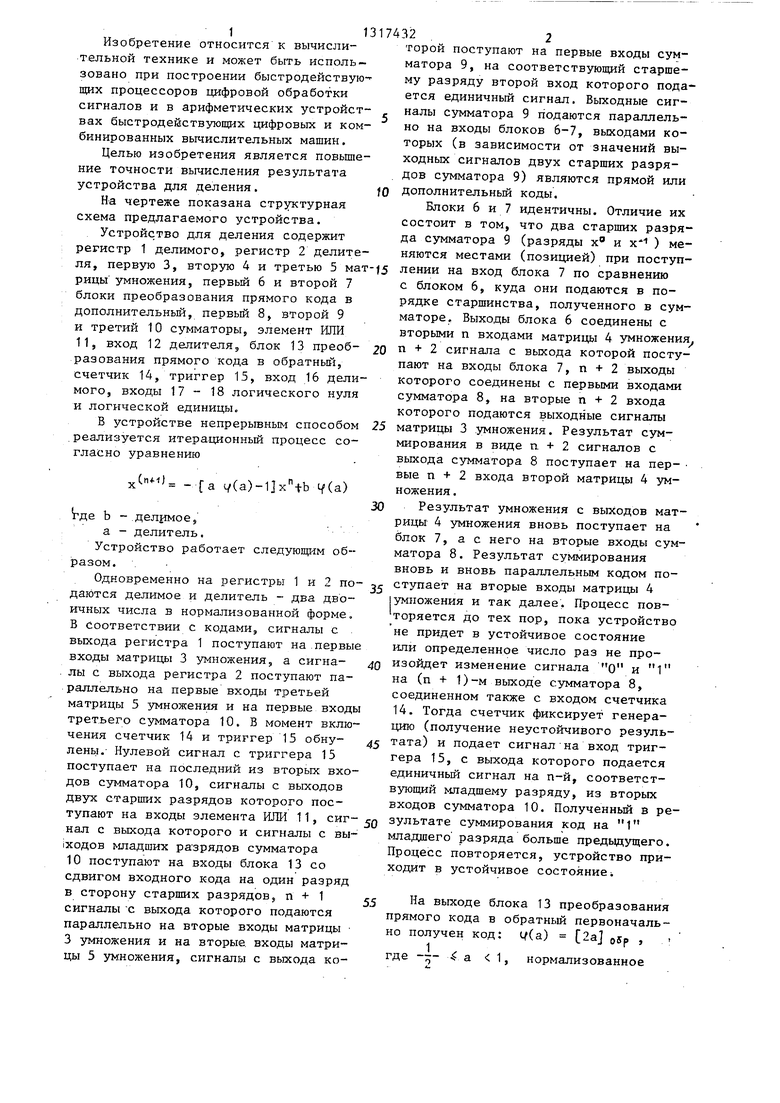

На чертеже показана структурная схема предлагаемого устройства.

Устройство для деления содержит регистр 1 делимого, регистр 2 делителя, первую 3, вторую 4 и третью 5 мат рицы умножения, первьй 6 и второй 7 блоки преобразования прямого кода в дополнительньй, первый 8, второй 9 и третий 10 сумматоры, элемент ИЛИ 11, вход 12 делителя, блок 13 преоб- разования прямого кода в обратный, счетчик 14, триггер 15, вход 16 делимого, входы 17 - 18 логического нуля и логической единицы.

В устройстве непрерьюным способом ,реализуется итерационный процесс согласно уравнению

- а v(a) tf(a)

где b -.делимое, а - делитель,

Устройство работает следующим образом.

Одновременно на регистры 1 и 2 по- даются делимое и делитель - два двоичных числа в нормализованной форме. В Соответствии с кодами, сигналы с выхода регистра 1 поступают на первые входы матрицы 3 умножения, а сигна- лы с выхода регистра 2 поступают параллельно на первые входы третьей матрицы 5 умножения и на первые входы третьего сумматора 10. В момент включения счетчик 14 и триггер 15 обну- лены.- Нулевой сигнал с триггера 15 поступает на последний из вторых входов сумматора 10, сигналы с выходов двух старших разрядов которого поступают на входы элемента ИЛИ 11, сиг- нал с выхода которого и сигналы с вы- 1-коцов младших разрядов сумматора 10 поступают на входы блока 13 со сдвигом входного кода на один разряд в сторону старших разрядов, п + 1 сигналы С выхода которого подаются параллельно на вторые входы матрицы 3 умножения и на вторые, входы матрицы 5 умножения, сигналы с выхода ко

5 0

5

0

0 Q

торой поступают на первые входы сумматора 9, на соответствующий старшему разряду второй вход которого подается единичный сигнал. Выходные сигналы сумматора 9 подаются параллельно на входы блоков 6-7, выходами которых (в зависимости от значений выходных сигналов двух старших разрядов сумматора 9) являются прямой или дополнительный коды.

Блоки 6 и 7 идентичны. Отличие их состоит в том, что два старших разряда сумматора 9 (разряды х и х ) меняются местами (позицией) при поступлении на вход блока 7 по сравнению с блоком 6, куда они подаются в порядке старшинства, полученного в сумматоре. Выходы блока 6 соединены с вторыми п входами матрицы 4 умножения п + 2 сигнала с выхода которой поступают на входы блока 7, п + 2 выходы которого соединены с первыми входами сумматора 8, на вторые п + 2 входа которого подаются выходные сигналы матрицы 3 умножения. Результат суммирования в виде п. + 2 сигналов с выхода сумматора 8 поступает на пер- вые п + 2 входа второй матрицы 4 умножения .

Результат умножения с выходов матрицы 4 умножения вновь поступает на блок 7, а с него на вторые входы сумматора 8. Результат суммирования вновь и вновь параллельным кодом поступает на вторые входы матрицы 4 Iумножения и так далее. Процесс повторяется до тех пор, пока устройство не придет в устойчивое состояние или определенное число раз не произойдет изменение сигнала О и 1 на (п + 1)-м выходе сумматора 8, соединенном также с входом счетчика 14. Тогда счетчик фиксирует генерацию (получение неустойчивого результата) и подает сигнал на вход триггера 15, с выхода которого подается единичный сигнал на п-й, соответствующий младшему разряду, из вторых входов сумматора 10. Полученный в результате суммирования код на 1 мла,пдпего разряда больше предыдущего. Процесс повторяется, устройство приходит в устойчивое состояние ,

На выходе блока 13 преобразования прямого кода в обратный первоначально получен код: t/(a) 2aJ oSp ,

1

где --- а 1, нормализованное

31317432

представлено двоичным кодом в

л п с

виде а о

a,aj.

а. Тогда

if(a) а

1

.

.а„о

1,а

.а„1

f5

где а .1 - а.

Поступившие на первые п входы матрицы 5 умножения значения кода а пе- ,„ ремножаются на ней со значением if (а), поступившим на вторые п + 1 входы матрицы 5 умножения. Старшие п + 2 разряда кода произведения а-if (а) с вькода матрицы 5 умножения поступают на вход сумматора.9, где происходит сложение этого кода с единицей.

Если полученное на сумматоре 9 значение разницы а i/(a)-1 положительное, то значение двух старших из п + + 3 разрядов на выходе сумматора 9 будет равно 10, а если отрицательное, то 01. Эти два старших разряда в качестве стробирующих поступают на пер20

вые два входа блоков 6-7 преобразова-25 нескольких циклов генерации, число

ния прямого кода в дополнительный. На выходах блоков 6-7 получается тот же или дополнительный от входного кода код, в зависимости от значений . Двух старших разрядов сумматора 8. Так, если код 10, то на выходе блока 6 будет тот же код, что и на входе, а на выходе блока 7 - дополнительньш к входному код. Обратная ситуация наблюдается при коде 01.

На вьпсоде матрицы 4 умножения получается значение произведения прямого кода а- iXa) - 1 на код , которое в зависимости от значений двух старших разрядов 01 или 10 сумматора 9 поступает на вторые п + 2 входа сумматора 8 без изменения или с пре- ,образованием входного кода на допол- нительный.

Если a-LfCa)7 1 (например, а-Ч (а) 1,0.. . 1) , то а -i/Ca) - 1 - положительное число. В этом случае на выходе сумматора 9 получим a-tXa)-1 10,0...1, где значение двух стар30

35

40

45

которьЕх определяется разрядностью счетчика 14. В последнем случае сче чик 14 подает сигнал на триггер 15, с выхода которого единичный сигнал поступает на младший разряд из вторых входов третьего сумматора 10. В результате работы третьего сумматор 10, элемента ИЛИ 11 и блока 13 преобразования прямого кода в обратный получаем новое значение -f (a), на ед ницу младшего разряда меньше предыдущего 1(а) . 1

По истечении переходных процессо в устройстве на выходе сумматора 8 формируется результат, равный частному от деления.

Формула изобретени

Устройство для деления, содержащ три матрицы умножения, два сумматор два блока преобразования прямого ко да в дополнительньй, блок преобразования прямого кода в обратный регистры делимого и делителя, входы которых являются входами делимого и делителя устройства соответственно, выход регистра де лимого соединен с входом первог сомножителя первой матрицы умножения выход которой соединен с входом пер вого слагаемого первого сумматора, выход которого является выходом реJ--1

х° 10.

ших разрядов кода х

В случае, если а- i/(a) 1 (например, a.t/(a) 0,1...1), получим (а) - 1 - отрицательное число. На выходе сумматора 9 получим а-ч(а)- 1 01, 1...1, где значение двух старших разрядов кода х х° 01. Здесь учитьшается перенос в старший разряд х сумматоров 8 и 9 при сложении разрядов х.

На выходе матрицы 3 умножения получается значение произведения Ь- v(a), которое поступает на первые п + 2 входа первого сумматора 8. На сумматоре 8 получается сумма

м

(+1)

5

„

+ b -i/Ca) х выходах суммато0

(a) - и X Полученное на п + 2 ра 8 значение суммы в качестве х поступает на п + 2 вторых входа второй матрицы 4 умножения.

Таким образом, после подачи ко- дов делимого и делителя на соответствующие регистры происходит их предварительное преобразование и умножение на первой 3 и третьей 5 матрицах умножения, после чего возникает итерационный процесс, в котором участвуют матрица 4 умножения, блоки 6-7 преобразования прямого кода в догюл- нительный и сумматор 8.

Вследствие переходных процессов в устройстве на выходе сумматора 8 результат получается сразу или после

0

5

0

5

0

5

которьЕх определяется разрядностью счетчика 14. В последнем случае счетчик 14 подает сигнал на триггер 15, с выхода которого единичный сигнал поступает на младший разряд из вторых входов третьего сумматора 10. В результате работы третьего сумматора 10, элемента ИЛИ 11 и блока 13 преобразования прямого кода в обратный получаем новое значение -f (a), на единицу младшего разряда меньше предыдущего 1(а) . 1

По истечении переходных процессов в устройстве на выходе сумматора 8 формируется результат, равный частному от деления.

Формула изобретения

Устройство для деления, содержащее три матрицы умножения, два сумматора, два блока преобразования прямого кода в дополнительньй, блок преобразования прямого кода в обратный, регистры делимого и делителя, входы которых являются входами делимого и делителя устройства соответственно, выход регистра де- лимого соединен с входом первого сомножителя первой матрицы умножения, выход которой соединен с входом первого слагаемого первого сумматора, выход которого является выходом ре5.13

зультата устройства и соединен с входом первого сомножителя второй матри цы умножения, вход второго сомножителя которого соединен с вькодом первого блока преобразования прямого кода в дополнительньй, вход которого соединен с выходом второго сумматора, вход первого слагаемого которого соединен с выходом третьей : матрицы умножения, .вход первого сомножителя которой соединен с выходом регистра делителя, выход блока преобразования прямого кода в обратный со единён с входами вторых сомножителей, первой и третьей матриц умножения, вход п-го младшего разряда (где п - разрядность операндов) блока преобразования прямого кода в обратный соединен с входом логического нуля устройства, вход логической еди ницы устройства соединен с входом знакового разряда второго слагаемого второго сумматора, выходы старшего и младшего знаковых разрядов которого соед инены с входами младшего и старшего знаковых разрядов соответ ственно второго блока преобразования прямого кода в дополнительный, инСоставитель Н.Маркелова Редактор. А.Маковская Техред А.Кравчук Корректор М.Шароши

Заказ 2424/43 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по дедам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

174326

формационный вход которого соединен с выходом второй матрицы умножения выход второго блока преобразования прямого кода в дополнительный соеди- J нен с входом второго слагаемого первого сумматора, отличающее- с я тем, что, с целью повьппение точ10

20

25

ности вычисления результата, в устройство введены счетчик, триггер.

третий сумматор и элемент ИЛИ, причем вькод регистра делителя соединен с входом первого слагаемого третьего сумматора, выходы знакового и первого разрядов которого соединены с пер- 15 вым и вторым входами элемента ИЛИ, выход которого соединен с входами знаковых разрядов вторых сомножителей первой и третьей матриц умножения, вьрсоды i-x (где i 2,3,...п) разрядов третьего сумматора соединены с входами (i - 1)-х разрядов блока преобразования прямого кода в обратный, выход (п+1)-го разряда первого сумматора соединен со счетным входом счетчика, выход которого соединен с входом триггера, выход которого соединен с входом п-го разряда второго слагаемого третьего сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1985 |

|

SU1291973A1 |

| Устройство для деления | 1988 |

|

SU1517026A1 |

| Устройство для деления | 1989 |

|

SU1619256A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| Устройство для умножения | 1986 |

|

SU1399729A1 |

| Вычислительное устройство | 1988 |

|

SU1532917A1 |

| Устройство для деления | 1990 |

|

SU1746378A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих процессоров цифровой обработки сигналов в арифметических устройствах быстродействующих и комбинированных вычислительных машин. Целью изобретения явлется повьшение точности - вычисления результата устройства для деления, содержащего три матрицы умножения 3-5, два блока преобразования лрямого кода в дополнительный 6,7, два сумматора 8,9, блок преобразования прямого кода в обратный 13. Для достижения цели в устройство дополнительно введены третий сумматор 10, триггер 15, элемент ИЛИ 11 и счетчик 14. 1 ил. со 4 00 to

| Способ извлечения ртути из кислых растворов | 1981 |

|

SU981417A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления | 1985 |

|

SU1291973A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-06-15—Публикация

1985-11-10—Подача